# AMD's processor lines belonging to the low-power oriented Cat family (Families 14h/16h)

# Dezső Sima

# October 2018

(Ver. 1.1)

© Sima Dezső, 2018

AMD's processor lines belonging to the low-power oriented Cat family (Families 14h/16h)

- 1. Introduction to AMD's low power oriented processor lines

- 2. Family 14h Models 00h-0Fh (Bobcat-based) APU lines

- 3. Family 16h Models 00h-0Fh (Jaguar-based) APU lines

- 4. Family 16h Models 30h-3Fh (Puma+ based) APU lines

- 5. AMD's withdrawal from the mobile market

- 6. References

# 1. Introduction to AMD's low power oriented processor lines

## 1. Introduction to AMD's low power oriented processor lines (1)

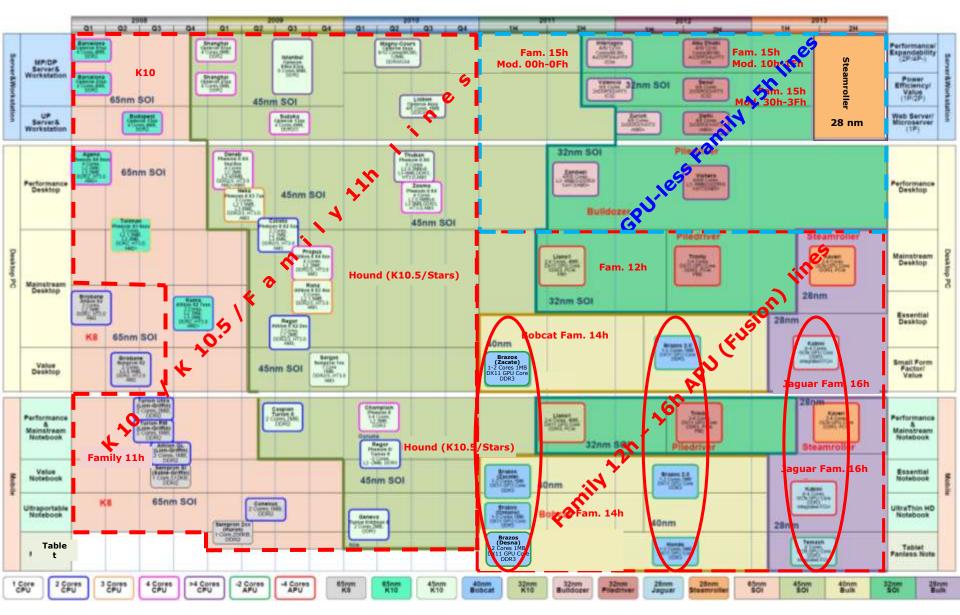

#### 1. Introduction to AMD's low power oriented processor lines AMD's move to reshape their mobile and embedded market strategy -1

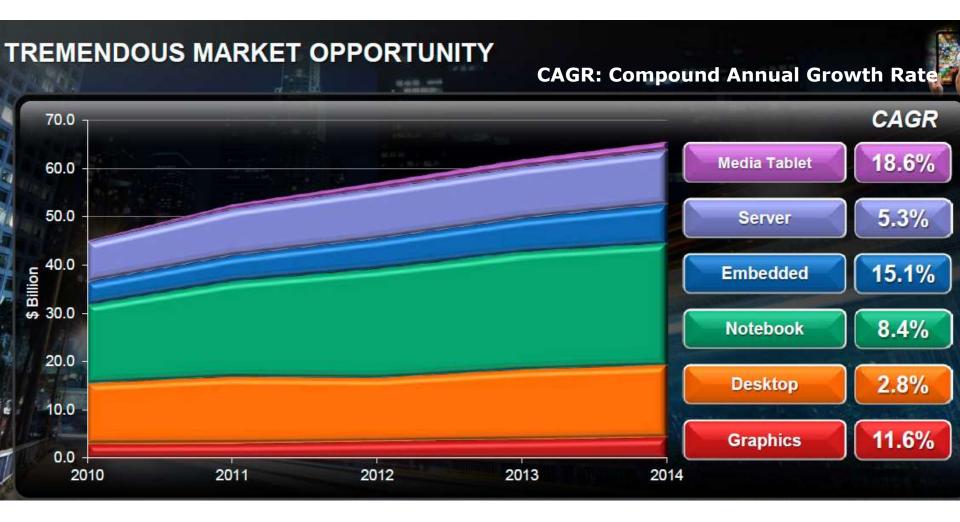

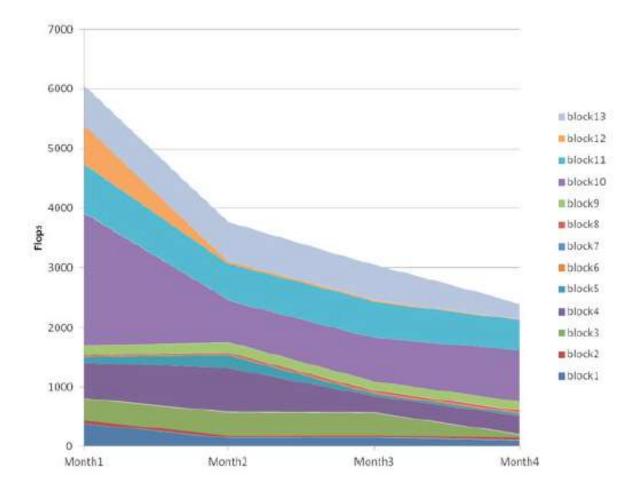

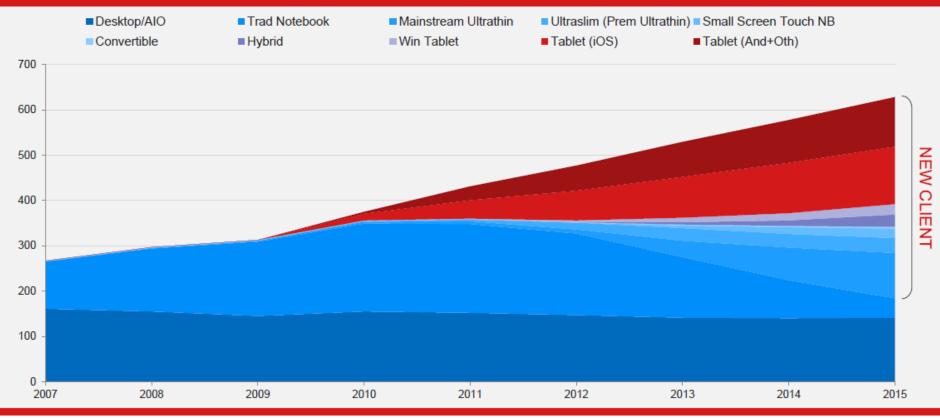

a) About 2011 AMD recognized the immensely increasing role of the mobile and embedded market segments, as demonstrated in one slide of their 2012 Financial Analyst Day presentations [1], shown below. AMD's view of worldwide turnover and growth rate of different processor segments [1]

#### AMD's move to reshape their mobile and embedded market strategy -2

- b) In 1/2011 AMD's CEO (Chief Executive Officer) and President Dirk Meyer resigned mainly due to his alleged ignorance of the netbooks, handheld and embedded market space.

- c) In 2011/2012's roadmaps and product announcements AMD put much more emphasis on mobile, laptop and embedded products, and also

- d) In 1/2012 AMD re-branded their Fusion APU concept to Heterogeneous Systems Architecture (HAS) to indicate their broader scoop of interest (broader than alone considering accelerated graphics) on the processor market.

#### Remarks

- Dirk Meyer was an outstanding processor architect, he has co-designed three very successful processors; DEC's Alpha 21064, 21264 as well as AMD's Athlon processors.

- In his role as CEO (2008-2011) he focused on the PC and data center market and intended to address the mobile and consumer electronics markets later [16].

#### AMD's revised concept for addressing the breadth of the processor market -1

Traditionally, AMD covered all market segments by the same processor design typically with two alternative implementations, including

- one full-fledged processor design that addresses the performance oriented server and desktop segments and a number of low cost, low power design for the mainstream desktop to the mobile segments, as derivatives of the full-fledged basic architecture.

- These derivative designs provide typically less resources, such as less cores, smaller L2 cache size or lack of the L3 cache, and are running at lower clock speeds.

All in all these designs provide lower power consumption at lower price and performance.

#### Example

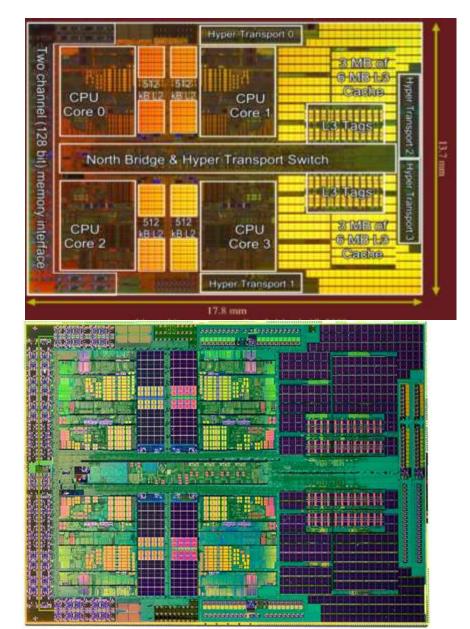

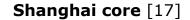

### AMD's K10.5 Shanghai based server-, desktop- and mobile lines -1

As shown below

a) the Shanghai-based high performance desktop core (Deneb) is obviously based on the original Shanghai core,

#### **Contrasting the K10.5-based Shanghai server and Deneb desktop dies**

4 C L2: 512 KB/C L3: 6 MB 258 mm<sup>2</sup>, 758 mtrs

Deneb core [18]

4 C L2: 512 KB/C L3: 6 MB 258 mm<sup>2</sup>, 758 mtrs

#### AMD's K10.5 Shanghai based server-, desktop- and mobile lines -2

b) the K10.5 Shanghai-based mainstream and value desktop cores (Propus, Regor) are L3-less derivatives of Deneb with reduced L2/Core cache size or core count.

## 1. Introduction to AMD's low power oriented processor lines (8)

[18]

[20]

#### AMD's K10.5 Shanghai based server-, desktop- and mobile lines -2

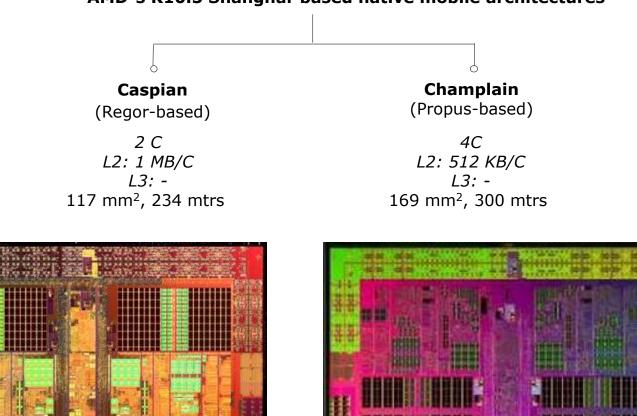

c) The K10.5 Shanghai-based mobile cores (Caspian, Champlain) are then derivatives of the mainstream and value desktop cores (Regor and Propus).

## 1. Introduction to AMD's low power oriented processor lines (10)

AMD-s K10.5 Shanghai-based native mobile architectures

[21]

\*\*\*\*\*\*

#### AMD's K10.5 Shanghai based server-, desktop- and mobile lines -2

To sum it up, despite of the wide variety of K10.5 Shanghai-based server, desktop and mobile cores, all of these designs are in fact derivatives of the basic K10.5 Shanghai core, i.e.

in their K10.5 Shanghai based cores AMD maintained in fact the same basic design.

#### AMD's revised concept for addressing the breadth of the processor market -2

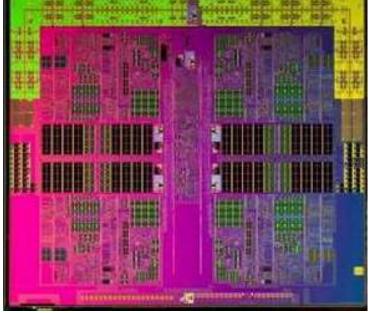

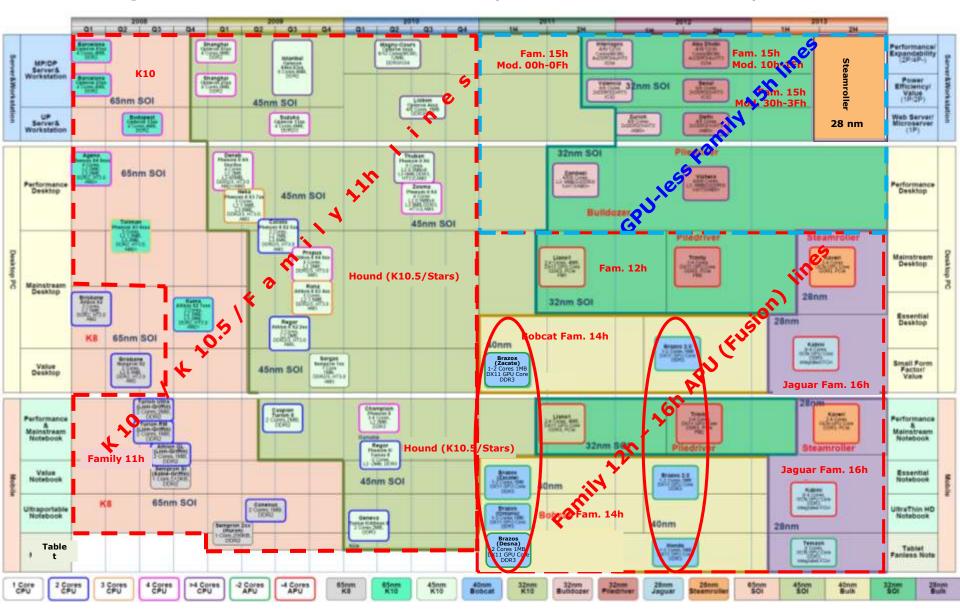

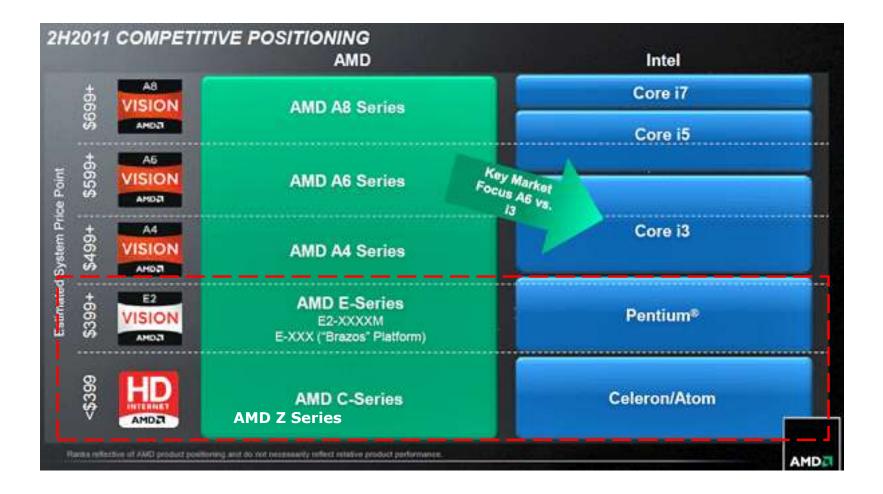

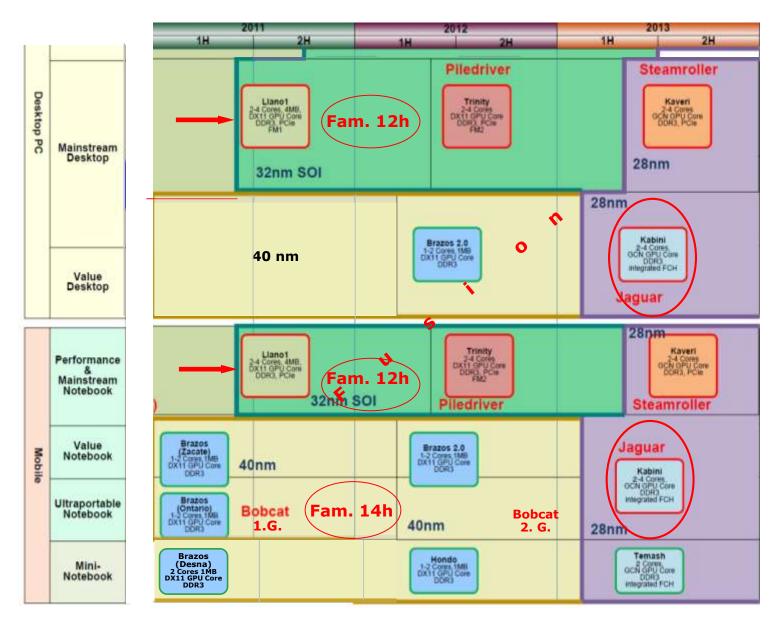

In 2011, along with the introduction of their Bobcat lines, AMD changed their design concept and opted henceforth for covering the wide processor market by two distinct processor designs rather than one in order to better optimize power and performance features of their lines [23].

According to the new concept

- the Bulldozer design focuses on the performance oriented server and desktop market, whereas

- the Bobcat design addresses the low cost, low power mobile, entry-level desktop and embedded market.

- In addition, desktop, mobile and embedded devices provide basically an integrated graphics as well.

- This is in line with AMD's visionary Fusion system architecture concept, announced after AMD's merger with ATI in 2006 that became renamed to the Heterogeneous System Architecture concept in 2012.

#### Remark

Intel made the same movement already in 2008 when they introduced their Atom line. Since then Intel pursues two major designs lines;

- their major line that focuses on performance oriented servers and desktops, whereas

- their Atom line that addresses low cost, low power mobile devices.

#### **Evolution of AMD's basic architectures**

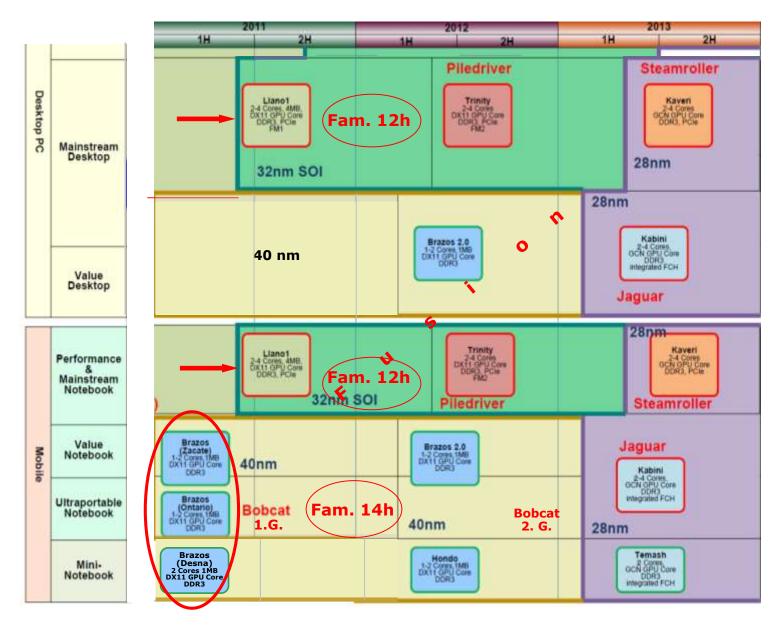

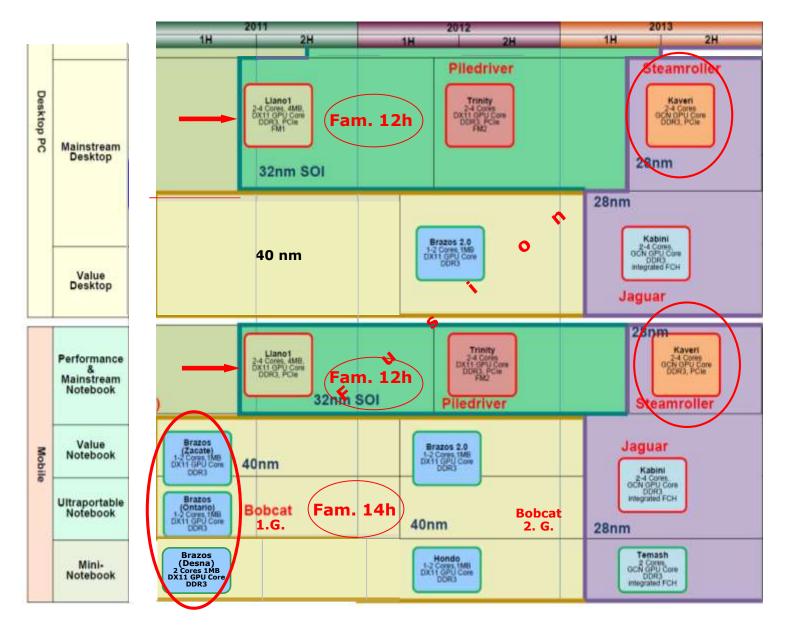

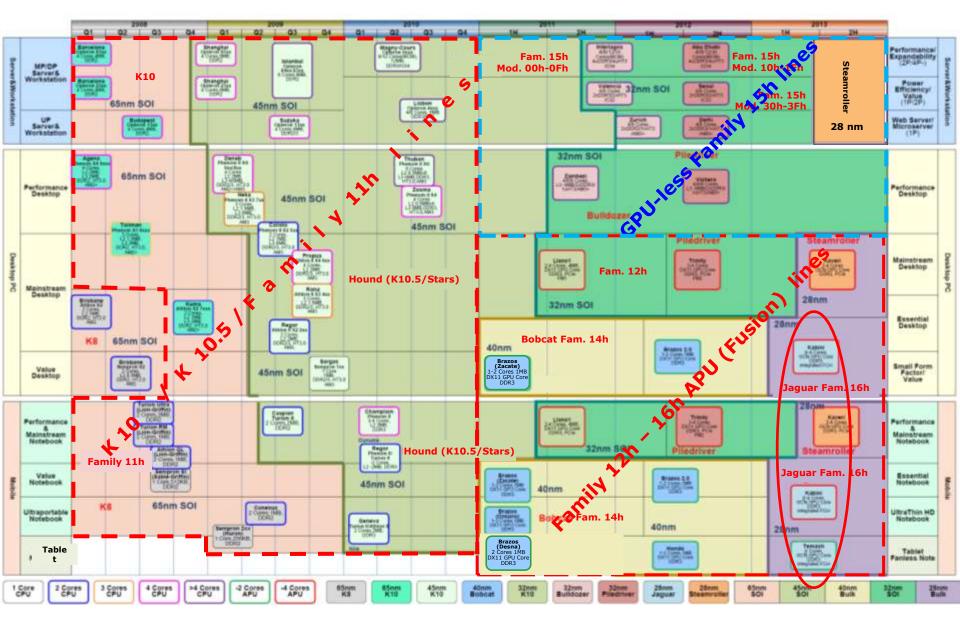

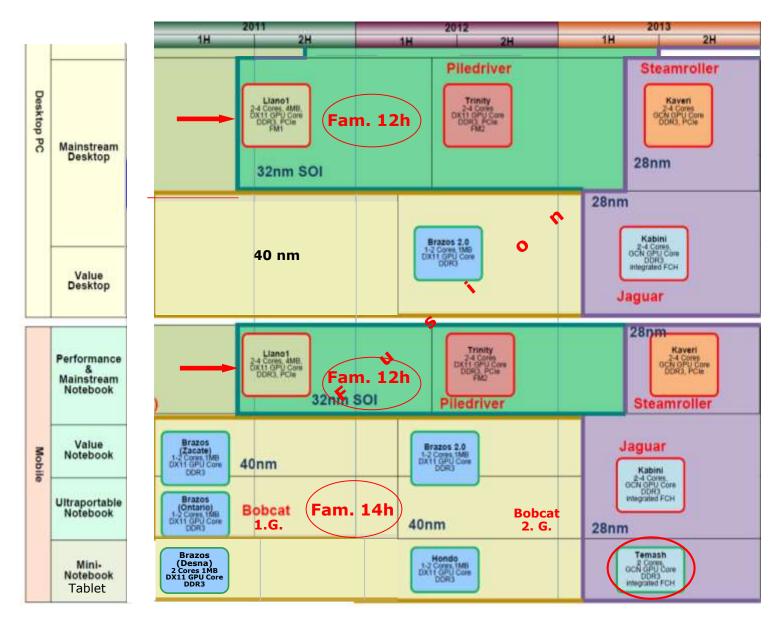

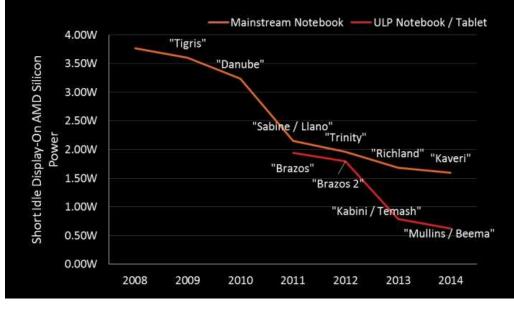

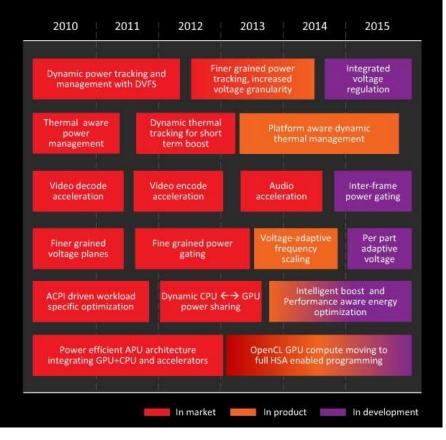

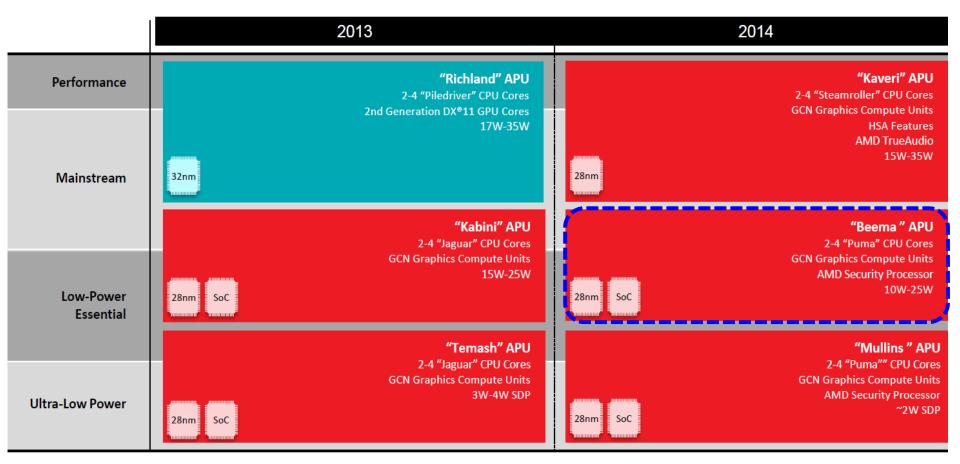

Overview of AMD's low power oriented APU lines (embedded/microserver APUs not shown) [14]

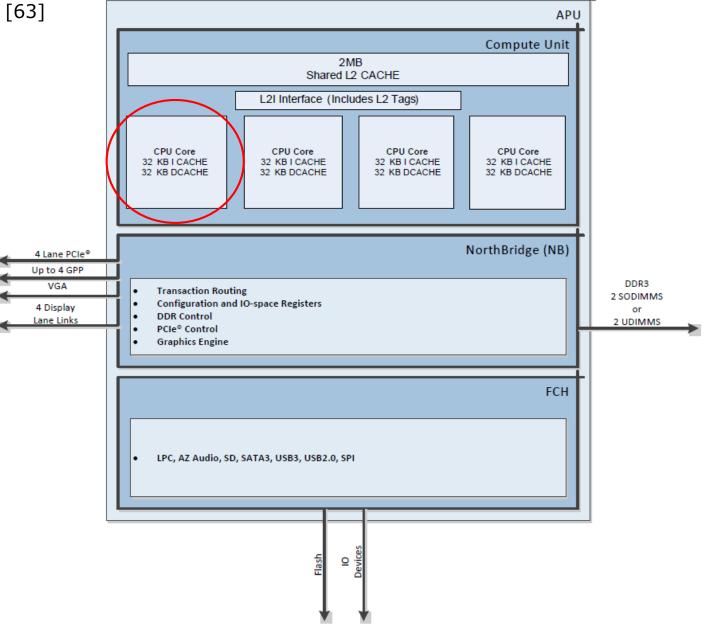

#### Brand names of AMD's Family 14h and 16h processor lines

|                         | Launched in                                         | 2011                                      | 2012                                | 2013                                | 2014                               | 2015                              |

|-------------------------|-----------------------------------------------------|-------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|-----------------------------------|

|                         |                                                     | Family 14h<br>(00h-0Fh)<br>(Bobcat)       | Family 14h<br>(00h-0Fh)<br>(Bobcat) | Family 16h<br>(00h-0Fh)<br>(Jaguar) | Family 16h<br>(30h-3Fh)<br>(Puma+) | Family 16h<br>(30h-3Fh)<br>(Puma+ |

|                         | 4P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Servers                 | 2P servers                                          |                                           |                                     |                                     |                                    |                                   |

|                         | 1P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Se                      | (85-140 W)                                          |                                           |                                     |                                     |                                    |                                   |

|                         | <b>High perf.</b><br>(~95-125 W)                    |                                           |                                     |                                     |                                    |                                   |

| Desktops                | Mainstream<br>(~65-100 W)                           |                                           |                                     |                                     |                                    |                                   |

|                         | <b>Entry level</b><br>(~30-60 W)                    |                                           |                                     |                                     |                                    |                                   |

| oks                     | High performance/<br>mainstream/entry<br>(~30-60 W) |                                           |                                     | Kabini A6                           |                                    |                                   |

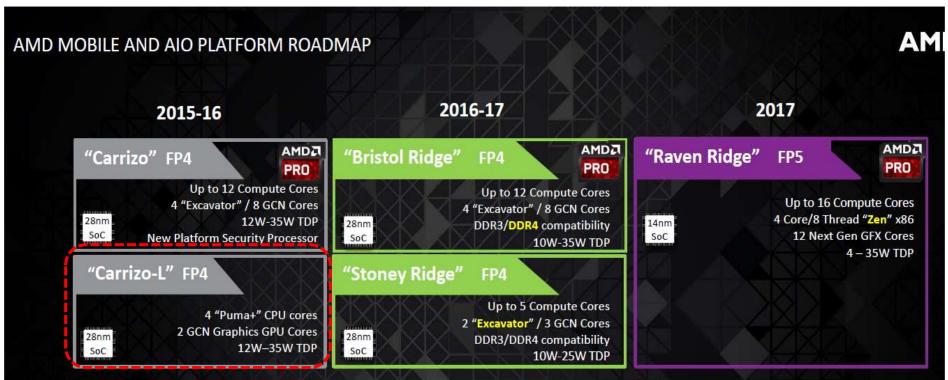

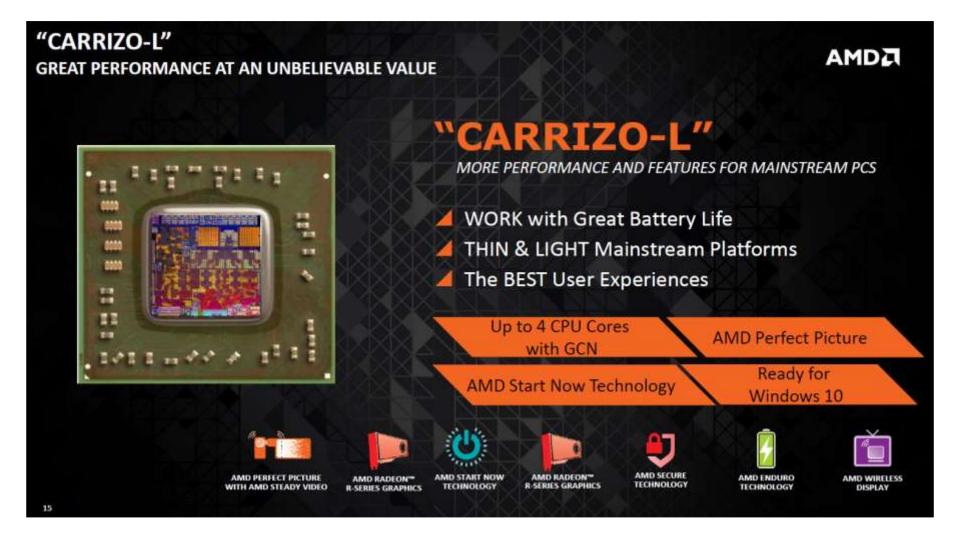

| Notebooks               | <b>Ultra portable</b><br>(~10-15 W)                 | Zacate<br>E-Series<br>Ontario<br>C-Series | Zacate<br>E1/E2                     | Kabini<br>A/E-Series                | Beema<br>A/E-Series                | Carrizo-L<br>A/L-Series           |

| <b>Tablet</b><br>(~5 W) |                                                     | Desna<br>Z-Series                         |                                     | Temash<br>A Series                  | Mullins<br>A Series/E1             |                                   |

#### Main features of AMD's Family 14h/16h (Cat-based) ultra-thin notebook processor lines

| Base arch.                                | Intro   | Ultra-thin<br>mobile<br>family | Series          | Techn. | Core count<br>(up to)                                  | L2<br>(up to)              | L3            | GPU<br>(APU) | Memory<br>(up to) | TDP<br>[W] | Socke<br>t   |

|-------------------------------------------|---------|--------------------------------|-----------------|--------|--------------------------------------------------------|----------------------------|---------------|--------------|-------------------|------------|--------------|

|                                           | 1/2011  | Zacate<br>(not SoC)            | E<br>Series     | 40 nm  | 2                                                      | 512 KB/<br>core<br>Private | -             | Yes          | DDR3L-<br>1333    | 18         | FT1<br>(BGA) |

| <b>Family14h</b><br>(00h-0Fh)<br>(Bobcat) | 6/2012  | Zacate<br>(not SoC)            | E1/E2<br>Models | 40 nm  | 2                                                      | 512 KB/<br>core<br>Private | -             | Yes          | DDR3L-<br>1333    | 18         | FT1<br>(BGA) |

|                                           | 1/2011  | Ontario                        | C<br>Series     | 40 nm  | 2                                                      | 512 KB/<br>core<br>private | -             | Yes          | DDR3-<br>1066     | 9          | FT1<br>(BGA) |

| Family 16h<br>(10H-1fH)<br>(Jaguar)       | 5/2013  | Kabini<br>(SoC)                | A<br>Series     | 28 nm  |                                                        | 2 MB<br>shared             | -             | Yes          | DDR3L-<br>1866    | 15         | FT3          |

| Family 16h                                | 4/2014  | Beema<br>(SoC)                 | A<br>Series     | 28 nm  | 4 cores<br>with a<br>shared L2<br>cache                | 2 MB<br>shared             | -             | Yes          | DDR3L-<br>1866    | 15         | FT3b         |

| (30H-3fH)<br>(Puma+)                      | 5/2015  | Carrizo-L<br>(SoC)             | A<br>Series     | 28 nm  |                                                        | 2 MB<br>shared             | -             | Yes          | DDR3L-<br>1866    | 10/<br>15  | FP4          |

| Family 17h<br>(00H-0fH)<br>(Zen)          | 10/2017 | Raven<br>Ridge<br>(SoC)        | Ryzen<br>7/5/3  | 14 nm  | 4-core CCX,<br>private L2<br>and shared<br>L3 cache(s) | ½ MB/<br>core              | 1 MB/<br>core | Yes          | DDR4-<br>2400     | 15         | AM4          |

APU: Accelerated Processing Unit (CPU +GPU) CCX: Core CompleX

<sup>2</sup>: 2\*512 KB for Turion X2, 2\*1 MB for Turion X2 Ultra

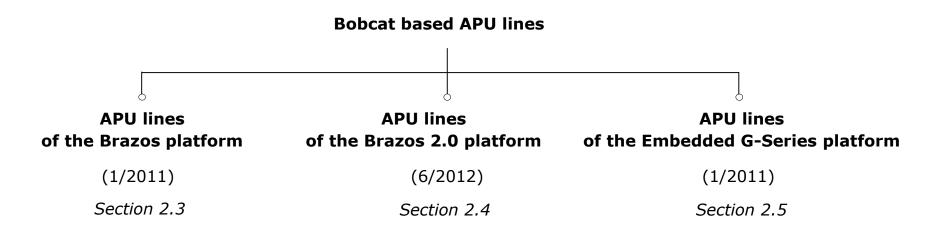

# 2. Family 14h Models 00h-0Fh (Bobcat-based) APU lines

- 2.1 Overview of the Bobcat-based APU lines

- 2.2 The Bobcat core

- 2.3 APU-lines of the Brazos platform

- 2.4 APU lines of the Brazos 2.0 platform

- 2.5 APU lines of the Embedded G-Series platform

# 2.1 Overview of the Bobcat-based APU lines

#### 2.1 Overview of the Bobcat-based APU lines

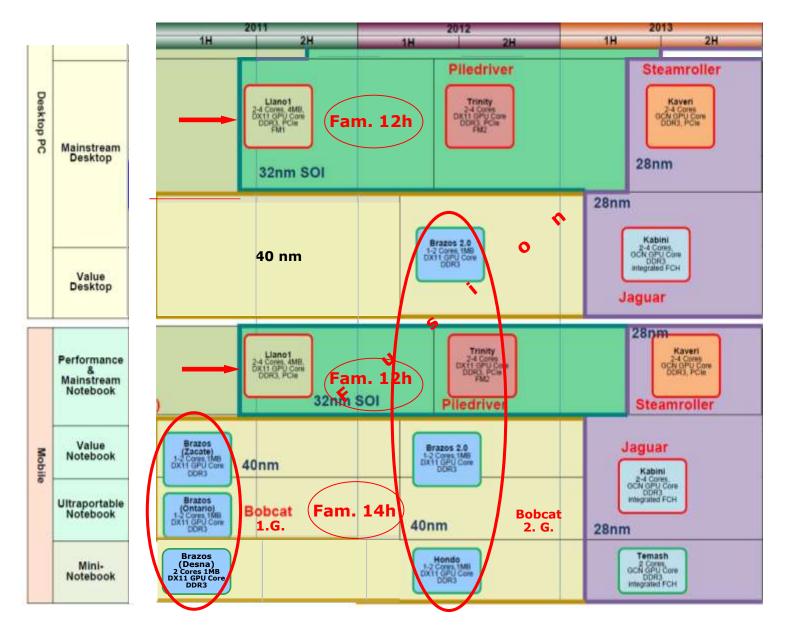

• Bobcat-based APUs are AMD's first products with the Fusion brand name, that were introduced at the Consumer Electronics Show (CES) in 1/2011.

They are the basic parts of the Brazos platform that focuses on the mobile market, but includes desktop models as well.

- The Brazos platform became one of AMD's most successful products that is typically used in ultra-light notebooks and tablets [24], [25].

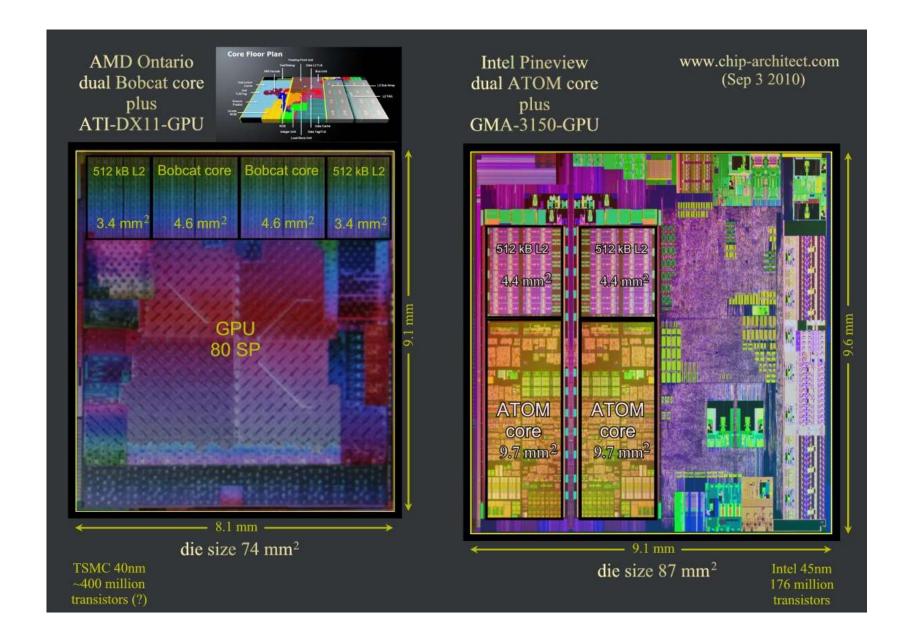

- Bobcat-based APUs compete with Intel's Atom processors.

- They mark AMD's new market strategy that positively repositions the mobile and desktop market segments in AMD's overall market policy.

- Bobcat based Fusion products include basically up to two Bobcat cores and a GPU with similar capabilities than a low-end discrete graphics card.

- 40 nm technology, 75 mm<sup>2</sup>, 450 mtrs.

#### Remark [26]

Bobcat based Brazos systems was a turning point for AMD.

The firm sold until the launch of the Jaguar-based 28 nm mobile products (Temash, Kabini) nearly 50 million Brazos systems.

Jaguar-based systems improve both IPC (about 20 %) and power consumption (also about 20 %) vs. the previous products.

According to industry sources [27] these low power systems seems to be AMD's last hope to avoid bankruptcy and remain alive.

#### **Overview of the Bobcat-based APU lines**

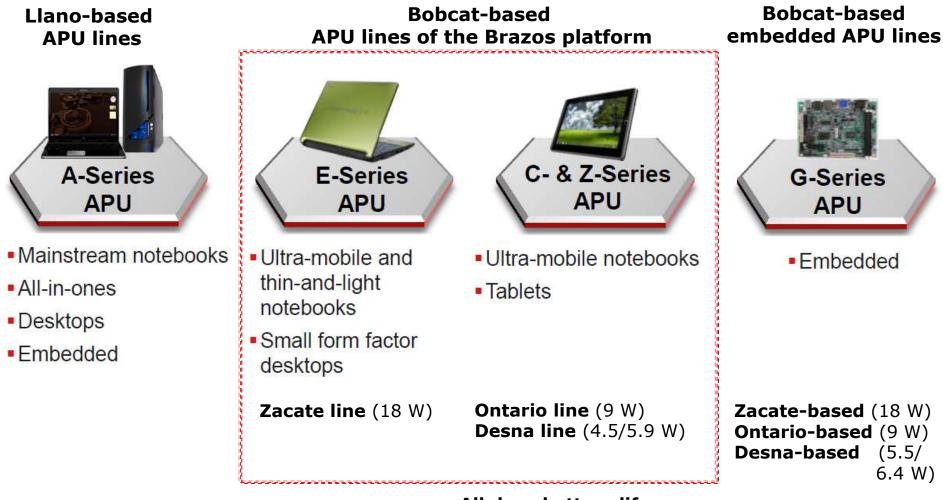

Positioning of the Bobcat-based APU lines-1 (embedded lines not shown) [based on 14]

Positioning of the Bobcat-based APU lines-2 (embedded lines not shown) [14]

#### **Brand names of Bobcat-based processor lines**

|                         | Launched in                                         | 2011                                      | 2012                                | 2013                                | 2014                               | 2015                              |

|-------------------------|-----------------------------------------------------|-------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|-----------------------------------|

|                         |                                                     | Family 14h<br>(00h-0Fh)<br>(Bobcat)       | Family 14h<br>(00h-0Fh)<br>(Bobcat) | Family 16h<br>(00h-0Fh)<br>(Jaguar) | Family 16h<br>(30h-3Fh)<br>(Puma+) | Family 16h<br>(30h-3Fh)<br>(Puma+ |

|                         | 4P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Servers                 | 2P servers                                          |                                           |                                     |                                     |                                    |                                   |

|                         | 1P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Se                      | (85-140 W)                                          |                                           |                                     |                                     |                                    |                                   |

|                         | High perf.<br>(~95-125 W)                           |                                           |                                     |                                     |                                    |                                   |

| Desktops                | <b>Mainstream</b><br>(~65-100 W)                    |                                           |                                     |                                     |                                    |                                   |

|                         | <b>Entry level</b><br>(~30-60 W)                    |                                           |                                     |                                     |                                    |                                   |

| oks                     | High performance/<br>mainstream/entry<br>(~30-60 W) |                                           |                                     | Kabini A6                           |                                    |                                   |

| Notebooks               | <b>Ultra portable</b><br>(~10-15 W)                 | Zacate<br>E-Series<br>Ontario<br>C-Series | Zacate<br>E1/E2                     | Kabini<br>A/E-Series                | Beema<br>A/E-Series                | Carrizo-L<br>A/L-Series           |

| <b>Tablet</b><br>(~5 W) |                                                     | Desna<br>Z-Series                         |                                     | Temash<br>A Series                  | Mullins<br>A Series/E1             |                                   |

# 2.2 The Bobcat core

- 2.2.1 The microarchitecture of the Bobcat core

- 2.2.2 Main features of the Bobcat core

# 2.2.1 The microarchitecture of the Bobcat core

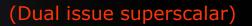

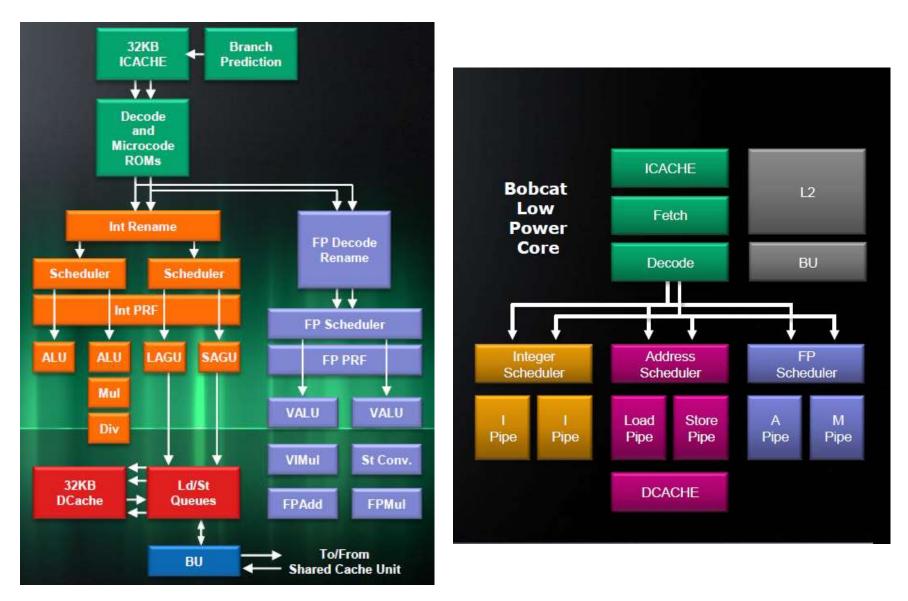

#### 2.2.1 The microarchitecture of the Bobcat core

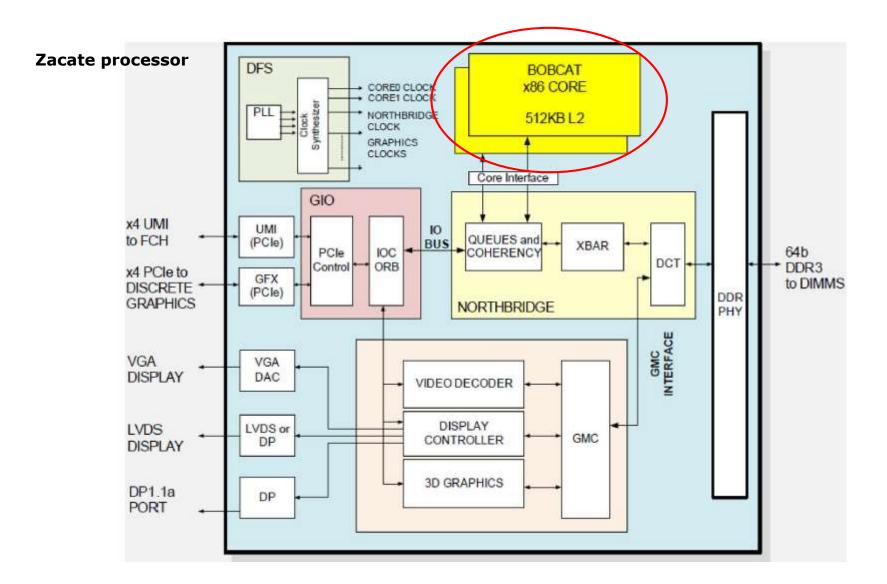

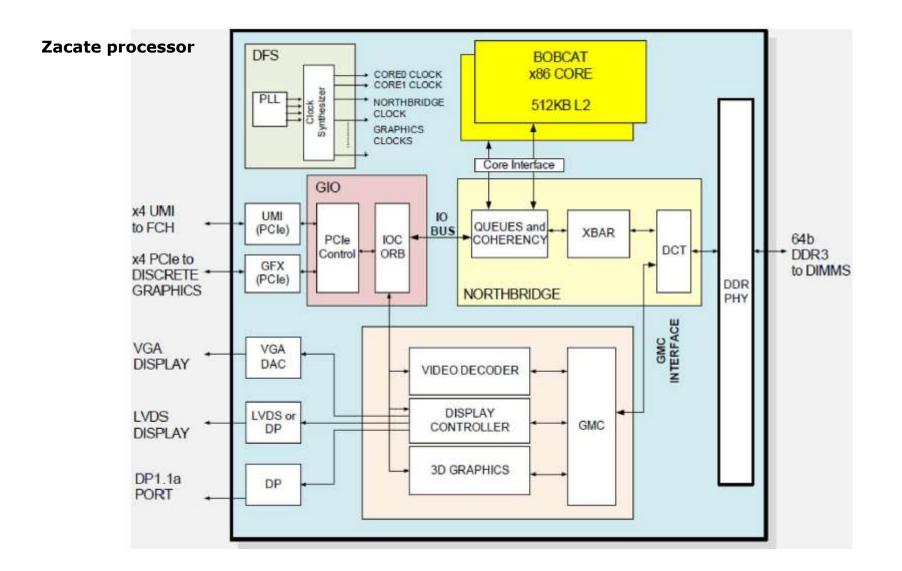

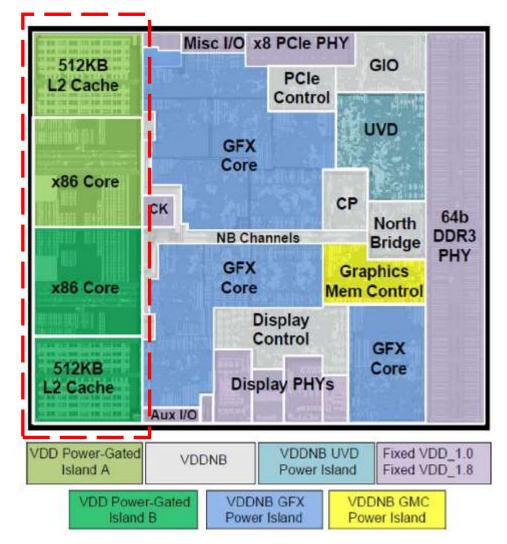

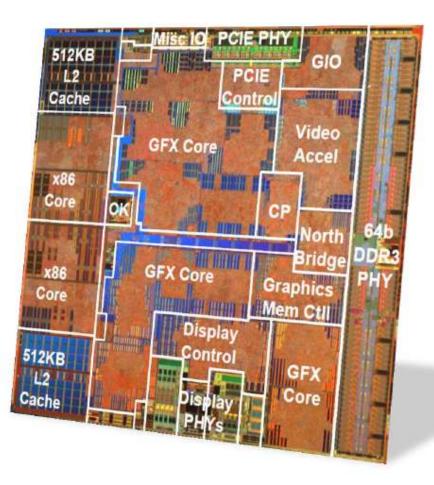

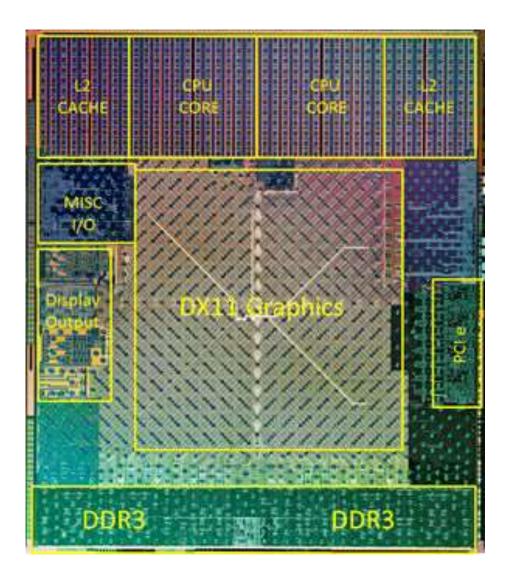

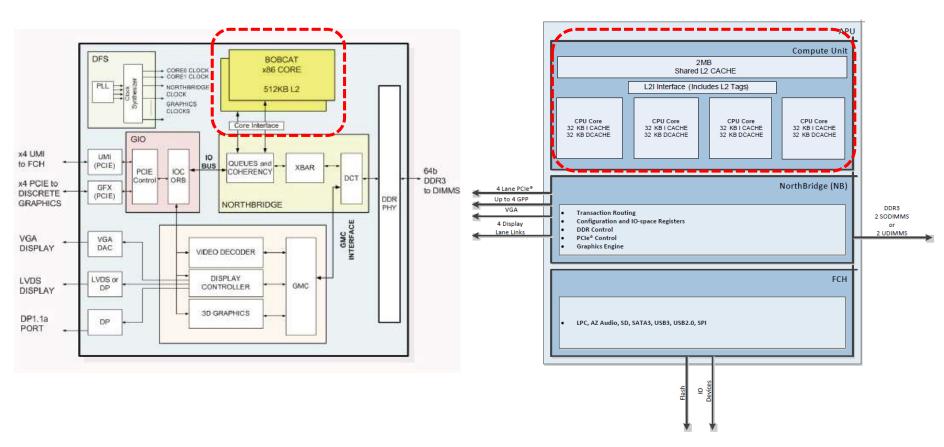

The Bobcat core is the x86 "engine" of Bobcat-based APUs, as indicated in the next example.

#### **Example: Use of dual Bobcat cores in the Zacate processor** [28]

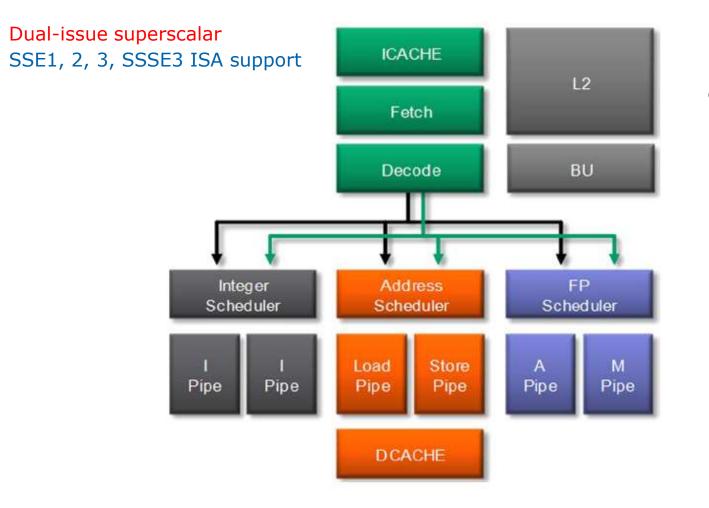

#### Rough block diagram of the microarchitecture of the Bobcat core [28]

512 KB/core ECC protected L2, clocked at ½ clock rate to reduce power

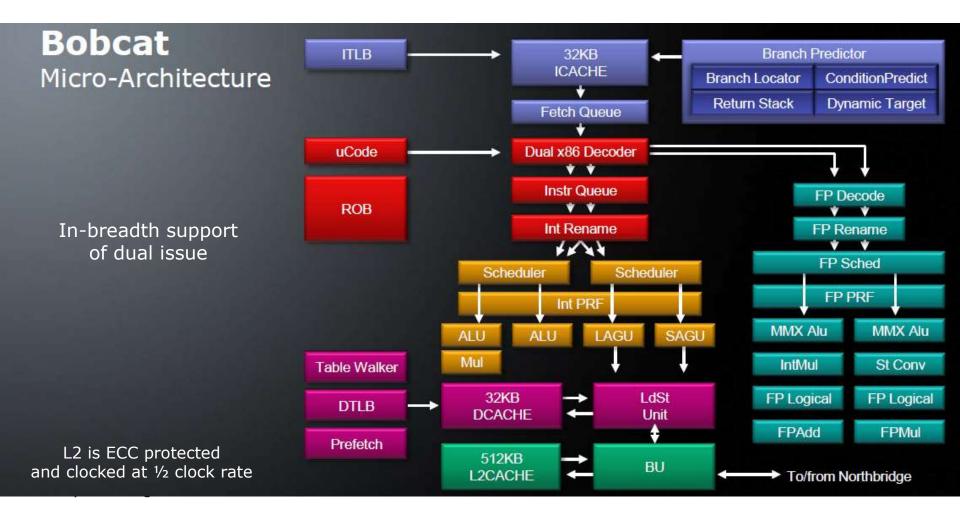

#### More detailed block diagram of the microarchitecture of the Bobcat core [8]

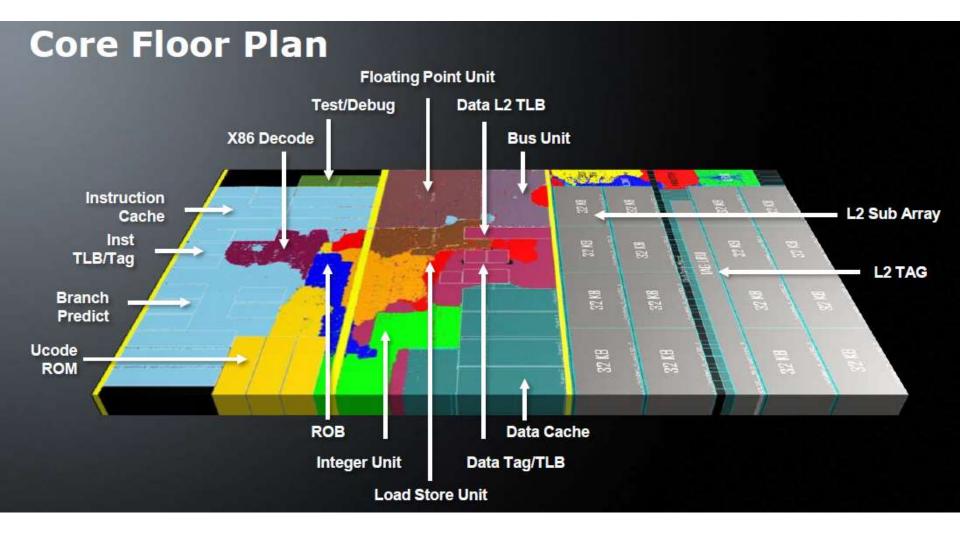

#### **Bobcat's floorplan** [8]

#### **Example: Block diagram of the Zacate APU** [28]

**Example: Floorplan and power domains of the Zacate die that includes 2 Bobcat cores**[28]

#### Use of the Bobcat CPU core in AMD's Family 14h-based mobile and embedded lines

- All the Bobcat based Zacate, Ontario and Desna mobile and G-series Fusion APUs have the same common design that includes basically two Bobcat CPU cores and a GPU, as detailed in Sections 4.xx and in Sections 4.xx and 4.xx.

- Nevertheless, in different models AMD disables a CPU or the GPU core or both and includes different GPU cores, as indicated next.

#### Use of different GPU cores in Bobcat-based Ontario, Zacate and Desna mobile models [29]

#### "Zacate" (40 nm)

|         |         |       |          |       |            |                    |                   |         | 1                   |         |         |           |      |              |

|---------|---------|-------|----------|-------|------------|--------------------|-------------------|---------|---------------------|---------|---------|-----------|------|--------------|

|         | C       |       |          |       | CPU        |                    |                   |         | G                   | PU      |         |           | TOD  | Dalasad      |

| Model   | Step.   | Cores | Freq.    | Turbo | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo   | Memory    | TDP  | Released     |

| E-240 🗗 | B0      | 1     | 1.5 GHz  |       | 512 KB     | 15×                | 1.175 - 1.35      |         |                     | 500 MHz |         | DDR3-1066 |      | Jan 4, 2011  |

| E-300   | B0      |       | 1.3 GHz  |       |            | 13×                |                   | HD 6310 | 80:8:4              | 488 MHz | N/A     | DDR3-1333 |      | Aug 22, 2011 |

| E-350 🗗 | B0      |       | 1.6 GHz  | N/A   |            | 16×                | 1.25 - 1.35       |         |                     | 492 MHz |         | DDR3-1066 |      | Jan 4, 2011  |

| E-450   | C0      | 2     | 1.65 GHz |       | 2 × 512 KB | 16.5×              |                   | HD 6320 | 80:8:4              | 508 MHz | 600 MHz | DDR3-1333 | 18 W | Aug 22, 2011 |

| E1-1200 |         |       | 1.4 GHz  | ]     |            | 14×                |                   | HD 7310 | 80:8:4              | 500 MHz | N/A     | DDR3-1066 | ]    | 04.0040      |

| E2-1800 |         |       | 1.7 GHz  | 1     |            | 17×                |                   | HD 7340 | 80:8:4              | 523 MHz | 680 MHz | DDR3-1333 | 1    | Q1 2012      |

|         |         |       |          |       |            |                    | ,                 |         |                     |         |         | ,         |      |              |

| Ontario | " (40 r | ım)   |          |       |            |                    |                   |         |                     |         |         |           |      |              |

|         |         |       |          |       |            |                    |                   |         |                     |         |         |           |      |              |

#### "Ontario" (40 nm)

| Madal  | Ctore |       |         |          | CPU        |                    |                   |         | G                   | PU      |         |           | TOD | Deleased     |

|--------|-------|-------|---------|----------|------------|--------------------|-------------------|---------|---------------------|---------|---------|-----------|-----|--------------|

| Model  | step. | Cores | Freq.   | Turbo    | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo   | Memory    | TDP | Released     |

| C-30 🗗 | DA    | 1     | 1.2 GHz | N/A      | 512 KB     | 12×                | 1.25 - 1.35       |         | 00.0.4              | 070 MUL | N/A     |           |     | lan ( 0011   |

| C-50 🗗 | B0    | 2     | 1.0.01- | N/A      | 2 542 KB   | 10×                | 1.05 - 1.35       | HD 6250 | 00:0:4              | 276 MHz | N/A     | DDR3-1066 | 9 W | Jan 4, 2011  |

| C-60   | C0    | 2     | 1.0 GHz | 1.33 GHz | 2 × 512 KB | 10-13.3×           |                   | HD 6290 | 80:8:4              | 276 MHz | 400 MHz |           |     | Aug 22, 2011 |

#### "Desna" (40nm)

| Madal  | Cton  |       |         | C     | :PU        |                    |                   |         | GP                  | U       |       | Mamanu    | TOD   | Delegend     |

|--------|-------|-------|---------|-------|------------|--------------------|-------------------|---------|---------------------|---------|-------|-----------|-------|--------------|

| Model  | step. | Cores | Freq.   | Turbo | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo | Memory    | TDP   | Released     |

| Z-01 🗗 | B0    | 2     | 1.0.04- | N/A   | 2 × 512 KB | 10×                |                   |         | 00.0.4              | 076 MU- | N/A   | DDD2 1000 | 5.9 W | June 1, 2011 |

| Z-03   |       | 2     | 1.0 GHz | N/A   | 2 × 512 KD | 10×                |                   | HD 6250 | 00:0:4              | 276 MHz | N/A   | DDR3-1066 | 4.5 W | Q1 2012      |

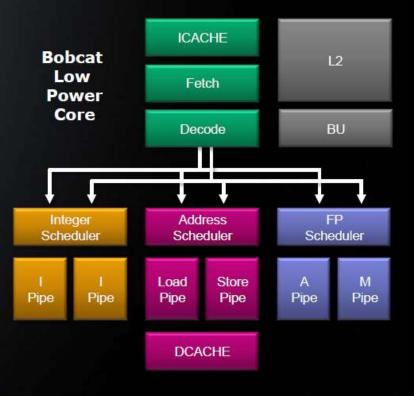

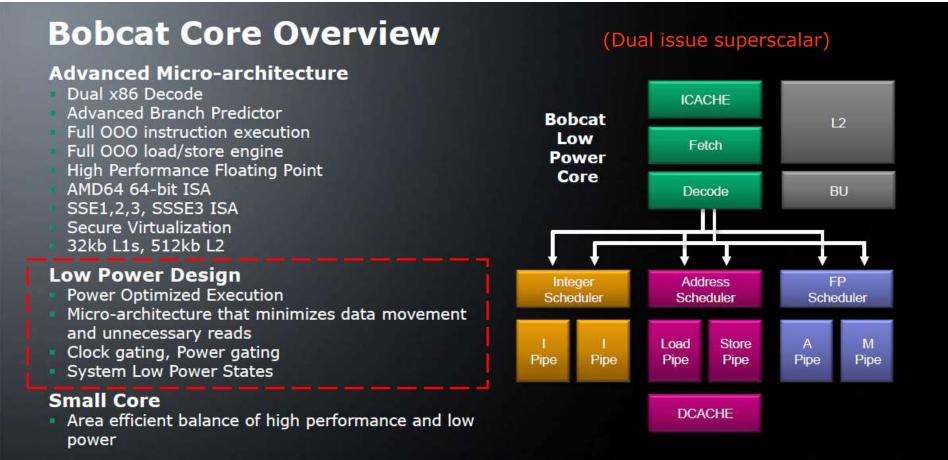

# 2.2.2 Main features of the Bobcat core

2.2.2 Main features of the Bobcat CPU core-1 [8]

2.2.2.1 Main features of the Bobcat core affecting the performance or security

# **Bobcat Core Overview**

#### Advanced Micro-architecture

- Dual x86 Decode

- Advanced Branch Predictor

- Full OOO instruction execution

- Full OOO load/store engine

- High Performance Floating Point

- AMD64 64-bit ISA

- SSE1,2,3, SSSE3 ISA

- Secure Virtualization

- 32kb L1s, 512kb L2

#### Low Power Design

- Power Optimized Execution

- Micro-architecture that minimizes data movement and unnecessary reads

- Clock gating, Power gating

- System Low Power States

#### Small Core

Area efficient balance of high performance and low power

#### The Turbo Core technology in Bobcat cores

- First Bobcat based models were Stepping B0 devices, they were introduced in 1/2011, they did not provide the Turbo Core technology.

- Turbo Core technology appeared along with select dual core Stepping C0 mobile devices that appeared in 8/2011, such as

- the E450 (Zacate) model that supports Turbo Core for the GPU and

- the C60 (Ontario) model that supports Turbo Core for both the CPU and the GPU cores [29].

There is no available publication to date that gives details of how Turbo Core is implemented in Bobcat-based processors, nevertheless, it can be assumed that Turbo Core is implemented in these processors in the same way as in the Llano processors, i.e. based on a digital power monitor circuitry, described in [30].

#### Supporting the Turbo Core mode in different Bobcat-based mobile models [29]

#### "Zacate" (40 nm)

| Madel   | Char     |       |          |       | CPU        |                    |                   |         | G                   | PU      |         |           | тор   | Delegend     |

|---------|----------|-------|----------|-------|------------|--------------------|-------------------|---------|---------------------|---------|---------|-----------|-------|--------------|

| Model   | step.    | Cores | Frec.    | Turbo | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo   | Memory    | TDP   | Released     |

| E-240 🗗 | B0       | 1     | 1.5 GHz  |       | 512 KB     | 15×                | 1.175 - 1.35      |         |                     | 500 MHz |         | DDR3-1066 |       | Jan 4, 2011  |

| E-300   | B0       |       | 1.3 GHz  |       |            | 13×                |                   | HD 6310 | 80:8:4              | 488 MHz | N/A     | DDR3-1333 |       | Aug 22, 2011 |

| E-350 🗗 | B0       |       | 1.6 GHz  | N/A   |            | 16×                | 1.25 - 1.35       |         |                     | 492 MHz |         | DDR3-1066 | 10.14 | Jan 4, 2011  |

| E-450   | C0       | 2     | 1.65 GHz |       | 2 × 512 KB | 16.5×              |                   | HD 6320 | 80:8:4              | 508 MHz | 600 MHz | DDR3-1333 | 18 W  | Aug 22, 2011 |

| E1-1200 |          |       | 1.4 GHz  |       |            | 14×                |                   | HD 7310 | 80:8:4              | 500 MHz | N/A     | DDR3-1066 |       | 01 0010      |

| E2-1800 |          |       | 1.7 GHz  |       |            | 17×                |                   | HD 7340 | 80:8:4              | 523 MHz | 680 MHz | DDR3-1333 |       | Q1 2012      |

| Ontario | '' (40 n | im)   |          |       |            |                    | ·                 |         | <u>.</u>            |         |         |           | *     | ·            |

# "*Ontario*" (40 nm)

| Madal  | Ctore |          |         |          | CPU        |                    |                   |         | G                   | PU        |         |           | тор | Delessed     |

|--------|-------|----------|---------|----------|------------|--------------------|-------------------|---------|---------------------|-----------|---------|-----------|-----|--------------|

| Model  | step. | Cores    | Freq.   | Turbo    | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.     | Turbo   | Memory    | TDP | Released     |

| C-30 🗗 | BO    | 1        | 1.2 GHz | N/A      | 512 KB     | 12×                | 1.25 - 1.35       | HD 6250 | 80:8:4              | 276 MHz   | N/A     |           |     | len 4, 2011  |

| C-50 🗗 | B0    | 2        | 1.0 GHz |          | 2 × 512 KB | 10×                | 1.05 - 1.35       | HD 0200 | 00.0.4              | 270 10112 | N/A     | DDR3-1066 | 9 W | Jan 4, 2011  |

| C-60   | C0    | 2        | 1.0 GHZ | 1.33 GHz |            | 10-13.3×           |                   | HD 6290 | 80:8:4              | 276 MHz   | 400 MHz |           |     | Aug 22, 2011 |

|        |       |          |         |          |            |                    |                   |         |                     |           |         |           |     |              |

|        | "De   | sna'' (4 | 40nm)   |          |            |                    |                   |         |                     |           |         | -         |     |              |

#### "Desna" (40nm)

| Model         Step.         CPU         GPU         Memory         TDP         Ref           Cores         Freq.         Turbo         L2 Cache         Multi <sup>1</sup> V <sub>core</sub> Model         Config <sup>2</sup> Freq.         Turbo         TDP         Ref | Released  |          |          |       |      |         |                     |         |                   |                    |            |       |         |       |       |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|----------|-------|------|---------|---------------------|---------|-------------------|--------------------|------------|-------|---------|-------|-------|--------|

| Cores Freq. Turbo L2 Cache Multi <sup>1</sup> V <sub>core</sub> Model Config <sup>2</sup> Freq. Turbo                                                                                                                                                                      |           |          |          |       |      | บ       | GP                  |         |                   |                    | PU         | C     |         |       | Cton  | Madal  |

|                                                                                                                                                                                                                                                                            | Released  | IDP R    | nemory   | urbo  | . Tu | Freq.   | Config <sup>2</sup> | Model   | V <sub>core</sub> | Multi <sup>1</sup> | L2 Cache   | Turbo | Freq.   | Cores | step. | woder  |

| Z-01 @ B0 2 1.0 GHz N/A 2 × 512 KB 10× HD 6250 80:8:4 276 MHz N/A DDR3-1066 5.9 W Jun                                                                                                                                                                                      | une 1, 20 | 5.9 W Ju | 002 1000 | N/A D |      | 076 MU- | 00.0.4              |         |                   | 10                 | 0 510 KB   | NZA   | 1.0.00- | 2     | B0    | Z-01 🗗 |

|                                                                                                                                                                                                                                                                            | Q1 2012   |          |          | NVA D |      |         | 00:0:4              | HD 6250 |                   | 10×                | 2 × 512 KD | N/A   | 1.0 GHZ | 2     |       | Z-03   |

### 2.2.2.2 Main features of the Bobcat core affecting the power consumption [8]

### 1) Power optimized microarchitecture [31]

### • Introducing physical register files instead of future files for register renaming

- While using physical register files for register renaming the physical register files keep both the architectural state and the result values of the execution that are waiting for writing back into the architectural registers in sequential order.

- Such an implementation replaces data movements with pointer updates that results in power saving.

### Pointer based implementation of queues

This minimizes data movements versus traditional implementations of queues where data will be shifted for adding or removing data.

#### Remark

For an overview of register renaming see e.g. [62].

2) Using effective power saving techniques related to clocking and powering the processor

Bobcat cores utilize

- Clock gating

- Power gating as well as

- Core CC6 and package PC6 states,

- i.e. low power techniques used also in Llano or Bulldozer cores, and described in the related Section discussing the Llano lines.

Remarks

- 1) Data size-based clock gating is widely used in Bobcat cores for less than 64-bit operations, for this reason e.g. the upper and lower halves of all result buses and forwarding logic are clocked independently to allow clock gating of not needed circuitry [31].

- 2) Power gating is implemented differently in the Bobcat and Llano cores and Bulldozer modules. Whereas in the Llano cores and Bulldozer modules AMD power isolates VSS (ground), in the Bobcat cores VDD will be isolated as shown next [28].

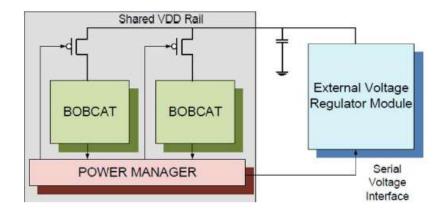

#### **Power gating the Bobcat cores** [28]

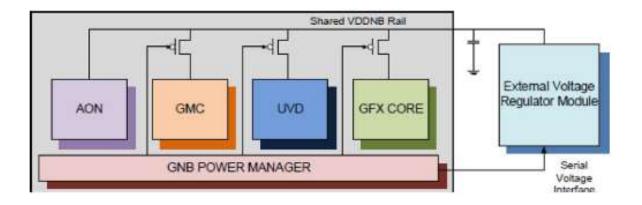

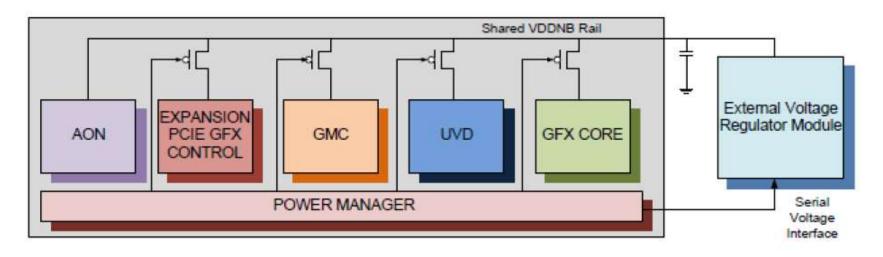

#### **Power gating the NBB units** [28]

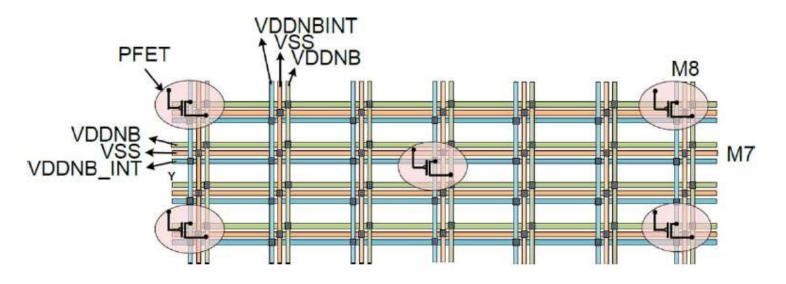

GFX: Graphics CoreGMC: Graphics Memory Control (if memory is in self-refresh)UVD: Unified Video Decoder Power gating of VDDNB in Zacate's VDDNB power grid implementation [28]

VDDNB: Supply voltage of the North Bridge VDDNB\_INT: Power gated supply voltage of the North Bridge VSS: Ground

M7, M8: Metal layers

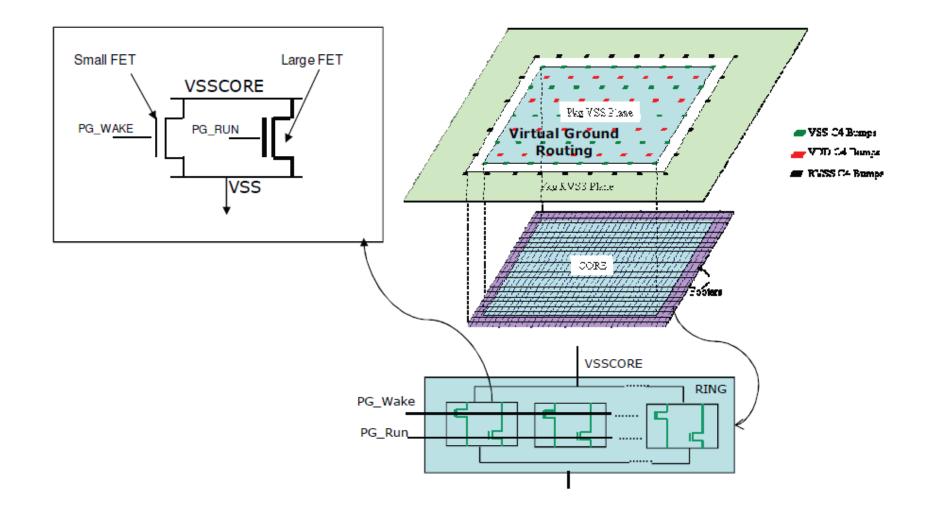

### **Power gating of VSS in AMD's Llano cores** [32]

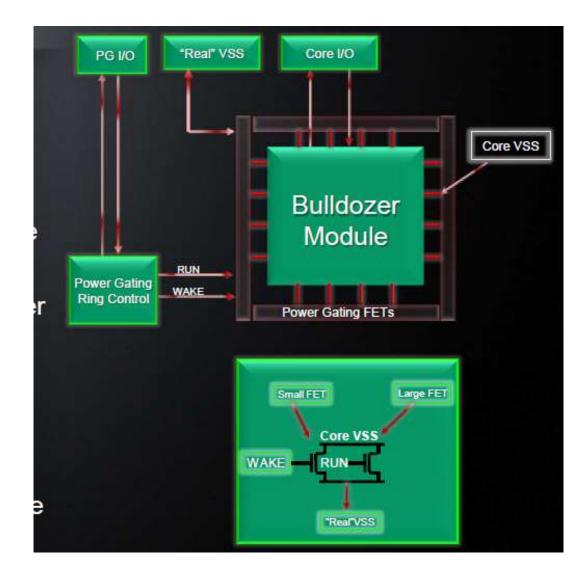

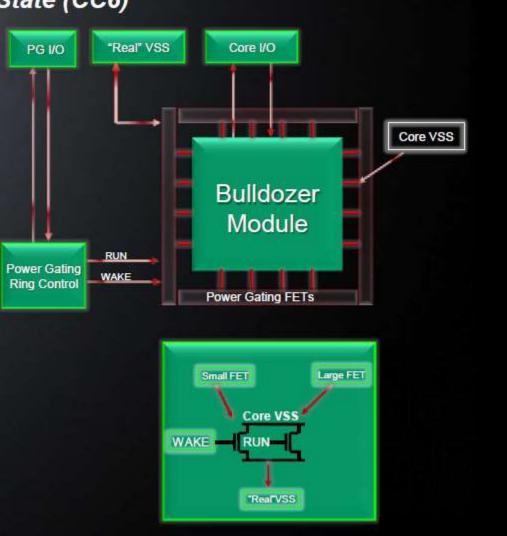

## **Power gating of VSS in AMD's Bulldozer modules** [33]

### Remark

Nevertheless, in Llano's NB AMD seems to power-gate VDDNB rather than VSS [34]

- With GFX: Graphics Core

- GMC: Graphics Memory Control (when memory is in self-refresh)

- UVD: Unified Video Decoder

- PCIE GFX CONTROL: the x16 PCIe Graphics Expansion Controller

- AON: Always on (not power gated circuitry)

The GFX and GMC units are dynamically (hardware controlled) power gated whereas power gating of the other units is static, i.e. done under software (driver) control.

### **Implementation of the Core C6 state with power gating in a Bulldozer module** [33]

## POWER MANAGEMENT | Core C6 State (CC6)

- Core C6: if a core isn't active, remove power

- Implemented in this physical design by a power gating ring that isolates the Core VSS for each Bulldozer module from the "Real" VSS

- CC6 entry: when both Bulldozer cores in the module are idle, flush caches and dump register state to CC6 save space, then gate Core VSS

CC6 exit: ungate Core VSS, reload CC6 saved state, resume execution (ex: service interrupts, etc.)

## 2.2.2 Main features of the Bobcat core (13)

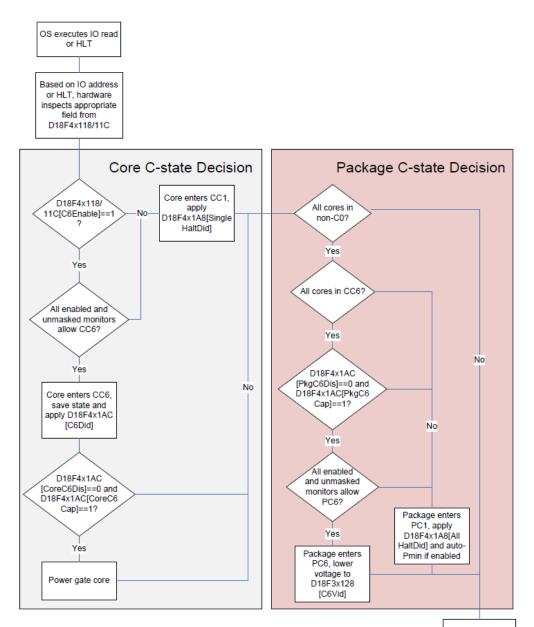

#### The Core C6 state (CC6 state)/Package C6 state (PC6 state) (simplified) [35]

#### Entering the CC6 state

- 1. OS requests entering into the CC6 state by issuing a specific I/O read or HLT instruction.

- 2. The processor enters the CC6 state if associated monitors allow this.

#### The process of entering the CC6 state

- 1. L1 and L2 caches are flushed to DRAM by hardware.

- 2. Internal core state is saved to DRAM by hardware.

- 3. The core clock ramps down to a low value..

#### Entering the power gating state

If a core entered the CC6 state and a transition to power gating is allowed the core becomes power gated by Vss removed.

#### Exiting the Core C6 state (CC6 state)

There is a set of events, such as interrupts, which cause a core to exit the CC6 state.

#### Entering the Package C6 state (PC6 state)

If all cores have entered the CC6 state and a transition to the PC6 state is enabled (by monitors), the processor enters the PC6 state.

#### Exciting from the Package C6 state (PC6 state)

If one of the cores leaves the CC6 state the processor excites the PC6 state.

## 2.2.2 Main features of the Bobcat core (14)

## Remark [35]

Flow diagram of entering

- the Core C6 (CC6) and

- the Package C6 (PC6) states

Wait for next Cstate request.

## 2.3 APU-lines of the Brazos platform

- 2.3.1 Overview of the Bobcat based APU lines of the Brazos platform

- 2.3.2 Mobile APU lines of the Brazos platform

2.3.1 Overview of the APU lines of the Brazos platform

## 2.3.1 Overview of the Bobcat based APU lines of the Brazos platform (1)

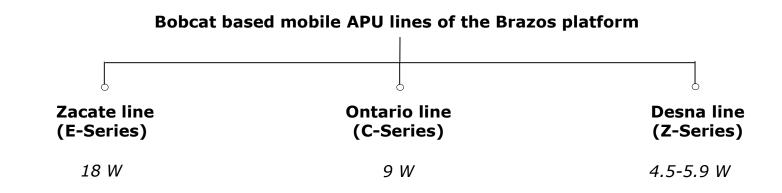

### 2.3.1 Overview of the APU lines of the Brazos platform

Direct X 11 capable graphics.

No Turbo Core on first introduced, Stepping B0 devices in 1/2011, CPU and GPU Turbo Core introduced later on select dual core Stepping C0 Series E and C devices in 8/2011. Socket: FT1 BGA.

### Target markets of Bobcat based APU lines of the Brazos platform [36]

All days battery life

#### Positioning of the Bobcat-based mobile APU lines of the Brazos platform [14]

# 2.3.2 Mobile APU lines of the Brazos platform

## 2.3.2 Mobile APU lines of the Brazos platform (1)

#### 2.3.2 Bobcat based mobile APU lines of the Brazos platform

Direct X 11 capable graphics.

No Turbo Core on first, Stepping B0 devices in 1/2011,

CPU and GPU Turbo Core introduced later on select dual core Stepping C0 Series E and C devices in 8/2011. Socket: FT1 BGA.

#### Positioning of the Mobile APU lines of the Brazos platform [based on 14]

## 2.3.2 Mobile APU lines of the Brazos platform (3)

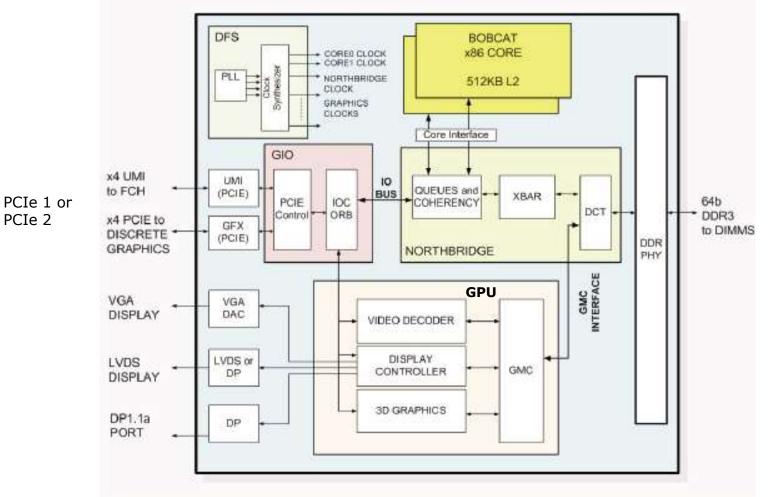

#### The common block diagram of the Zacate, Ontario and Desna Fusion APUs [28]

GMC: Graphics Memory Controller DP: Display port DFS: Digital Frequency Synthesizer UMI: Unified Media interface

FCH: Fusion Controller Hub LVDS: Low Voltage Differential Signaling VGA: Video Graphics Array

#### Remarks

- 1) AMD's Fusion architecture implements an efficient form of the UMA architecture (Unified Memory Architecture) in which a part of the system memory is used as the graphics frame buffer [28].

- 2) The Zacate, Ontario and Desna processors are part of the Brazos mobile platform, as already stated.

#### **Microarchitecture of Mobile APUs of the Brazos platform**

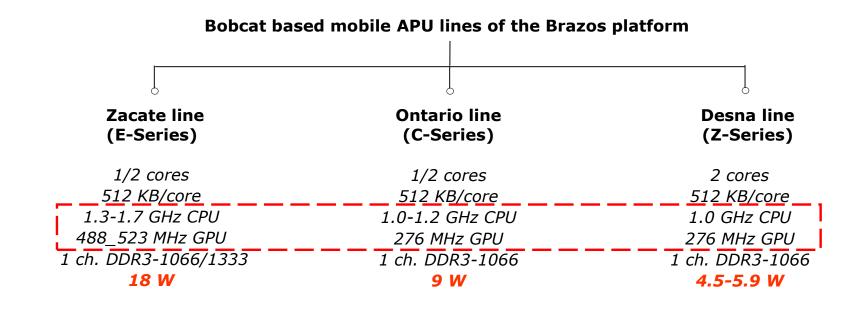

- Zacate, Ontario and Desna APUs have basically the same microarchitecture.

- The main difference between them is that they have decreasing clock rates (both CPU and GPU clock rates) and accordingly decreasing power consumption (18 W/9 W/~5 W), as shown below.

## 2.3.2 Mobile APU lines of the Brazos platform (6)

#### Key features of Mobile APU lines of the Brazos platform

Direct X 11 capable graphics.

No Turbo Core on first, Stepping B0 devices in 1/2011, CPU and GPU Turbo Core introduced later on select dual core Stepping C0 Series E and C devices in 8/2011.

Socket: FT1 BGA.

#### Main features of mobile APU lines of the Brazos platform

|                  |                                                       | Core<br>count | L2       | GPU                                         | fc (GPU)<br>(MHz) | 1 Ch. DDR3<br>(up to) |                                                                                                             |

|------------------|-------------------------------------------------------|---------------|----------|---------------------------------------------|-------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|

|                  | Mainstream A-Series<br>(Llano-based)                  |               |          |                                             |                   |                       |                                                                                                             |

| M                | Essential<br>E-series<br>(Zacate)                     | 2C            | 2x512 KB | HD 6320                                     | 488-508           | DDR3-1333             | 1/11<br><b>Zacate</b><br>40 nm, ~75 mm <sup>2</sup> , ~450 mtrs<br>1.3-1.65 GHz<br>18 W, FT1 BGA<br>E-4xx   |

| b                | (Bobcat-based)<br>Value                               | 1C            | 512 KB   | HD 6310                                     | 488-500           | DDR3-1333             | E-2xx/E-3xx                                                                                                 |

| l<br>l<br>e<br>s | C-series<br>Low power (Ontario)<br>(Bobcat-based)     | 2C            | 2x512 KB | HD 6250<br>(C-30/C-50)<br>HD 6290<br>(C-60) | 276               | DDR3-1066             | 1/11<br><b>Ontario</b><br>40 nm, ~75 mm <sup>2</sup> , ~450 mtrs<br>1.0-1.2 GHz<br>9 W, FT1 BGA<br>C-50/C60 |

|                  |                                                       | 1C            | 512 KB   |                                             |                   |                       | C-30                                                                                                        |

|                  | Z-series<br>Ultra Low (Desna)<br>power (Bobcat-based) | 2C            | 2x512 KB | HD 6250                                     | 276               | DDR3-1066             | 6/11<br><b>Desna</b><br>40 nm, ~75 mm², ~450 mtrs<br>1.0 GHz<br>5.9 W, FT1 BGA<br>Z-0x                      |

# Differences in the microarchitectures of the Bobcat-based Zacate, Ontario and Desna APUs-1

a) A few Zacate and Ontario models (E-series and C-series) have only a single Bobcat core, while the other core is disabled on the die, as indicated in the next Figure.

# Differences in the microarchitectures of the Bobcat-based Zacate, Ontario and Desna APUs-2

|                  |                                      | Core<br>count | L2       | GPU                                         | <b>fc (GPU)</b><br>(MHz) | 1 Ch. DDR3<br>(up to) |                                                                                                             |

|------------------|--------------------------------------|---------------|----------|---------------------------------------------|--------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|

|                  | Mainstream A-Series<br>(Llano-based) |               |          |                                             |                          |                       |                                                                                                             |

| M                | Essential<br>E-series<br>(Zacate)    | 2C            | 2x512 KB | HD 6320                                     | 488-508                  | DDR3-1333             | 1/11<br><b>Zacate</b><br>40 nm, ~75 mm <sup>2</sup> , ~450 mtrs<br>1.3-1.65 GHz<br>18 W, FT1 BGA<br>E-4xx   |

| b                | Value                                | 1C            | 512 KB   | HD 6310                                     | 488-500                  | DDR3-1333             | E-2xx/E-3xx                                                                                                 |

| i<br>I<br>e<br>s | C-series<br>Low power (Ontario)      | 2C            | 2x512 KB | HD 6250<br>(C-30/C-50)<br>HD 6290<br>(C-60) | 276                      | DDR3-1066             | 1/11<br><b>Ontario</b><br>40 nm, ~75 mm <sup>2</sup> , ~450 mtrs<br>1.0-1.2 GHz<br>9 W, FT1 BGA<br>C-50/C60 |

|                  |                                      | 1C            | 512 КВ   |                                             |                          |                       | C-30                                                                                                        |

|                  | Ultra Low Z-series<br>power (Desna)  | 2C            | 2x512 KB | HD 6250                                     | 276                      | DDR3-1066             | 6/11<br><b>Desna</b><br>40 nm, ~75 mm <sup>2</sup> , ~450 mtrs<br>1.0 GHz<br>5.9 W, FT1 BGA<br>Z-0x         |

# Differences in the microarchitectures of the Bobcat-based Zacate, Ontario and Desna APUs-3

b) Different models of the Zacate, Ontario and Desna lines include slightly different GPUs, nevertheless all have the same number of processing units (80), as shown below.

#### Use of different GPU cores in different mobile processors [29]

#### "Zacate" (40 nm)

|         |         |       |     |          |       |            |                    |                   | · — — · |                     |         |         |            |       |              |

|---------|---------|-------|-----|----------|-------|------------|--------------------|-------------------|---------|---------------------|---------|---------|------------|-------|--------------|

|         |         |       |     |          |       | CPU        |                    |                   |         | G                   | PU      |         |            | TOD   | Deleved      |

| Mode    | I Ste   | Cor   | es  | Freq.    | Turbo | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo   | Memory     | TDP   | Released     |

| E-240 d | Ø В0    | 1     |     | 1.5 GHz  |       | 512 KB     | 15×                | 1.175 - 1.35      |         |                     | 500 MHz |         | DDR3-1066  |       | Jan 4, 2011  |

| E-300   | B0      |       |     | 1.3 GHz  |       |            | 13×                |                   | HD 6310 | 80:8:4              | 488 MHz | N/A     | DDR3-1333  |       | Aug 22, 2011 |

| E-350 d | Ø В0    |       |     | 1.6 GHz  | N/A   |            | 16×                | 1.25 - 1.35       |         |                     | 492 MHz |         | DDR3-1066  | 10.14 | Jan 4, 2011  |

| E-450   | CO      | 2     |     | 1.65 GHz | N/A   | 2 × 512 KB | 16.5×              |                   | HD 6320 | 80:8:4              | 508 MHz | 600 MHz | DDR3-1333  | 18 W  | Aug 22, 2011 |

| E1-120  | 0       |       |     | 1.4 GHz  |       |            | 14×                |                   | HD 7310 | 80:8:4              | 500 MHz | N/A     | DDR3-1066  |       | 01 2012      |

| E2-180  | 0       |       |     | 1.7 GHz  |       |            | 17×                |                   | HD 7340 | 80:8:4              | 523 MHz | 680 MHz | DDR3-1333  |       | Q1 2012      |

| Ontari  | o'' (40 | nm)   |     |          |       |            |                    |                   |         |                     |         |         |            |       |              |

| lodel   | Step.   |       | 1   |          |       | CPU        |                    |                   |         | G                   | PU      |         | Memory     | TDP   | Released     |

|         | orop,   | Cores | Fr  | req. T   | urbo  | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo   | lineitiery |       |              |

| C-30 🗗  | -       | 1     | 1.2 | GHz      |       | 512 KB     | 12×                | 1.25 - 1.35       |         |                     |         |         |            |       |              |

| C-50 & | B0 | 2 | 1.0 GHz | N/A      | 2 × 512 KB | 10×      | 1.05 - 1.35 | HD 6250 | 80:8:4 | 276 MHz | N/A     | DDR3-1066 | 9 W | Jan 4, 2011  |

|--------|----|---|---------|----------|------------|----------|-------------|---------|--------|---------|---------|-----------|-----|--------------|

| C-60   | C0 | 2 | 1.0 GHZ | 1.33 GHz | 2 × 912 KD | 10-13.3× |             | HD 6290 | 80:8:4 | 276 MHz | 400 MHz |           |     | Aug 22, 2011 |

#### "Desna" (40nm)

| Madal  | Cton  |       |         | C     | :PU        |                    |                   |         | GP                  | U       |       |           | TOD   | Delegend     |

|--------|-------|-------|---------|-------|------------|--------------------|-------------------|---------|---------------------|---------|-------|-----------|-------|--------------|

| Model  | step. | Cores | Freq.   | Turbo | L2 Cache   | Multi <sup>1</sup> | V <sub>core</sub> | Model   | Config <sup>2</sup> | Freq.   | Turbo | Memory    | TDP   | Released     |

| Z-01 🗗 | B0    | 2     | 1.0 GHz | N/A   | 2 × 512 KB | 10                 |                   |         | 00.0.4              | 276 MHz | NI/A  | DDR3-1066 | 5.9 W | June 1, 2011 |

| Z-03   |       | 2     | 1.0 GHZ | DV/A  | 2 × 912 KD | 10×                |                   | HD 6250 | 00.0.4              |         | N/A   | DDR3-1066 | 4.5 W | Q1 2012      |

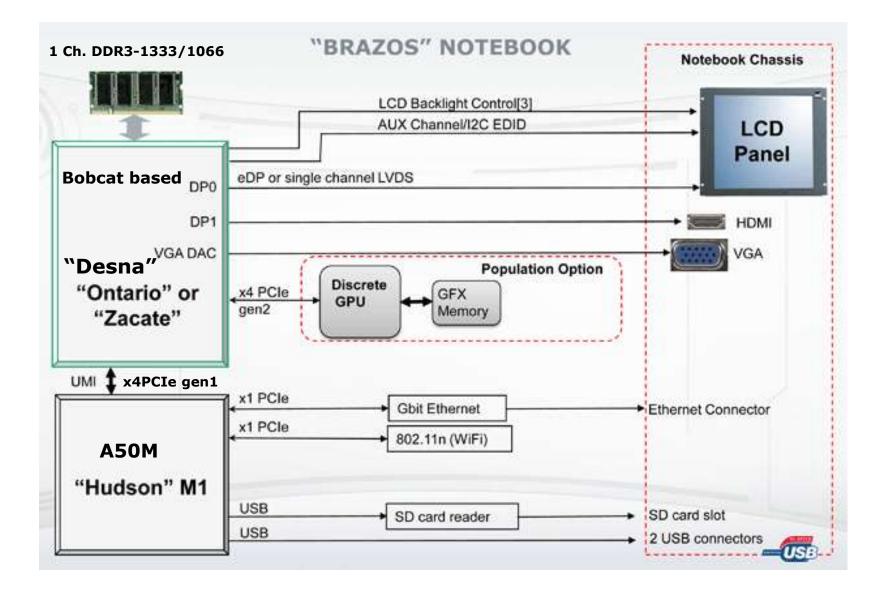

#### The Brazos notebook platform [37]

### Positioning the Hudson-M1 (A50M) Fusion Controller Hub (FCH) [38]

- All models support up to 4 channels of HD audio.

- A55T support up to 2 channels of HD audio.

| Model | Codename                                   | Platform                       | Fab<br>(nm) | UMI                       | SATA                     | USB<br>3.0 + 2.0 + 1.1 | RAID             | Gb Ethernet<br>MAC                      | 33 MHz<br>PCI    | SD <sup>1</sup> | VGA<br>DAC | TDP<br>(W) | Features / Notes                                     |

|-------|--------------------------------------------|--------------------------------|-------------|---------------------------|--------------------------|------------------------|------------------|-----------------------------------------|------------------|-----------------|------------|------------|------------------------------------------------------|

| A55T  | Hudson <mark>-</mark> M2T <sup>[N 1]</sup> | "Brazos" T                     |             | ×2 Gen 1                  | 1 × 3 Gbit/s<br>AHCI 1.1 | 0+8+0                  | No               | No                                      |                  | SDIO            | No         |            |                                                      |

| A50M  | Hudson-M1 <sup>[N 1]</sup>                 | "Brazos"                       |             | ×4 Gen 1 <sup>[M 1]</sup> | 6 × 6 Gbit/s             | 0+14+2                 |                  |                                         |                  | No              |            |            | ~920mw idle                                          |

| A60M  | Hudson-M2 <sup>(N-1)</sup>                 | "Sabine"                       |             | ~~~~~                     | AHCT1.2                  |                        |                  | /////////////////////////////////////// |                  |                 | Yes        |            |                                                      |

| A68M  | Hudson-M3L <sup>(N 1)</sup>                | "Brazos"<br>2.0                | 65          | ×4 Gen 1                  | 2 × 6 Gbit/s<br>AHCI 1.2 | 2+8+0                  | RAID 0,1         | 10/100/1000                             | No               | Yes             | No         | 4.7        | ~750mw idle                                          |

| A70M  | Hudson-M3 <sup>[N 1]</sup>                 | "Indus"<br>"Comal"<br>"Sabine" |             | +DP                       | 6 × 6 Gbit/s<br>AHCI 1.2 | 4 + 10 + 2             | 14 10 0,1        |                                         |                  |                 | Yes        |            | First native<br>USB 3.0<br>controller <sup>[6]</sup> |

| A45   | Hudson-D1 <sup>[N 2]</sup>                 |                                |             | ×4 Gen 2 <sup>[M 2]</sup> | 6 × 3 Gbit/s<br>AHCI 1.1 | 0 + 14 + 2             | No               | No                                      | Up to<br>4 slots | No              | No         |            |                                                      |

| A55   | Hudson-D2 <sup>[N 2]</sup>                 |                                |             |                           | And LT                   |                        |                  |                                         |                  |                 |            | 7.6        |                                                      |

| A75   | Hudson-D3 <sup>[N 2]</sup>                 | "Lynx"                         | 65          | ×4 Gen 2<br>+DP           | 6 × 6 Gbit/s<br>AHCI 1.2 | 4 + 10 + 2             | RAID 0,1,10      | 10/100/1000                             | Up to<br>3 slots | Yes             | Yes        | 7.8        | First native<br>USB 3.0<br>controller <sup>(6)</sup> |

| A85X  | Hudson-D4                                  | "Virgo"                        |             |                           | 8 × 6 Gbit/s<br>AHCI 1.2 |                        | RAID<br>0,1,5,10 |                                         |                  |                 |            |            |                                                      |

| A55E  | Hudson-E1 <sup>[N 3]</sup>                 |                                | 65          | ×4 Gen 2                  | 6 × 6 Gbit/s<br>AHCI 1.2 | 0 + 14 + 2             | RAID<br>0,1,5,10 | 10/100/1000                             | Up to<br>4 slots | No              | No         | 5.9        |                                                      |

Codenames:

M: for notebook platform

UMI:

**D**: for desktop platform

E: for embedded platform

UMI ×4 Gen 1 is based on <u>PCIe 1.1</u> × 4 lanes, giving 1 GBps bandwidth UMI ×4 Gen 2 is based on <u>PCIe 2.0</u> × 4 lanes, giving 2 GBps bandwidth

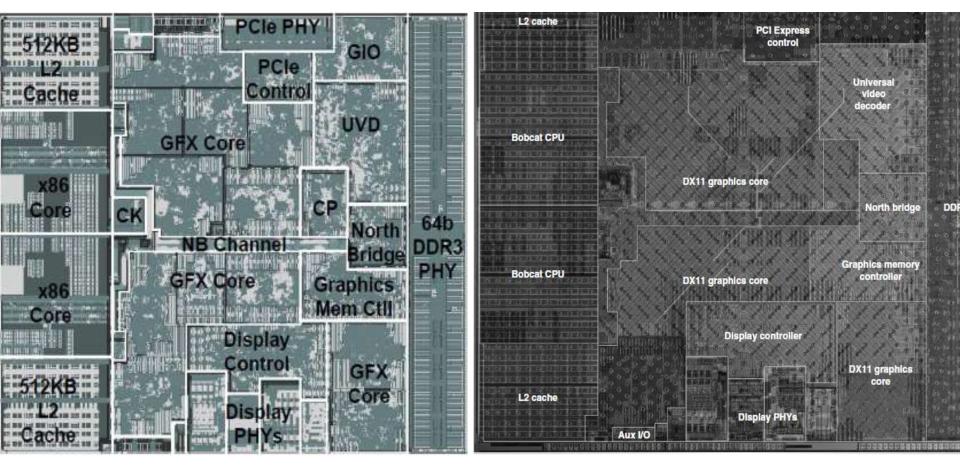

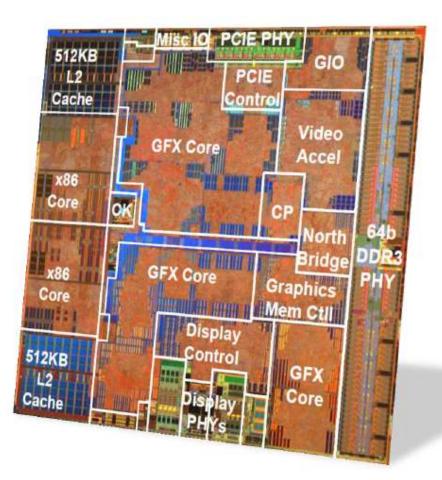

#### Die plots of the Zacate, Ontario and Desna APUs

All three APUs have the same die plot, as demonstrated below.

### Die plots of the Zacate and Ontario processors [28], [31]

#### Zacate

### Ontario

# 2.3.2 Mobile APU lines of the Brazos platform (16)

#### **Die plots of the Zacate and Desna processors** [36]

#### Zacate

#### Desna

### **Contrasting the die plots of Ontario and Intel's Pineview dual core Atom processor** [39]

# 2.3.2 Mobile APU lines of the Brazos platform (18)

#### **OpenCL programming support for the Ontario and the Zacate lines**

AMD's APP SDK 2.3 (1/2011) (formerly ATI Stream SDK) (provides OpenCL support for both lines .

New features of APP SDK 2.3 [40]

Improved OpenCL runtime performance:

Improved kernel launch times.

Improved PCIe transfer times.

Enabled DRMDMA for the ATI Radeon 5000 Series and AMD Radeon 6800 GPUs that are specified in the <u>Supported Devices</u>.

Increased size of staging buffers.

Enhanced Binary Image Format (BIF).

Support for UVD video hardware component through OpenCL (Windows 7).

Support for AMD E-Series and C-Series platforms (AMD Fusion APUs).

Support for Northern Islands family of devices.

Support for AMD Radeon<sup>™</sup> HD 6310 and AMD Radeon<sup>™</sup> 6250 devices.

Support for OpenCL math libraries: FFT and BLAS-3, available for download at <u>AMD Accelerated</u> <u>Parallel Processing Math Libraries</u>.

Preview feature: An optimization pragma for unrolling loops.

Preview feature: Support for CPU/X86 image. This enables the support for Image formats, as described in the Khronos specification for OpenCL, to be run on the x86 CPU. It is enabled by the following environment variable in your application: CPU\_IMAGE\_SUPPORT.

### Positioning of the Bobcat-based Brazos mobile lines vs. Intel's lines [41]

#### Remark

A-Series processors address the midrange and high-end market [41]

#### Main features of Bobcat-based ultra-portable mobile lines with a TDP of ~10-20W

| Base arch./<br>stepping                   | Intro       | Ultra-<br>portable<br>mobile<br>family | Series          | Techn. | Core count<br>(up to)                                  | L2<br>(up to)               | L3            | GPU<br>(APU) | Memory<br>(up to) | TDP<br>[W] | Socke<br>t   |

|-------------------------------------------|-------------|----------------------------------------|-----------------|--------|--------------------------------------------------------|-----------------------------|---------------|--------------|-------------------|------------|--------------|

|                                           | 1/2011      | Zacate<br>(not SoC)                    | E<br>Series     | 40 nm  | 2                                                      | 512 KB/<br>core<br>Private  | -             | Yes          | DDR3L-<br>1333    | 18         | FT1<br>(BGA) |

| <b>Family14h</b><br>(00h-0Fh)<br>(Bobcat) | 6/2012      | Zacate<br>(not SoC)                    | E1/E2<br>Models | 40 nm  | 2                                                      | 512 KB/<br>core<br>Private  | -             | Yes          | DDR3L-<br>1333    | 18         | FT1<br>(BGA) |

|                                           | 1/2011      | Ontario                                | C<br>Series     | 40 nm  | 2                                                      | 512 KB/<br>core<br>private  | -             | Yes          | DDR3-<br>1066     | 9          | FT1<br>(BGA) |

| Family 16h<br>(10H-1fH)<br>(Jaguar)       | 5/2013      | Kabini<br>(SoC)                        | A<br>Series     | 28 nm  | 4                                                      | 2 MB<br>shared              | -             | Yes          | DDR3L-<br>1866    | 9/<br>15   | FT3          |

| Family 16h                                | 4/2014      | Beema<br>(SoC)                         | A<br>Series     | 28 nm  | 4 cores<br>with a<br>shared L2<br>cache                | 2 MB<br>shared              | -             | Yes          | DDR3L-<br>1866    | 15         | FT3b         |

| (30H-3fH)<br>(Puma+)                      | 5/2015      | Carrizo-L<br>(SoC)                     | A<br>Series     | 28 nm  |                                                        | 2 MB<br>shared              | -             | Yes          | DDR3L-<br>1866    | 10/<br>15  | FP4          |

| Family 17h<br>(00H-0fH)<br>(Zen)          | 10/201<br>7 | Raven<br>Ridge<br>(SoC)                | Ryzen<br>7/5/3  | 14 nm  | 4-core CCX,<br>private L2<br>and shared<br>L3 cache(s) | <sup>1</sup> ⁄2 MB/<br>core | 1 MB/<br>core | Yes          | DDR4-<br>2400     | 15         | AM4          |

APU: Accelerated Processing Unit (CPU +GPU) CCX: Core CompleX

<sup>2</sup>: 2\*512 KB for Turion X2, 2\*1 MB for Turion X2 Ultra

UMI: Universal Media Interface

# **Die plot of the Zacate APU** [42]

# 2.3.2 Mobile APU lines of the Brazos platform (22)

#### "Zacate" (40nm)

[edit]

edit

- All models support: SSE, SSE2, SSE3, SSSE3, SSE4a, NX bit, AMD64, PowerNow!, AMD-V

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Single-channel, up to 1066 MHz)

- Config GPU are Unified Shaders (Vertex shader/Geometry shader/Pixel shader) : Texture mapping unit : Render

Output unit

|                                |              | $\frown$ |              |                    |                 |              |               |              |             | $\frown$ |             |                    |

|--------------------------------|--------------|----------|--------------|--------------------|-----------------|--------------|---------------|--------------|-------------|----------|-------------|--------------------|

| Model<br>Number                | CPU<br>cores | Freq.    | L2 Cache     | Multi <sup>1</sup> | Voltage         | Model<br>GPU | Config<br>GPU | GPU<br>Freq. | ими         | TDF      | Socket      | Release<br>Date    |

| E-Series Ę <del>,</del><br>240 | 1            | 1.5 GHz  | 512 KB       | 18.75x             | 1.175 -<br>1.35 | HD 6310      | 80:8:4        | 500MHz       | 2.5<br>GT/s | 18<br>W  | BGA-<br>413 | January 4,<br>2011 |

| E-Series Ę <sub>5</sub><br>350 | 2            | 1.6 GHz  | 2x 512<br>KB | 20x                | 1.25 - 1.35     | HD 6310      | 80:8:4        | 500MHz       | 2.5<br>GT/s | 18<br>W  | BGA-<br>413 | January 4,<br>2011 |

Table: Main features of AMD's mainstream Zacate Fusion APU line [43]

#### "Ontario" (40nm)

- All models support: SSE, SSE2, SSE3, SSSE3, SSE4a, NX bit, AMD64, PowerNow!, AMD-V

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Single-channel, up to 1066 MHz)

- Config GPU are Unified Shaders (Vertex shader/Geometry shader/Pixel shader) : Texture mapping unit : Render

Output unit

| Model<br>Number               | CPU<br>cores | Freq.   | L2 Cache  | Multi <sup>1</sup> | Voltage        | Model<br>GPU | Config<br>GPU | GPU<br>Freq. | имі         | TDP | Socket      | Release Date       |

|-------------------------------|--------------|---------|-----------|--------------------|----------------|--------------|---------------|--------------|-------------|-----|-------------|--------------------|

| C-Series C <sub>-</sub><br>30 | 1            | 1.2 GHz | 512 KB    | 15x                | 1.25 -<br>1.35 | HD 6250      | 80:8:4        | 280MHz       | 2.5<br>GT/s | 9 W | BGA-<br>413 | January 4,<br>2011 |

| C-Series C <sub>5</sub>       | 2            | 1.0 GHz | 2x 512 KB | 12.5x              | 1.05 -<br>1.35 | HD 6250      | 80:8:4        | 280MHz       | 2.5<br>GT/s | 9 W | BGA-<br>413 | January 4,<br>2011 |

Table: Main features of AMD's low power Ontario Fusion APU line [43]

# 2.4 Bobcat-based APU lines of the Brazos 2.0 platform

# 2.4 APU lines of the Brazos 2.0 platform (1)

#### **APU lines of the Brazos 2.0 platform**

Introduced in 6/2012

#### Brazos 2.0 APU line

Zacate APUs

E2-1800 E1-1200

18 W

DX 11 support OpenCL 1.1 support GPU Turbo mode available on the E2-1800 model.

The same models are used both in value desktops and value notebooks (termed also as extra portable notebooks).

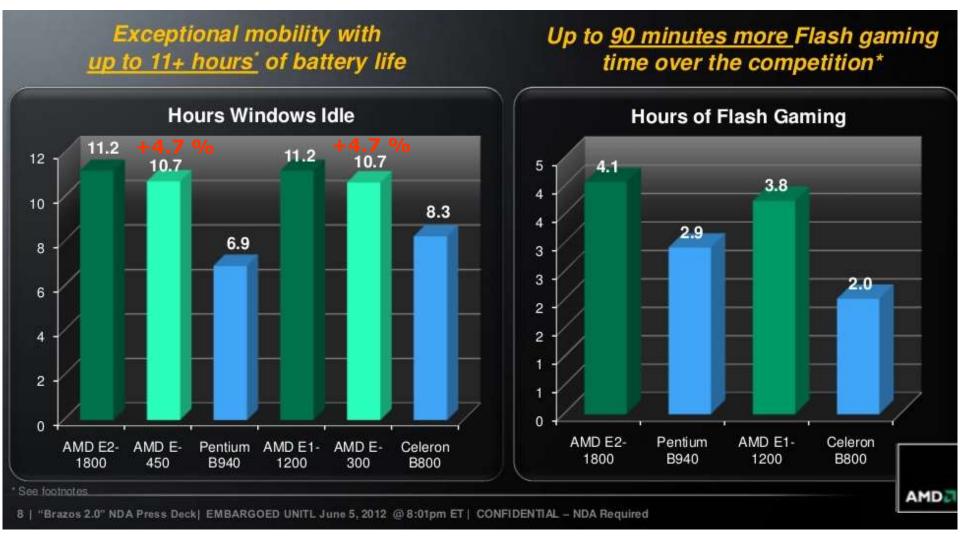

### **Contrasting the Brazos 2.0 and Brazos platforms**

### a) Contrasting the Brazos 2.0 APUs and the previous Brazos APUs [44].

Neither of the E2-1800 and the E1-1200 CPU cores are new designs but only minor upgrades of the previous Brazos E-450 and E-300 CPUs, as detailed in the subsequent Remark.

### Remark

Differences of the Brazos 2.0 APUs from the previous Brazos APUs

The CPUs of the Brazos 2.0 APUs are minor upgrades of the previous Brazos line, as follows: The E2-1800 is an upgrade of the previous Brazos E-450 whereas the E2-1200 is an upgrade of the E-300.

The improvement is restricted to a few % clock speed increase, as indicated in the Table below.

• The GPUs associated with the Brazos 2.0 GPUs are rebranded GPUs of the HD 6xxx line, as follows:

The HD 7310 is a rebranded HD 6310 whereas the HD 7340 is a rebranded HD 6320, both with a slight clock speed increase, as shown below.

|                     | Brazo   | os 2.0  | Braz     | zos     |  |  |  |

|---------------------|---------|---------|----------|---------|--|--|--|

|                     | E2-1800 | E2-1200 | E-450    | E-300   |  |  |  |

| fc of the CPU       | 1.7 GHz | 1.4 GHz | 1.65 GHz | 1.3 GHz |  |  |  |

| GPU type            | HD 7310 | HD 7340 | HD 6310  | HD 6320 |  |  |  |

| Basic fc of the GPU | 523 MHz | 500 MHz | 508 MHz  | 488 MHz |  |  |  |

| Turbo fc of the GPU | 680 MHz |         | 600 MHz  |         |  |  |  |

# b) Contrasting the FCHs of the Brazos 2.0 platform with those of the previous Brazos platform [45].

|                               | Note           | book           | Des            | ktop           |

|-------------------------------|----------------|----------------|----------------|----------------|

| 2011 Branding                 | A50M           | A68M           | A45            | A68            |

| Target Platform               | "Brazos"       | "Brazos 2.0"   | "Brazos"       | "Brazos 2.0"   |

| PCI Express Support (CF)      | Y              | 1x4            | Y              | 1x4            |

| Clock Gen                     | N              | Y              | N              | Y              |

| SATA                          | 6 x 6Gb/s      | 2 x 6Gb/s      | 6 x 3Gb/s      | 3 x 6Gb/s      |

| HD Audio                      | Up to 4-codecs | Up to 4-codecs | Up to 4-codecs | Up to 4-codecs |

| PCIe GPPs                     | 4 x1 Gen 2     |

| Unified Media Interface (UMI) | x4 Gen 1       | x4 Gen 2       | x4 Gen 2       | x4 Gen 2       |

| USB 3.0 + 2.0 + 1.1 Ports     | 0 + 14 + 2     | 2 + 8 + 0      | 0 + 14 + 2     | 2 + 8 +0       |

| APU Fan Control               | Y              | Y              | Y              | Y              |

| SD Controller                 | N              | Y              | N              | Y              |

| 33MHz PCI                     | N              | N              | Up to 4 slots  | Up to 3 slots  |

As indicated, the major differences are additional PCIe 2.0 x4 and USB 3.0 support in Brazos 2.0 FCHs.

# Battery life comparison of Brazos, Brazos 2.0 and Intel's Atom models [45]

# Main features of Mobile APU models of the Brazos 2.0 platform [45]

| 2012 AMD  | 2012 AMD E-Series APU for Essential Notebooks and Desktops |     |              |                         |                         |                         |          |                                           |  |  |  |  |

|-----------|------------------------------------------------------------|-----|--------------|-------------------------|-------------------------|-------------------------|----------|-------------------------------------------|--|--|--|--|

| APU Model | AMD<br>Radeon™<br>Brand                                    | TDP | CPU<br>Cores | CPU Clock<br>(Max/Base) | AMD<br>Radeon™<br>Cores | GPU Clock<br>(Max/Base) | L2 Cache | Max DDR3                                  |  |  |  |  |

| E2-1800   | HD 7340                                                    | 18W | 2            | 1.7GHz                  | 80                      | 680MHz/<br>523MHz       | 1MB      | DDR3-1333<br>DDR3L1066<br>DDR3U-<br>1066  |  |  |  |  |

| E1-1200   | HD 7310                                                    | 18W | 2            | 1.4GHz                  | 80                      | 500MHz                  | 1MB      | DDR3-1066<br>DDR3L-1066<br>DDR3U-<br>1066 |  |  |  |  |

# The Brazos 2.0 platform [45]

#### "Zacate" APUs Dual Core CPU - 40nm "Bobcat" core - 1 MB L2, 64-bit FPU - 18W TDP Complete ISA support - SSE1-3 and virtualization Memory Control x86 Cores SIMD •Graphics Core Engine – 80 Radeon<sup>™</sup> Cores Array – New AMD Radeon<sup>™</sup> HD 7000 Series GPU DirectX® 11 capable - OpenCL<sup>™</sup> 1.1 enabled Universal Improved graphics boost Video Decoder AMD VISION Engine •3rd generation Unified Video Decoder •DDR3 1066-1333, 2 DIMMs Hami •FT1 BGA package (same as current Brazos) Platform Interfaces P **Display and I/O** •Two dedicated digital display interfaces dvi - Configurable as HDMI, DVI, and/or Display Port - Also supports single link LVDS for internal panels •VGA SATA •8 PCle Gen 2 LPC •"Hudson-3L" FCH SPI FCH "Hudson"\_3L PCie - USB 3.0 Support (2 ports) / USB 2.0 (8 ports) A68/A68M 4X1 FCH HD AUDIO CIR - Desktops: A68 USB2/USB3 - Mobiles: A68M SD Controller

# 2.4 APU lines of the Brazos 2.0 platform (8)

# Positioning the Brazos 2.0 APU models [45]

|          | AMD                                                                    | Intel         |

|----------|------------------------------------------------------------------------|---------------|

| 2.0      | AMD E2-1800 Accelerated Processor<br>vith AMD Radeon™ HD 7340 Graphics | Pentium       |

| "Brazos  | AMD E1-1200 Accelerated Processor<br>vith AMD Radeon™ HD 7310 Graphics | Celeron       |

| "Brazos" | AMD C-60 Accelerated Processor<br>with AMD Radeon™ HD 6290 Graphics    | Atom          |

|          | AMD Z-01 Accelerated Processor<br>with AMD Radeon™ HD 6250 Graphics    | Atom Z-Series |

# 2.5 APU lines of the Embedded G-Series platform

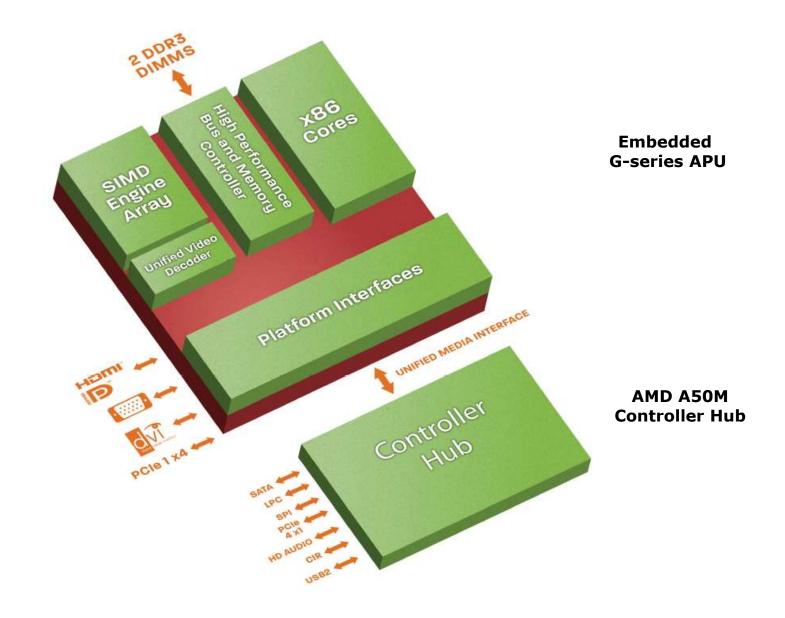

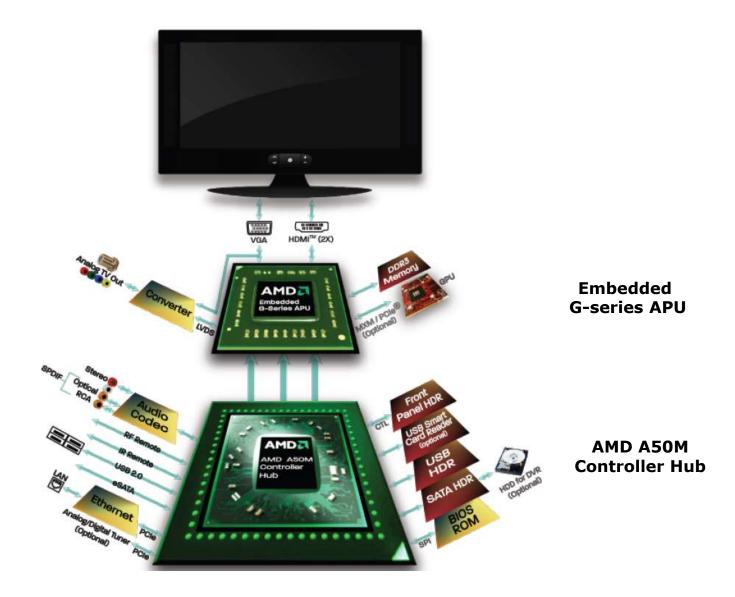

### **Embedded G-Series**

- Introduced in 1/2011

- Typical use: In TV Set Top Boxes

- They are basically Zacate, Ontario or Desna designs, as shown below.

# Main features of the embedded GPU lines [29]

|        |                      |             | Core<br>count | L2       | fc<br>CPU   | GPU<br>Direct X11 | fc<br>GPU                                                          |                                                                  |                         |

|--------|----------------------|-------------|---------------|----------|-------------|-------------------|--------------------------------------------------------------------|------------------------------------------------------------------|-------------------------|

|        |                      | 2C 2x512 KB |               | 1.4-1.65 | HD 6310     | 500/520           | 1(11<br><b>Zacate</b><br>40 nm, Up to DDR3-1333<br>FTI BGA<br>T48N |                                                                  |                         |

| Е      | G-series<br>with GPU | 18 W        | 1C            | 512 KB   | GHz         | HD 6320           | MHz                                                                | T56N<br>T52R<br>(1C disabled)                                    |                         |

| m<br>b |                      | 9 W -       | 2C            | 2x512 KB | 1.0-1.2     | HD 6250           | 280 MHz                                                            | 280 MHz                                                          | 1/11<br>Ontario<br>T40N |

| e      |                      | 9 W         | 1C            | 512 KB   | GHz         | HD 6290           | 200 1112                                                           | T44R                                                             |                         |

| d<br>d |                      | 6.4/5.5 W   | 2C            | 2x512 KB | - 1.0 GHz   | HD 6250           | 280 MHz                                                            | 6/11<br><b>Desna</b><br>T40E                                     |                         |

| e      |                      |             | 1C            | 512 KB   |             | пD 6250           | 200 1112                                                           | T40R<br>(1 C disabled)                                           |                         |

| d      |                      | 18 W -      | 2C            | 2x512 KB | + 1.4 GHz   |                   |                                                                    | <u>کرا ا</u><br><b>Zacate</b><br>T48 L                           |                         |

|        | G-Series             | 18 W ·      | 1C            | 512 KB   | 1.4 GHZ     | _                 | _                                                                  | T30 L<br>(GPU disabled)                                          |                         |

|        | without GPU          | 5 W         | 1C            | 512 KB   | 0.8-1.0 GHz | _                 | _                                                                  | 3(11<br><b>Desna</b><br>T24 L<br>(1C disabled)<br>(GPU disabled) |                         |

# 2.5 APU lines of the Embedded G-Series platform (3)

# **Graphics support of the G-Series** [46]

- Direct X 11 with Shader Model 5

- Open CL 1.1

- Open GL 3.2.2.1

#### System architecture of a Bobcat-based embedded GPU lines [47]

# Main features of the Controller Hubs of the lines of the Embedded G-Series platform [47]

| Model | PCI<br>Express®                                                     | PCI                                          | Gigabit<br>Ethernet<br>MAC | RAID                                            | SATA              | USB               | Additional<br>Interfaces/Features                                                                                           |  |  |

|-------|---------------------------------------------------------------------|----------------------------------------------|----------------------------|-------------------------------------------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| A55E  | 4x1 or 1x 4<br>PCIe®<br>Generation<br>2 UMI<br>connection<br>to APU | 33MHz<br>with<br>support<br>for 4<br>masters | Yes                        | 0/1/5/10 support<br>with FIS-based<br>switching | 6x 6Gb/s<br>ports | 14x v2.0<br>ports | SPI, LPC, SMBus,<br>CIR, HD audio, up<br>to 102 GPIO, Fan<br>control, Integrated<br>Clock Generation,<br>pin compatible for |  |  |

| A50M  | 4x1 or 1x 4                                                         | No                                           | No                         | No                                              |                   |                   | A50M and A55E                                                                                                               |  |  |

# 2.5 APU lines of the Embedded G-Series platform (6)

Use of a Bobcat-based embedded APU in a TV set top box [48]

# 3. Family 16h Models 00h-0Fh (Jaguar-based) APU lines

- 3.1 Overview of the Jaguar-based APU lines

- 3.2 The Jaguar core

- 3.3 Jaguar-based APU lines

# 3.1 Overview of the Jaguar-based APU lines

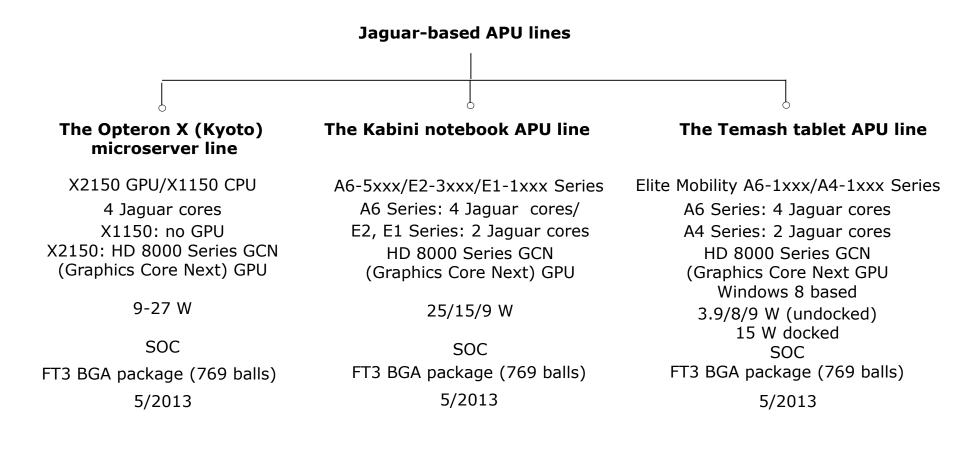

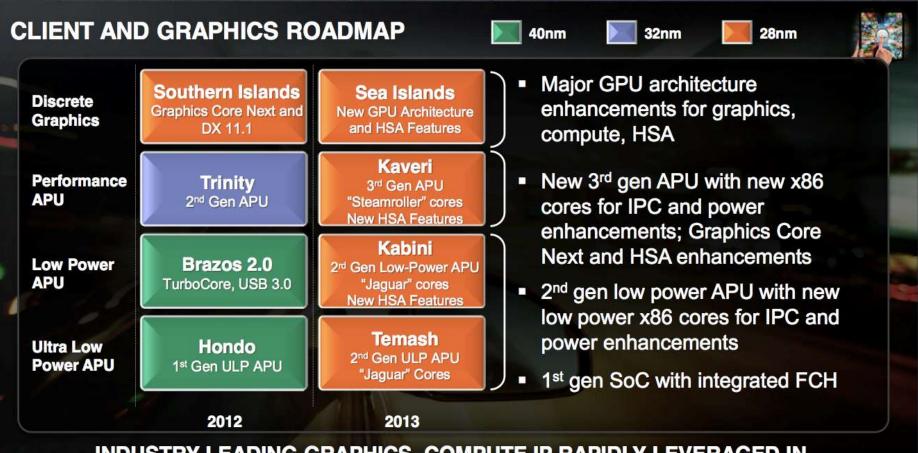

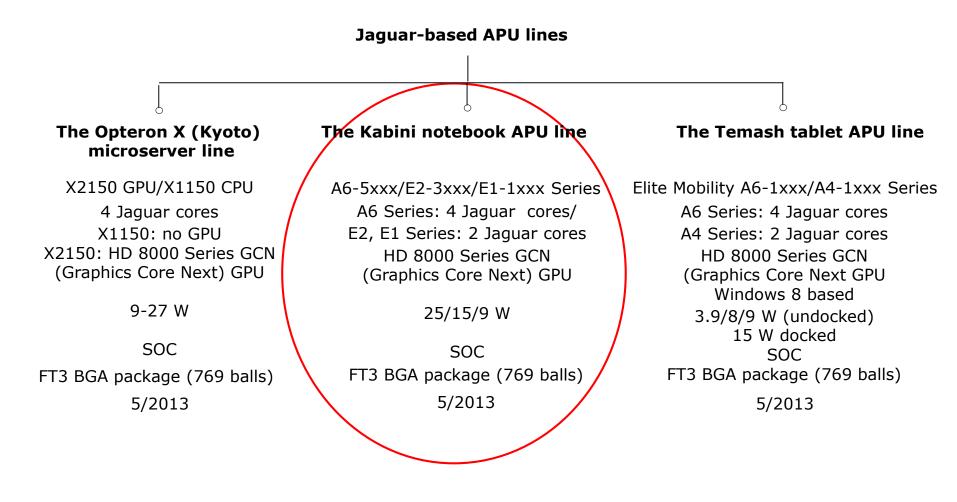

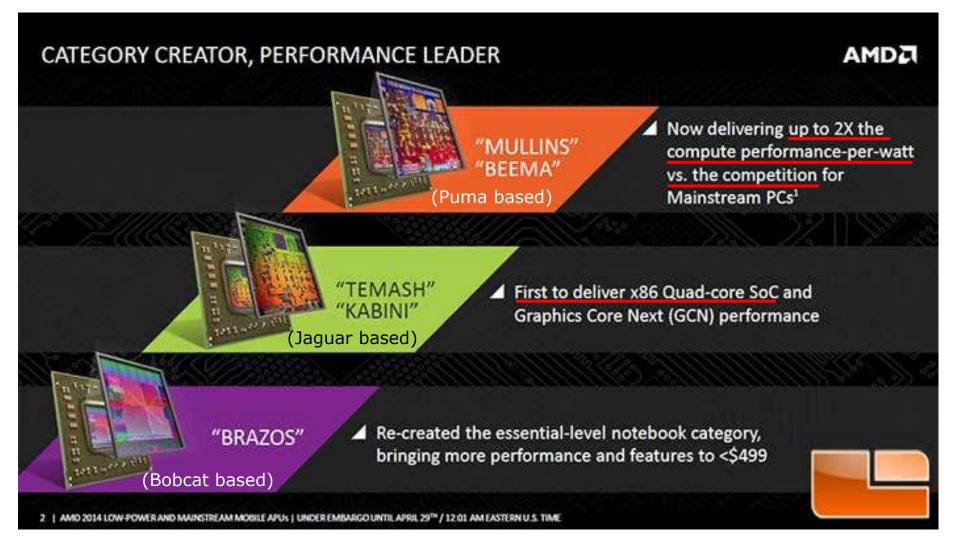

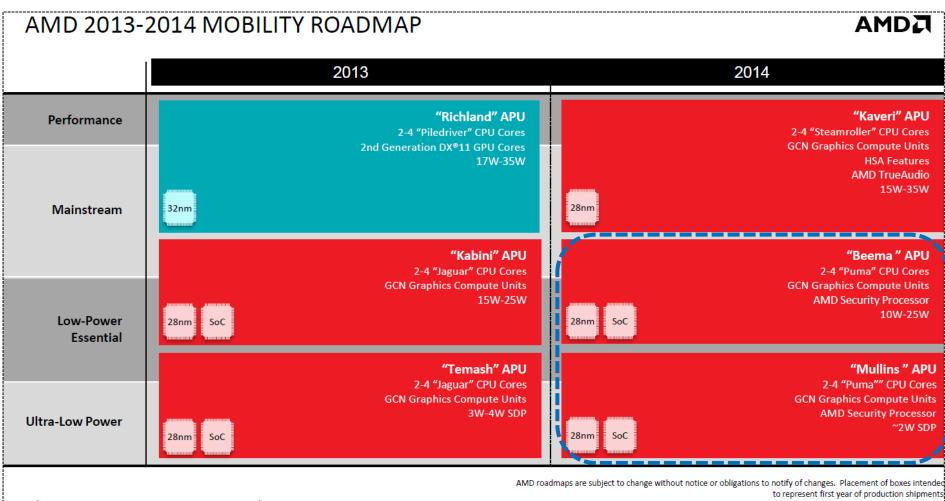

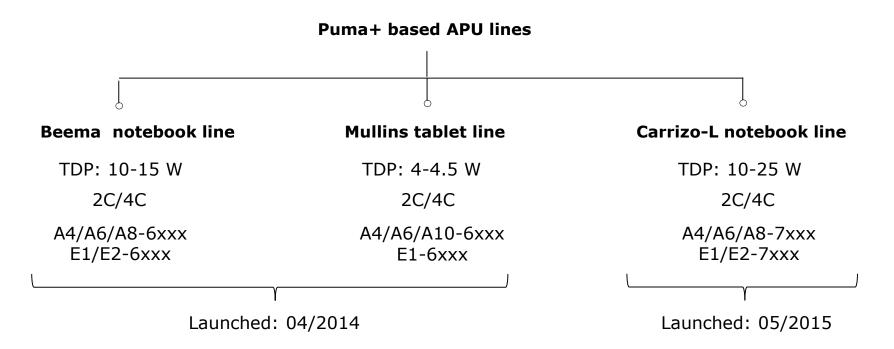

### 3.1 Overview of the Jaguar-based APU lines -1

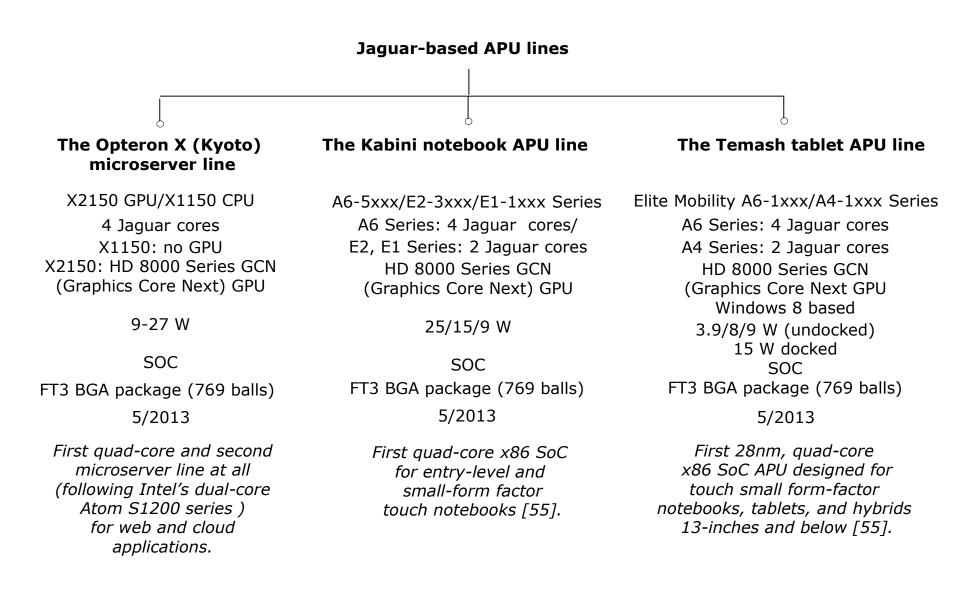

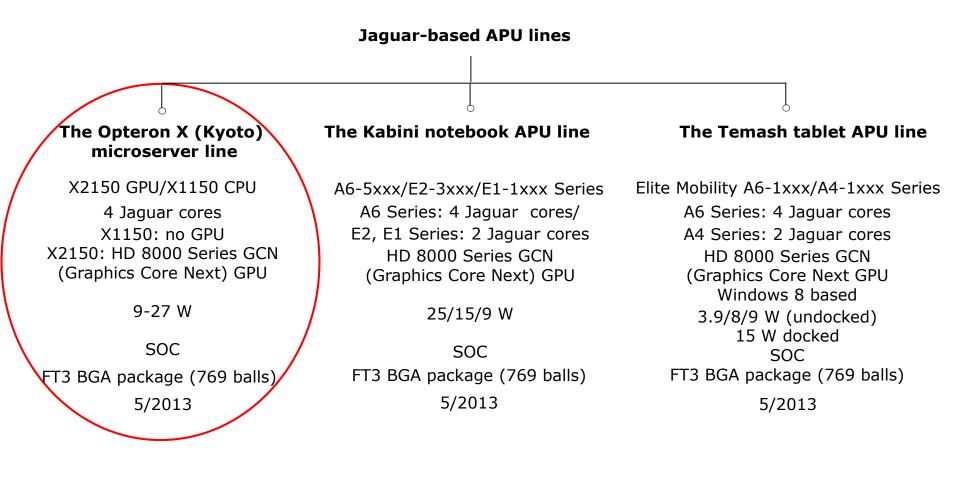

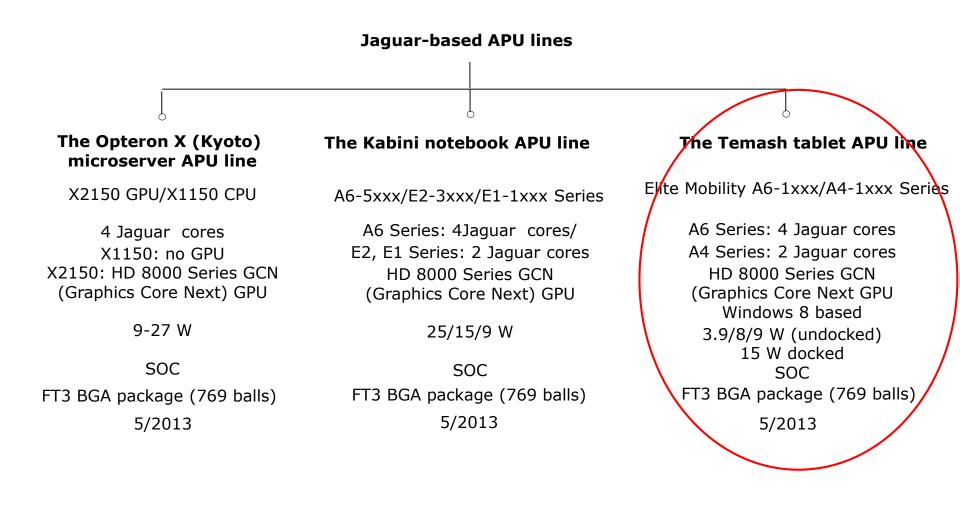

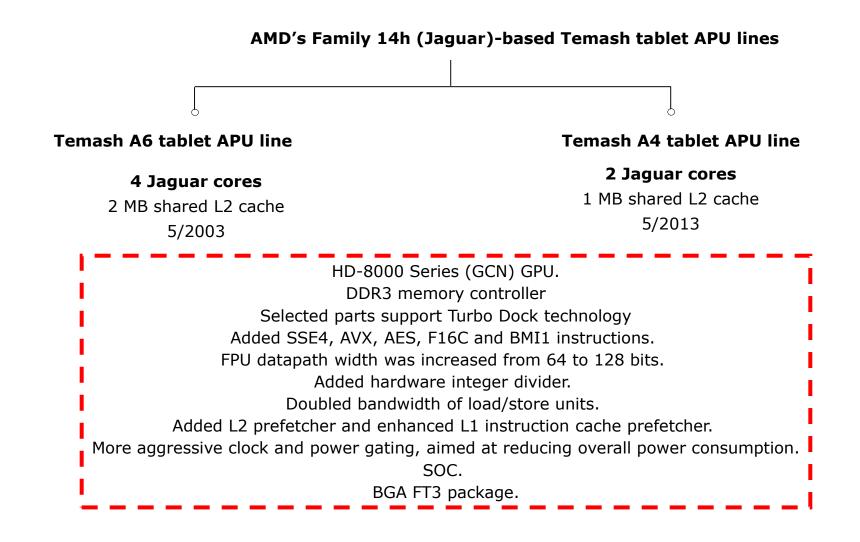

• Jaguar-based APUs are AMD's second low power oriented product series that were announced at the Hot Chips 2012 in 8/2012 and introduced in 5/2013.

They focus on the mobile market, especially on ultra-light notebooks and tablets but include also a line of micro servers, released in 5/2013 as well.

- Jaguar-based products follow AMD's successful Bobcat-based product lines of the Brazos platform that are typically used in ultra-light notebooks and tablets.

- Jaguar-based APUs compete with Intel's Atom line of processors, and also with ARM designs, as ARM's processor design were used in most smartphones and tablets, e.g. in Apple's iPad, Google's Galaxy Nexus 7 and Amazon's Kindle Fire [49].

- They are part of AMD's new market strategy that emphasizes the mobile market segment in AMD's overall market policy.

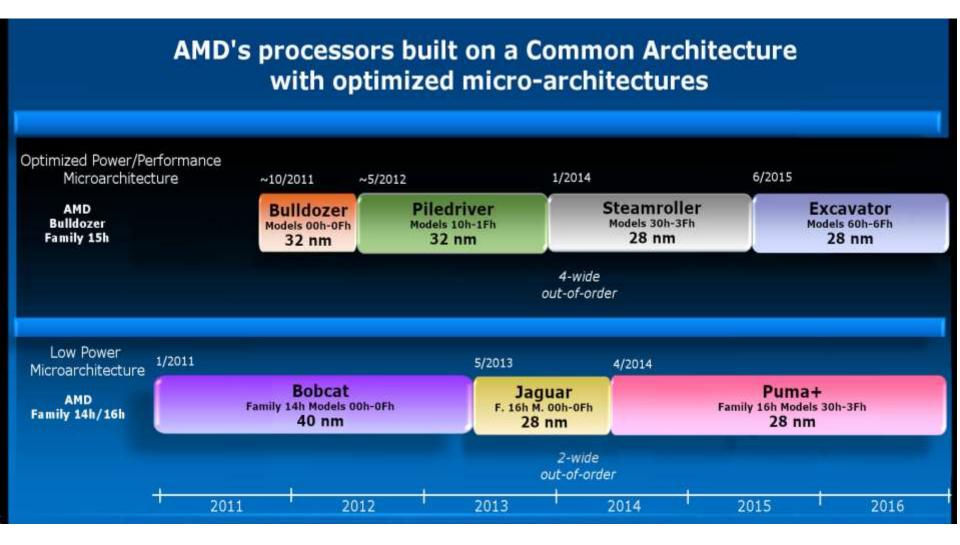

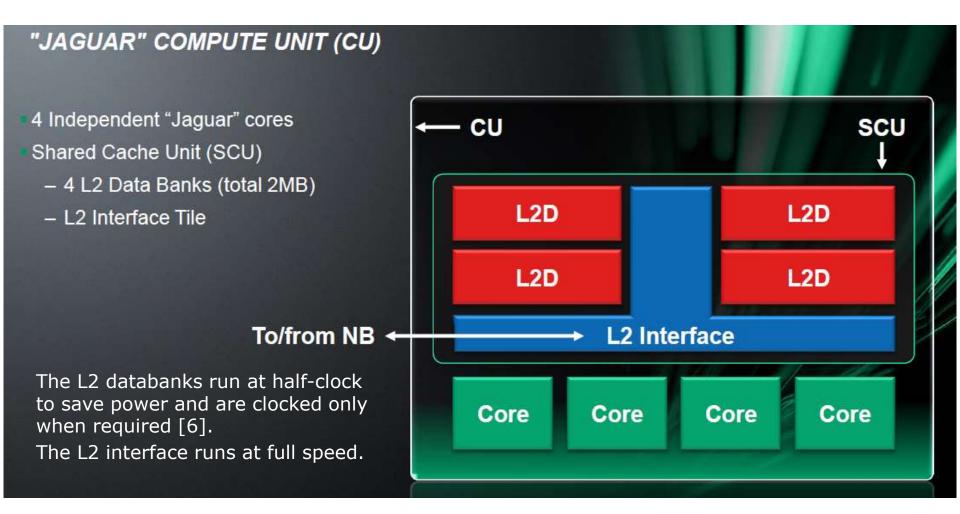

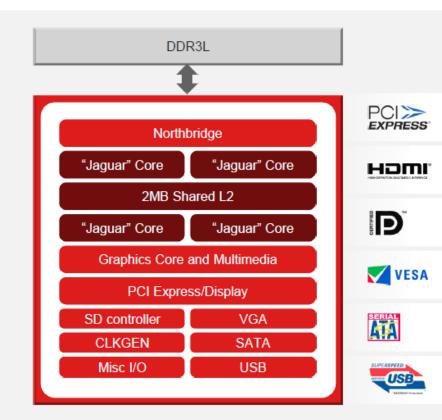

- Jaguar-based APU products include basically up to four Jaguar cores and a GPU with similar capabilities than a low-end discrete graphics card.

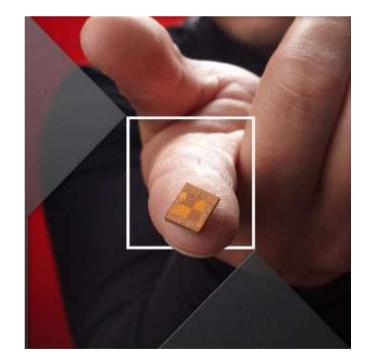

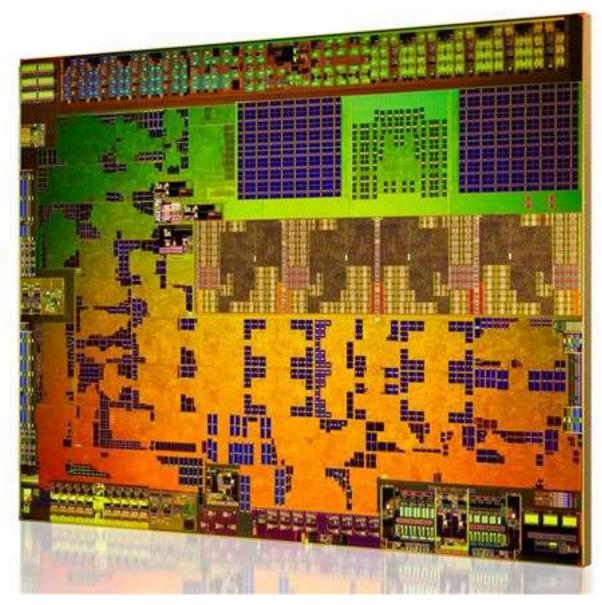

- 28 nm technology, ~ 110 mm<sup>2</sup> die size (compared to 75 mm<sup>2</sup> of Bobcat-based APUs + 28 mm<sup>2</sup> for the associated FCH) [50] and 1178 mtrs (vs. 450 mtrs for Bobcat-based APUs) [51].

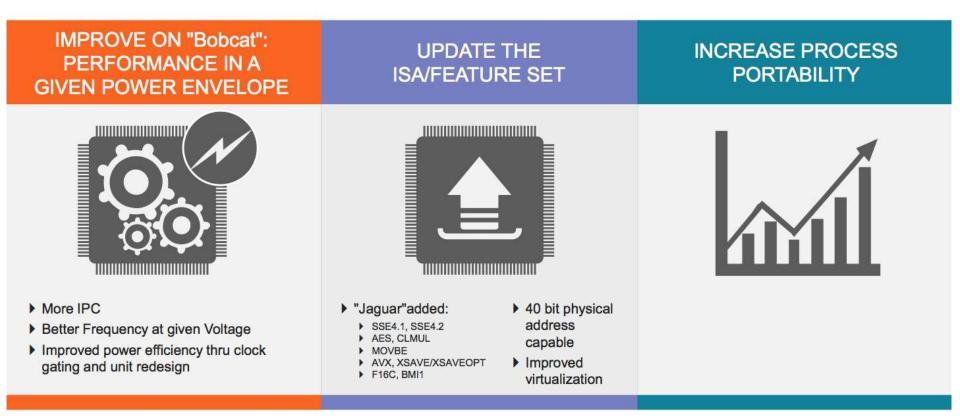

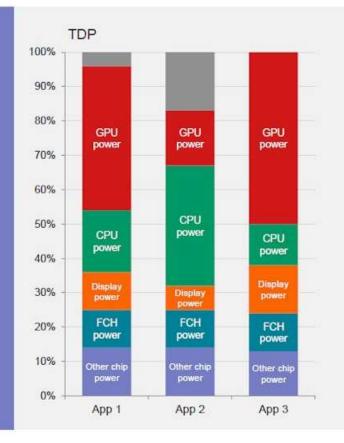

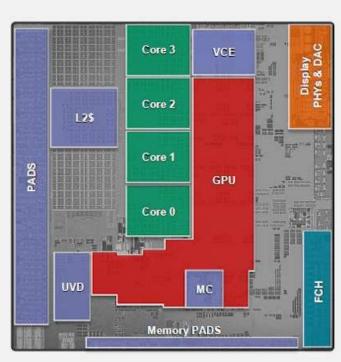

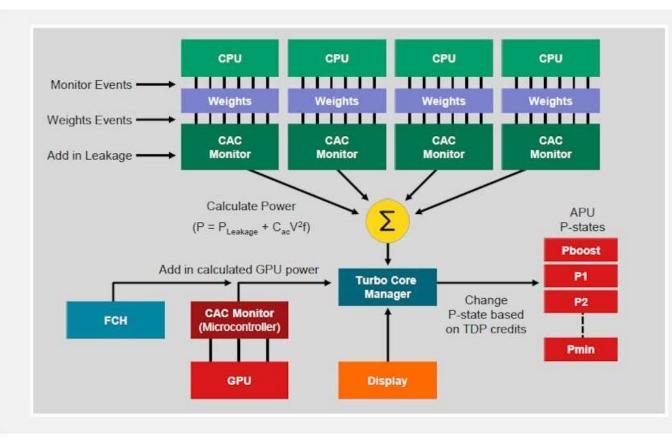

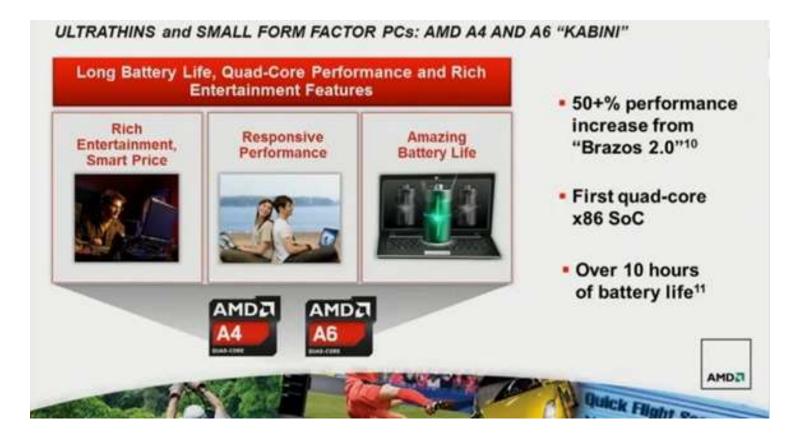

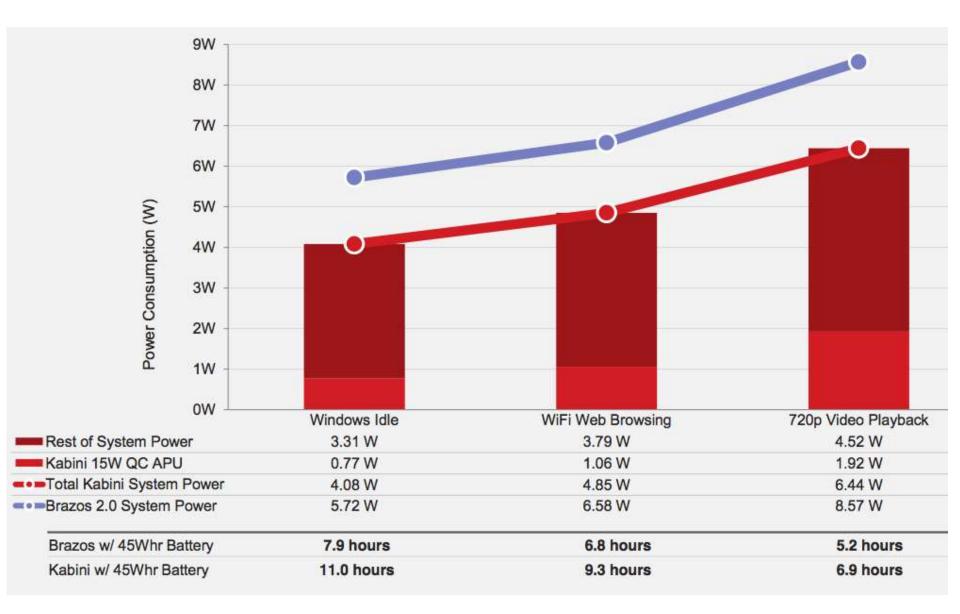

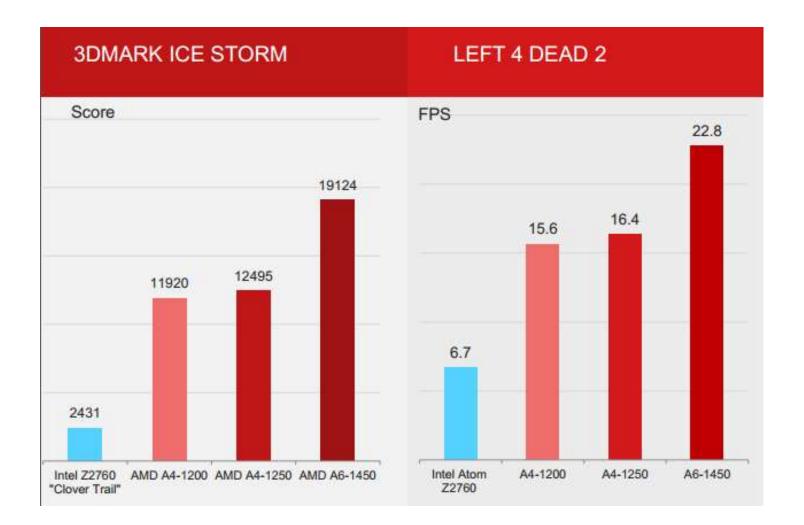

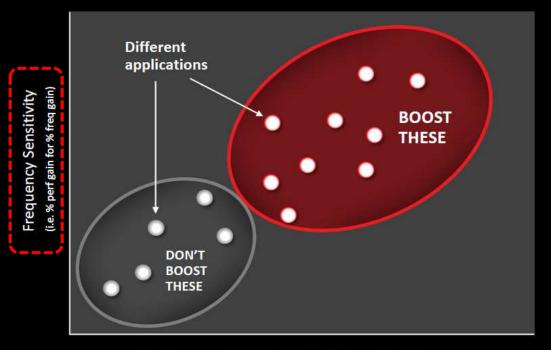

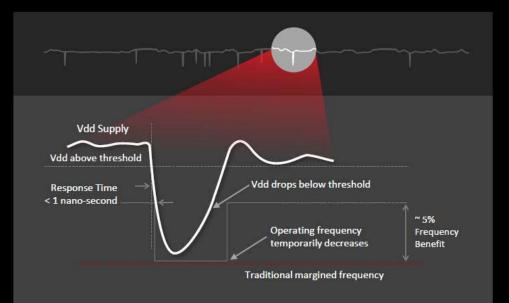

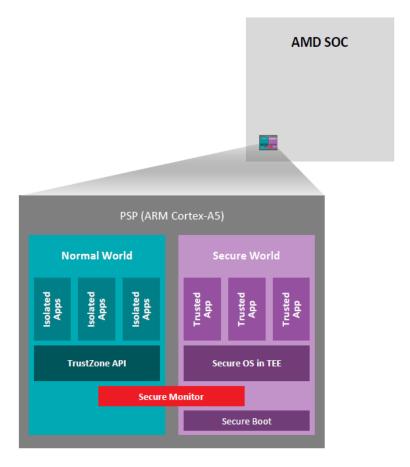

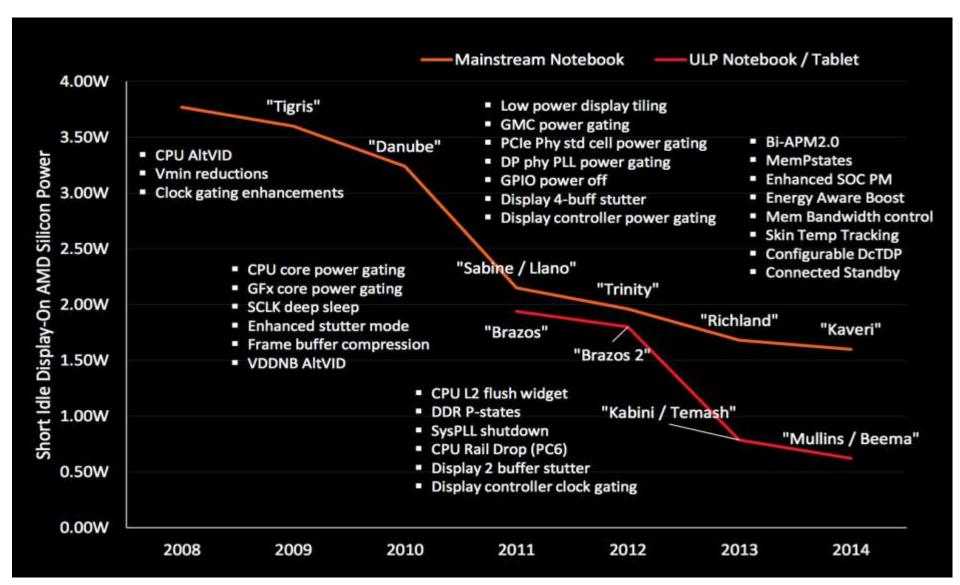

#### **Design goals of the Jaguar-based APU lines** [26]

AMD TECH DAY | MAY 2013 | EMBARGO - MAY 23 2013 12:01 AM EST

Remark

Process portability means the ability of different manufacturers to take the Jaguar design and fabricate it [52].

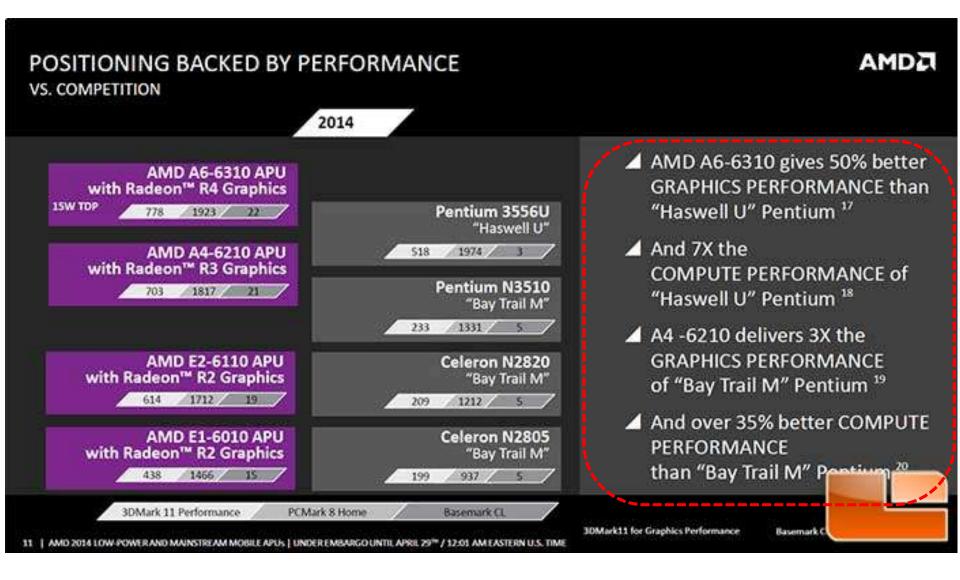

**Positioning the Jaguar-based APU lines** (The Kyoto micro server line not shown)[based on 14]

# Brand names of AMD's Jaguar-based processor lines

|           | Launched in                                         | 2011                                      | 2012                                | 2013                                | 2014                               | 2015                              |

|-----------|-----------------------------------------------------|-------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|-----------------------------------|

|           |                                                     | Family 14h<br>(00h-0Fh)<br>(Bobcat)       | Family 14h<br>(00h-0Fh)<br>(Bobcat) | Family 16h<br>(00h-0Fh)<br>(Jaguar) | Family 16h<br>(30h-3Fh)<br>(Puma+) | Family 16h<br>(30h-3Fh)<br>(Puma+ |

|           | 4P servers                                          |                                           |                                     |                                     |                                    |                                   |

| or S      | 2P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Servers   | 1P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Se        | (85-140 W)                                          |                                           |                                     |                                     |                                    |                                   |

|           | High perf.<br>(~95-125 W)                           |                                           |                                     |                                     |                                    |                                   |

| Desktops  | <b>Mainstream</b><br>(~65-100 W)                    |                                           |                                     |                                     |                                    |                                   |

| Des       | <b>Entry level</b><br>(~30-60 W)                    |                                           |                                     |                                     |                                    |                                   |

| oks       | High performance/<br>mainstream/entry<br>(~30-60 W) |                                           |                                     | Kabini A6                           |                                    |                                   |

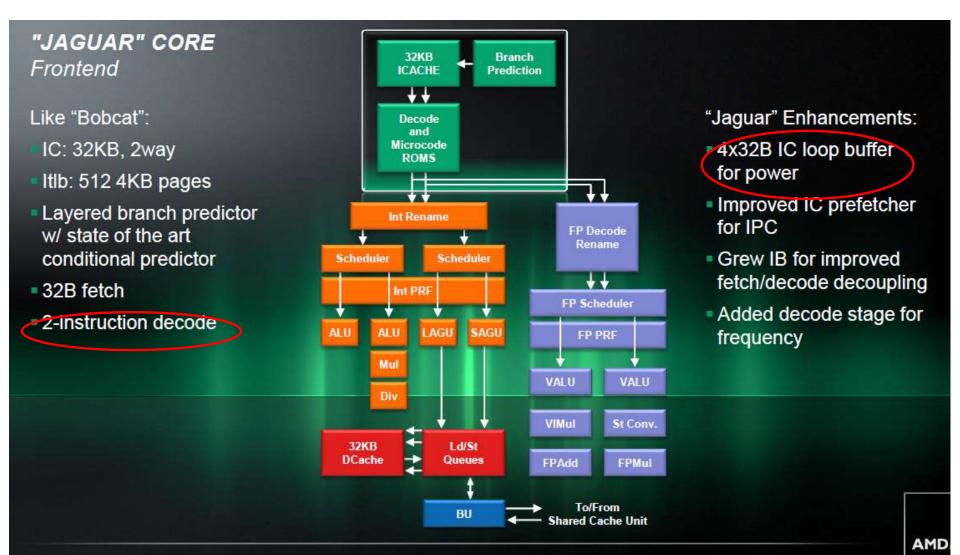

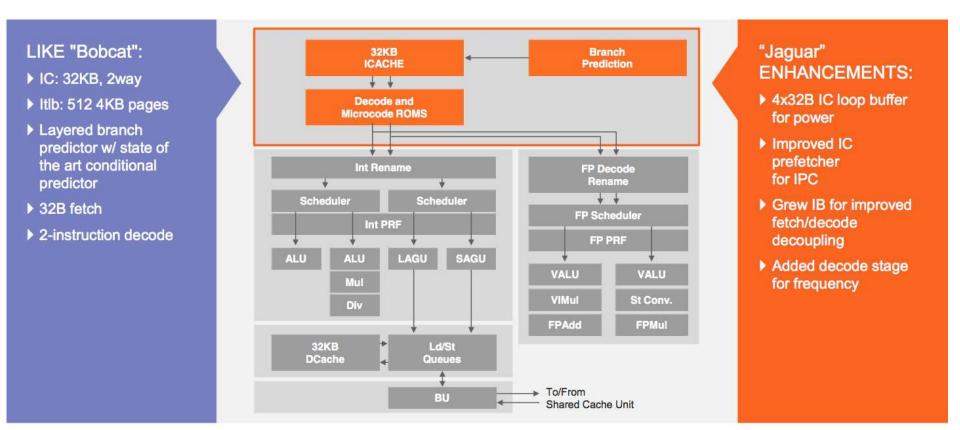

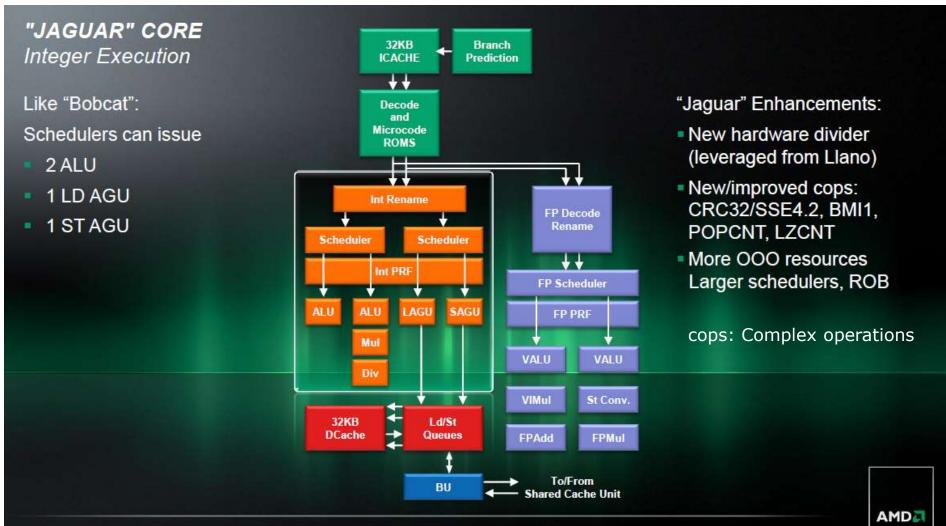

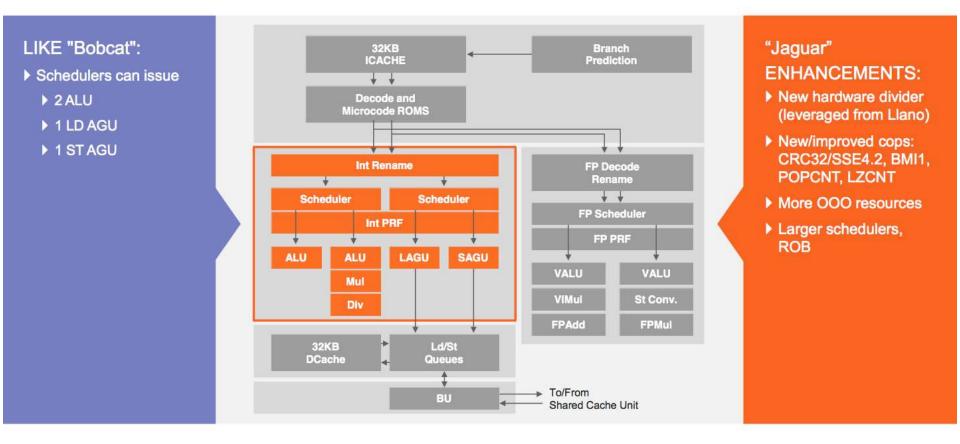

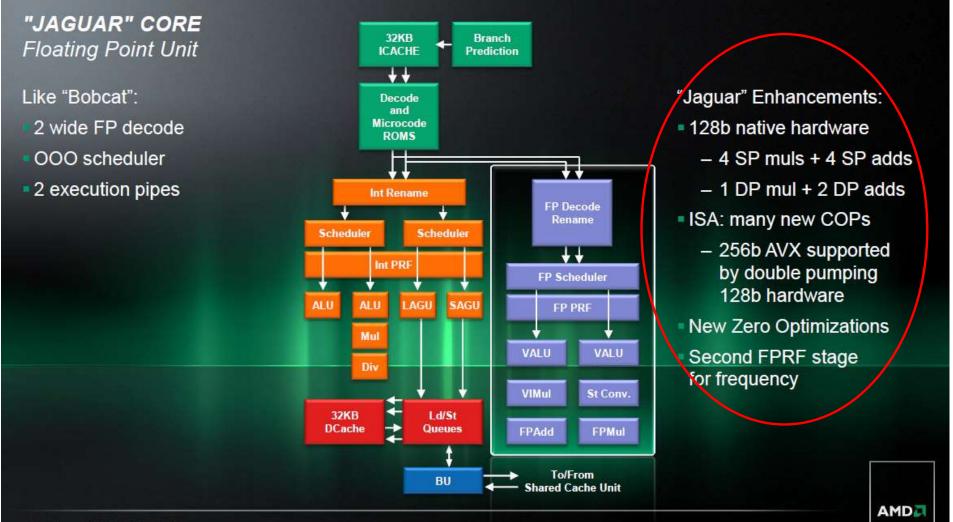

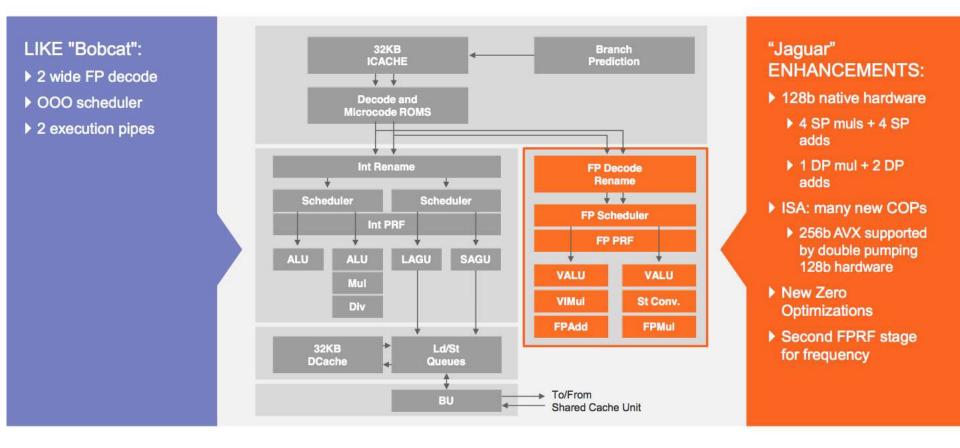

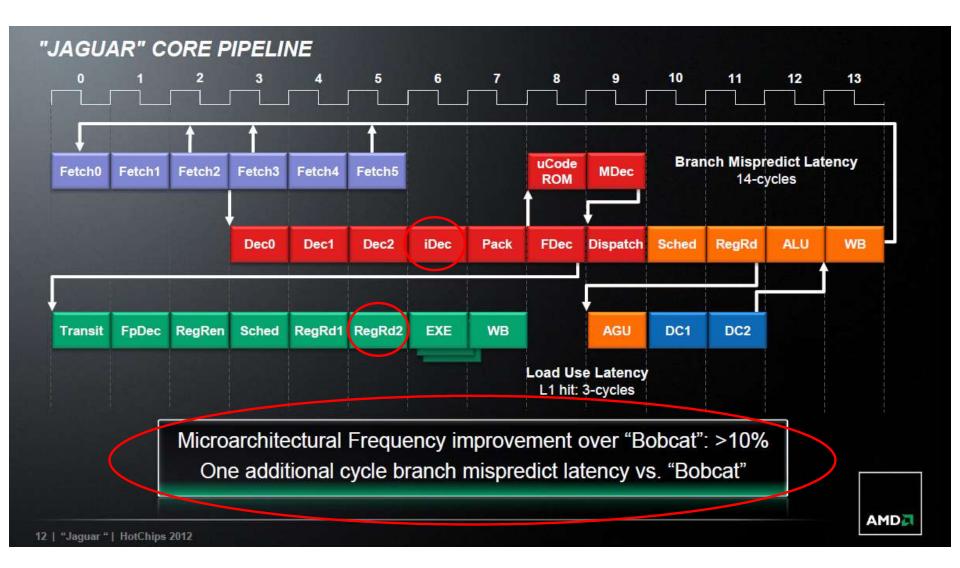

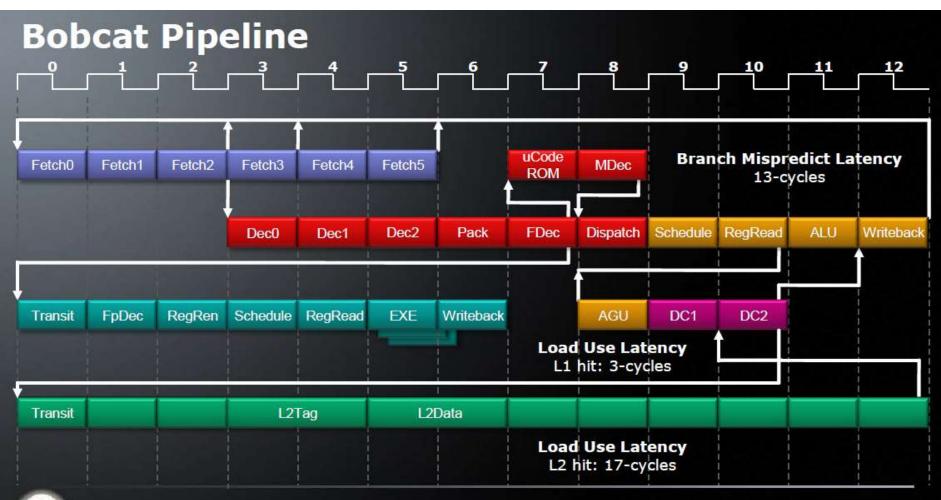

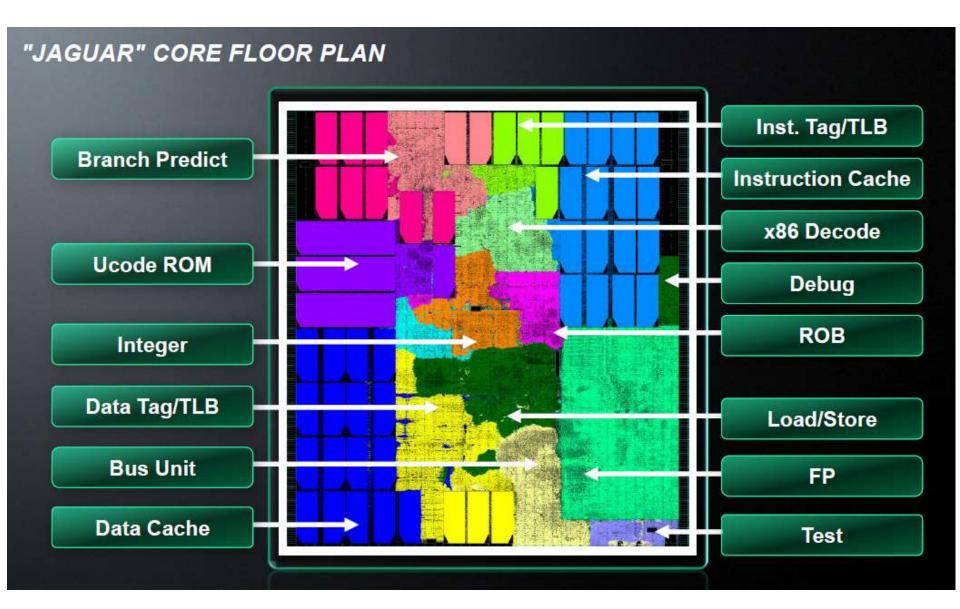

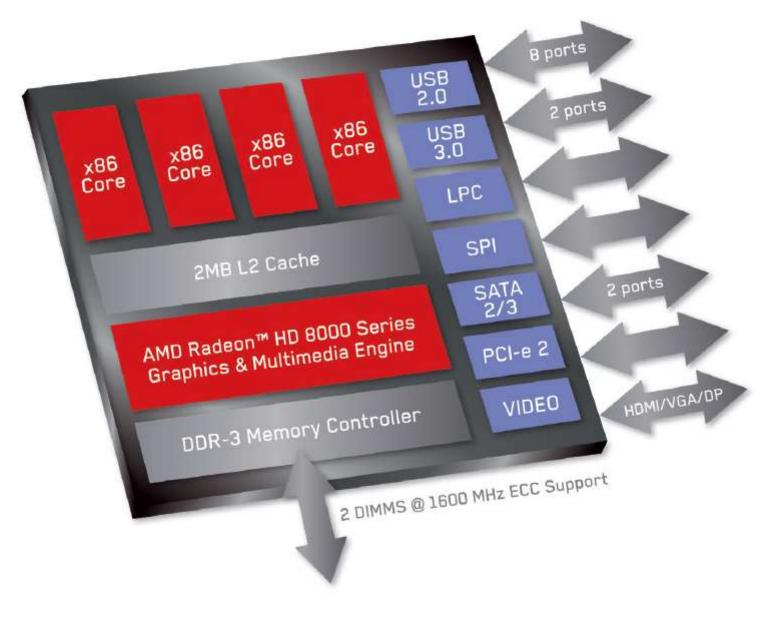

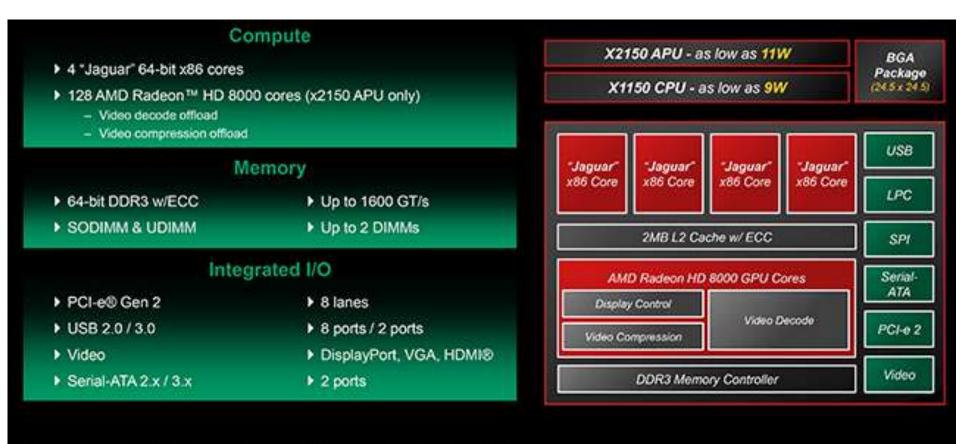

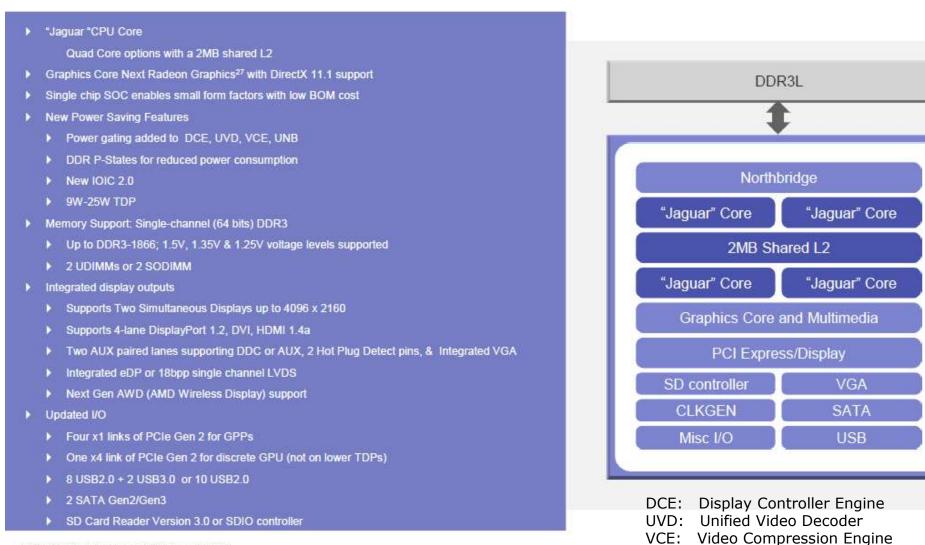

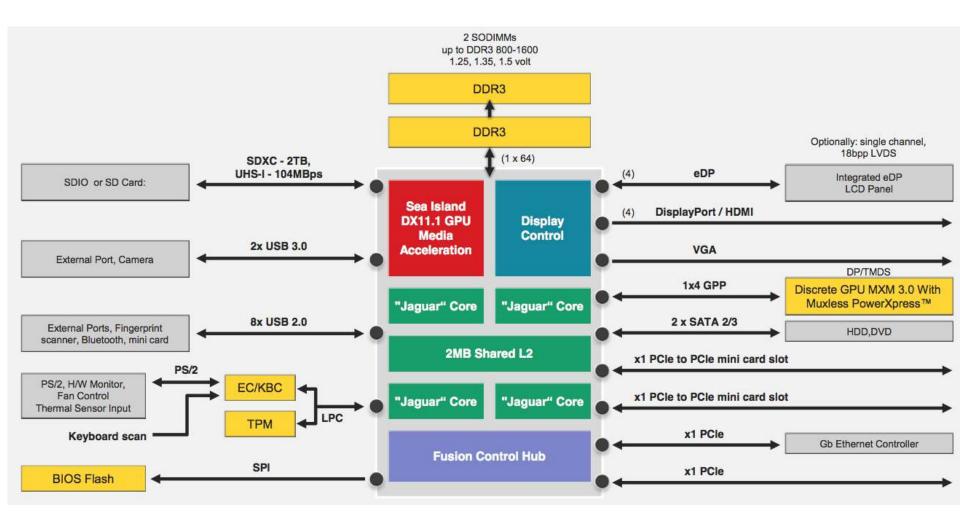

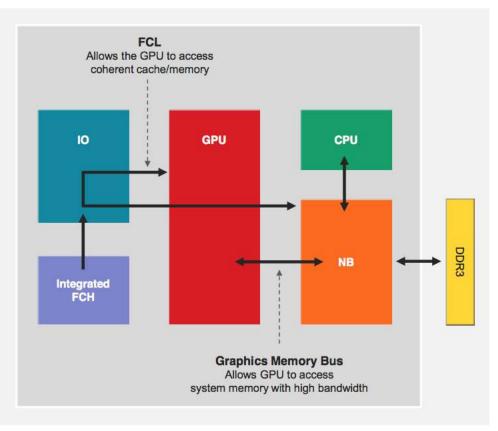

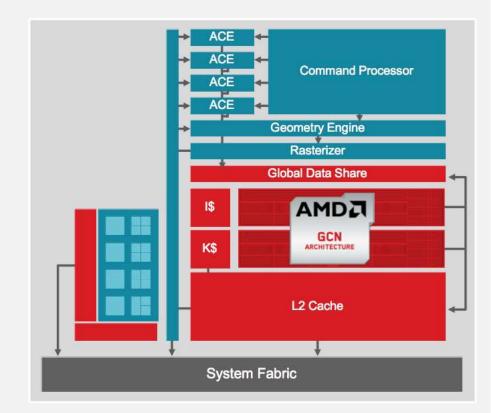

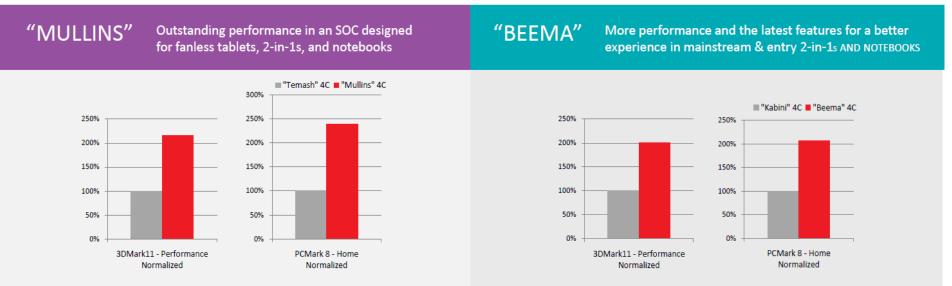

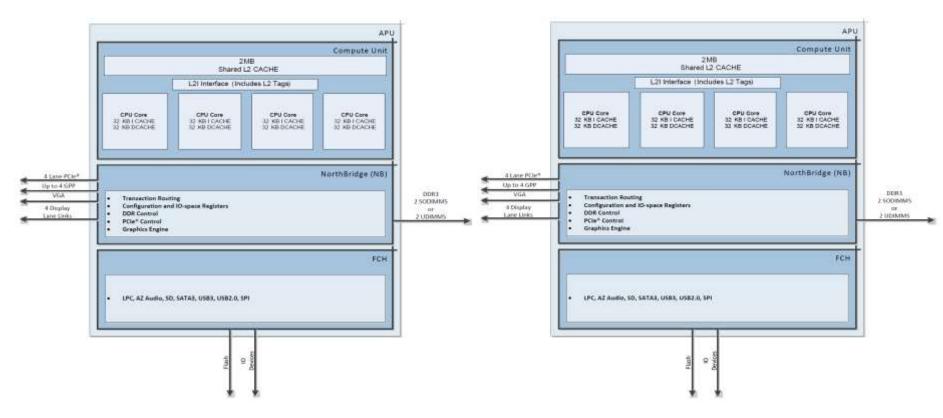

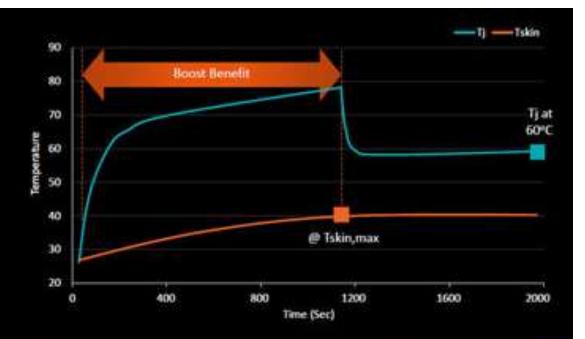

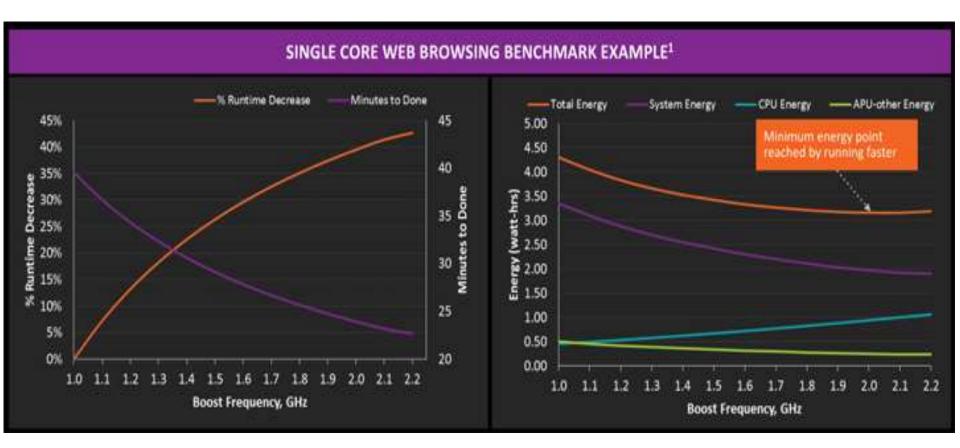

| Notebooks | <b>Ultra portable</b><br>(~10-15 W)                 | Zacate<br>E-Series<br>Ontario<br>C-Series | Zacate<br>E1/E2                     | Kabini<br>A/E-Series                | Beema<br>A/E-Series                | Carrizo-L<br>A/L-Series           |