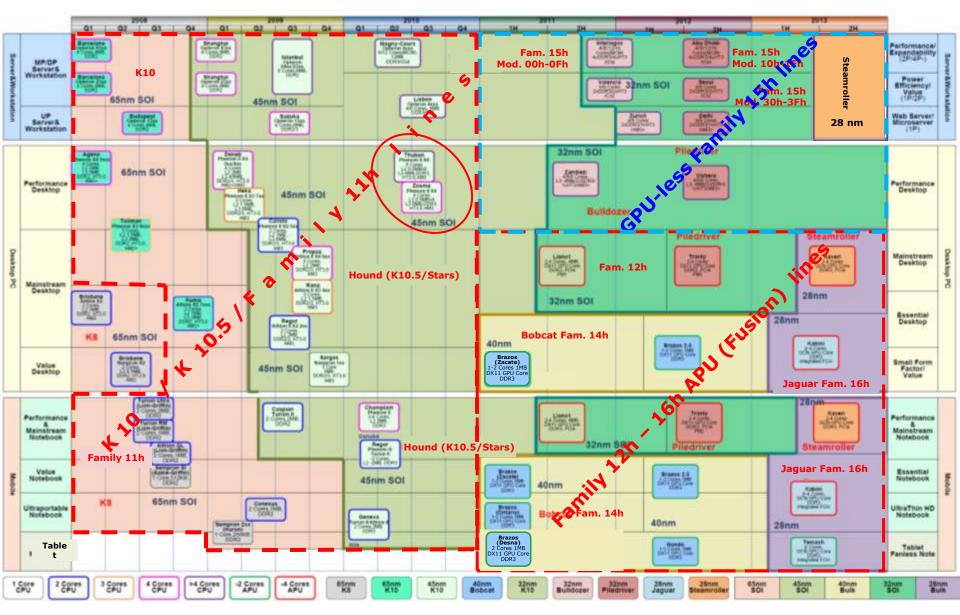

AMD's early processor lines, up to the Hammer Family (Families K8 - K10.5h)

Dezső Sima

October 2018

(Ver. 1.1)

© Sima Dezső, 2018

# AMD's early processor lines, up to the Hammer Family (Families K8 - K10.5h)

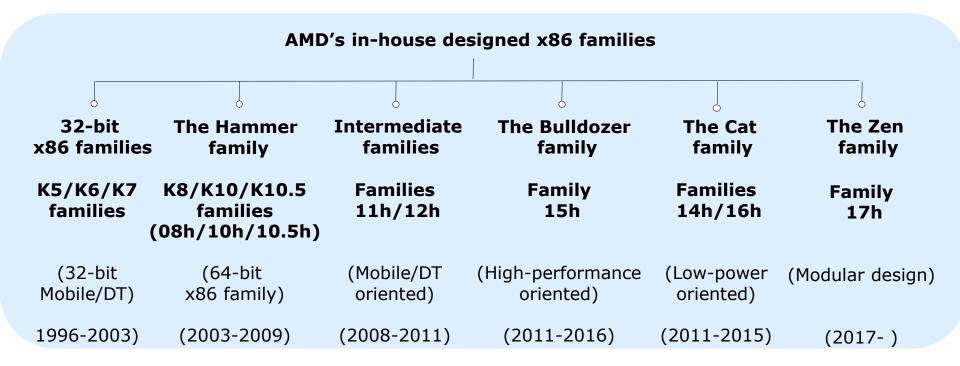

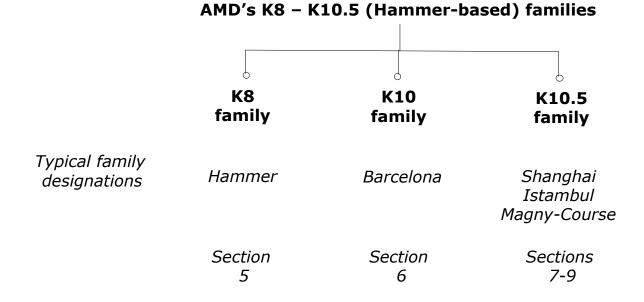

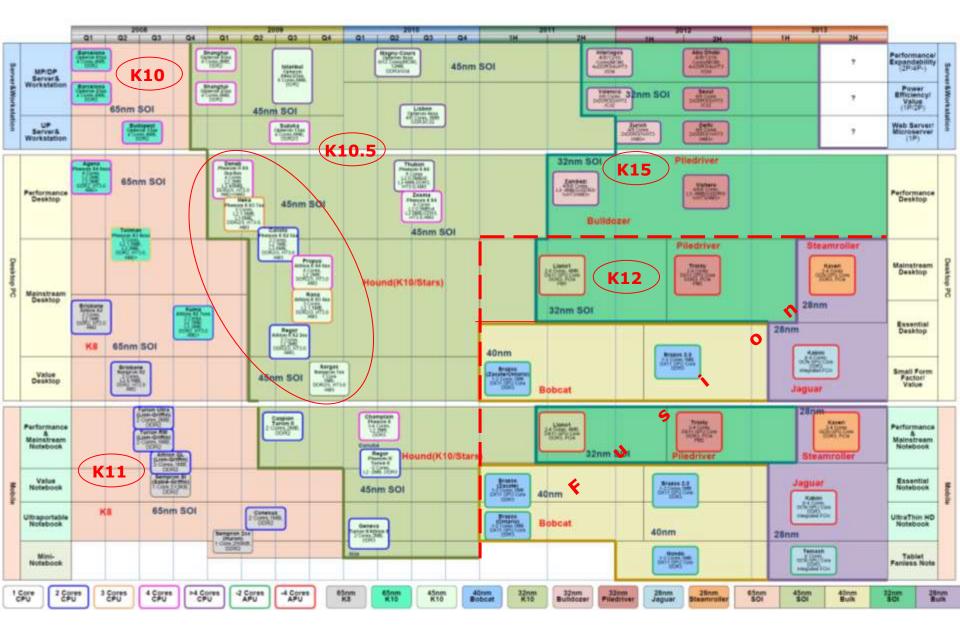

- 1. Introduction to AMD's processor families

- 2. AMD's 32-bit x86 families

- 3. Migration of 32-bit ISAs and microarchitectures to 64-bit

- 4. Overview of AMD's K8 K10.5 (Hammer-based) families

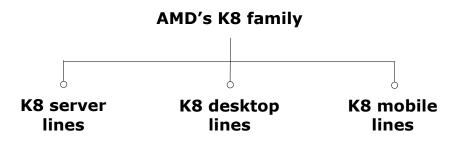

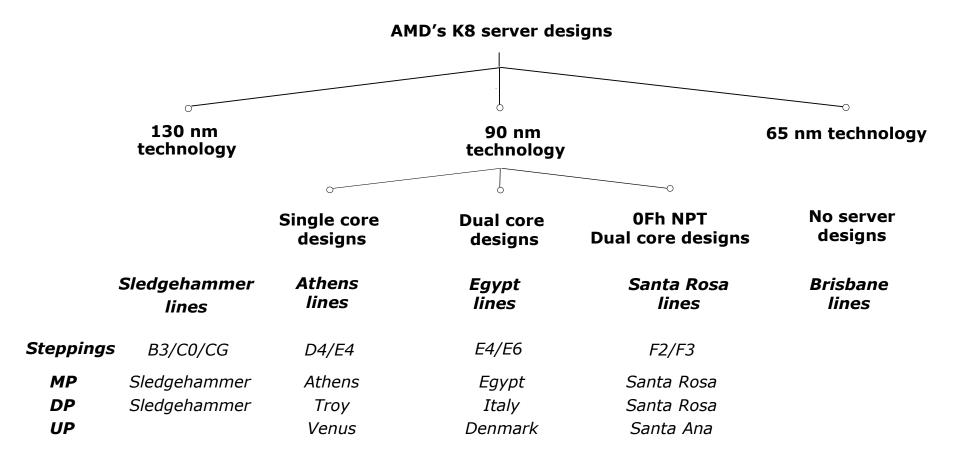

- 5. The K8 (Hammer) family

- 6. The K10 Barcelona family

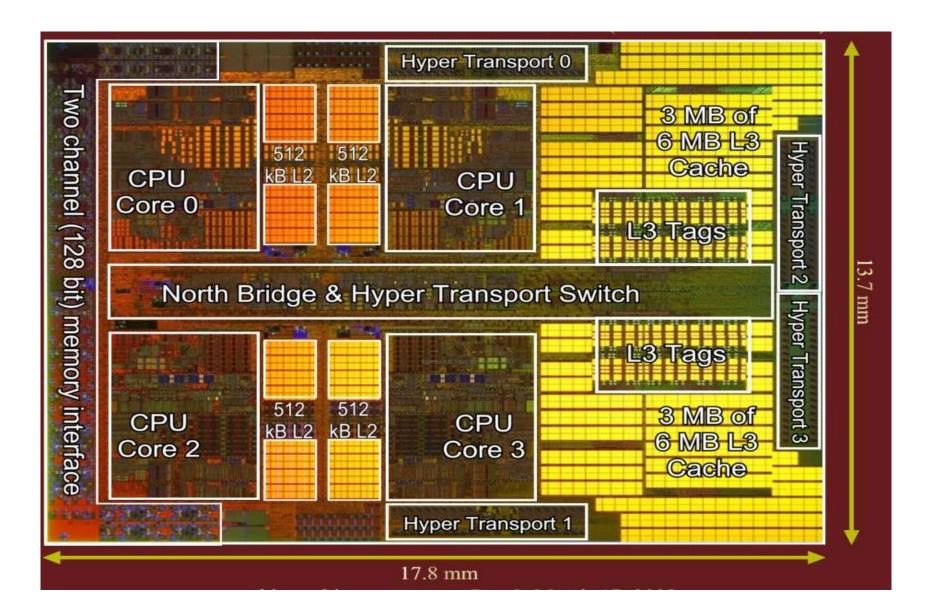

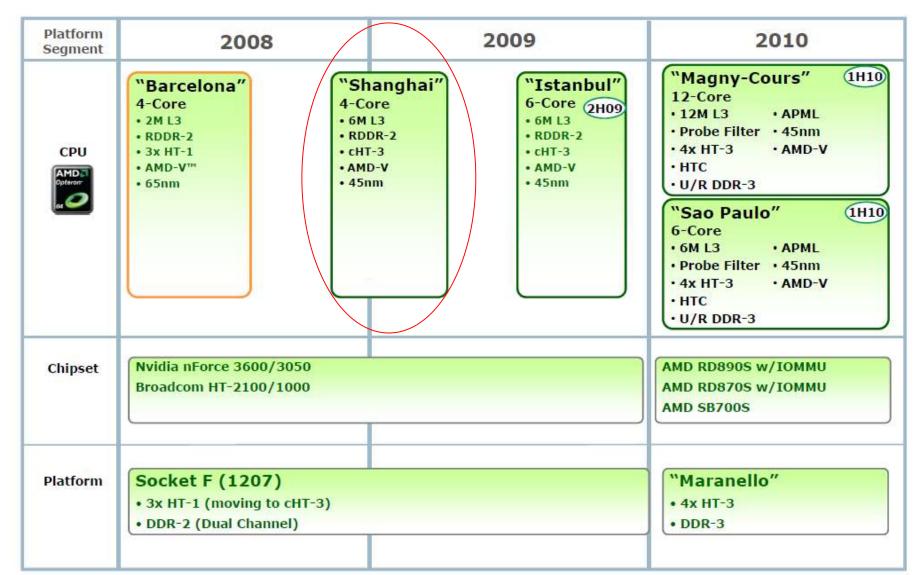

- 7. The K10.5 Shanghai family

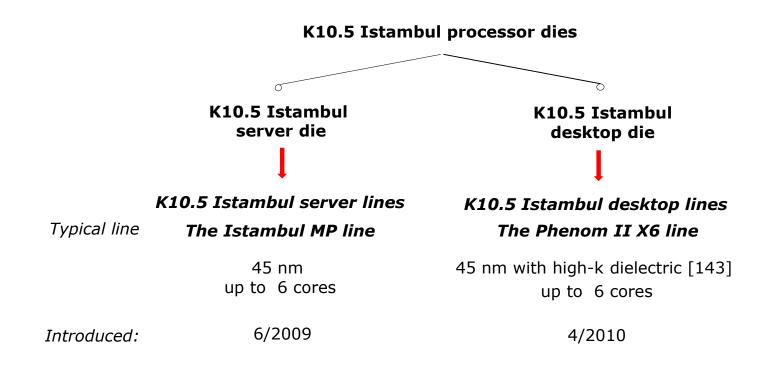

- 8. The K10.5 Istambul family

- 9. The K10.5-based Magny-Course/Lisbon family

- 10. References

1. Introduction to AMD's processor families

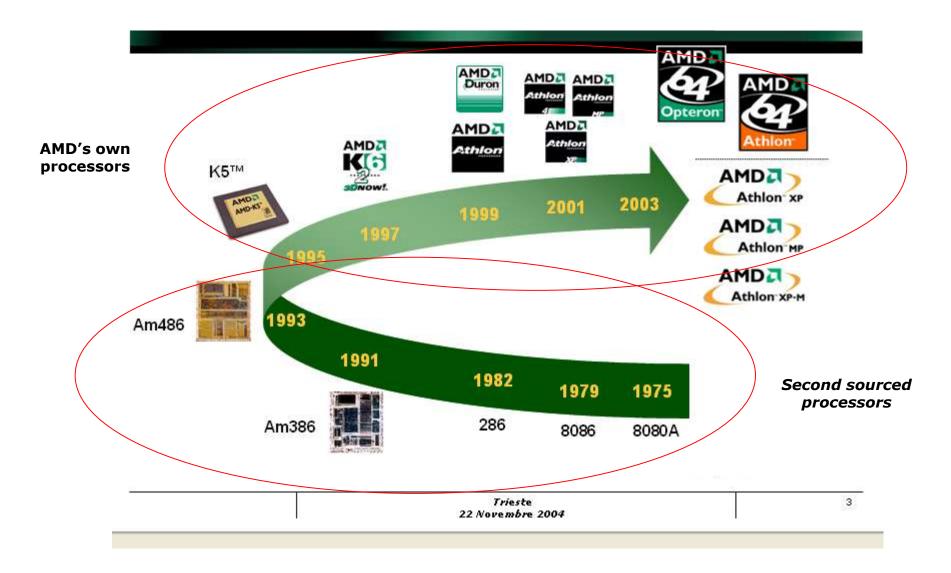

**1. Introduction to AMD's processor families AMD's early x86 processor history** [1]

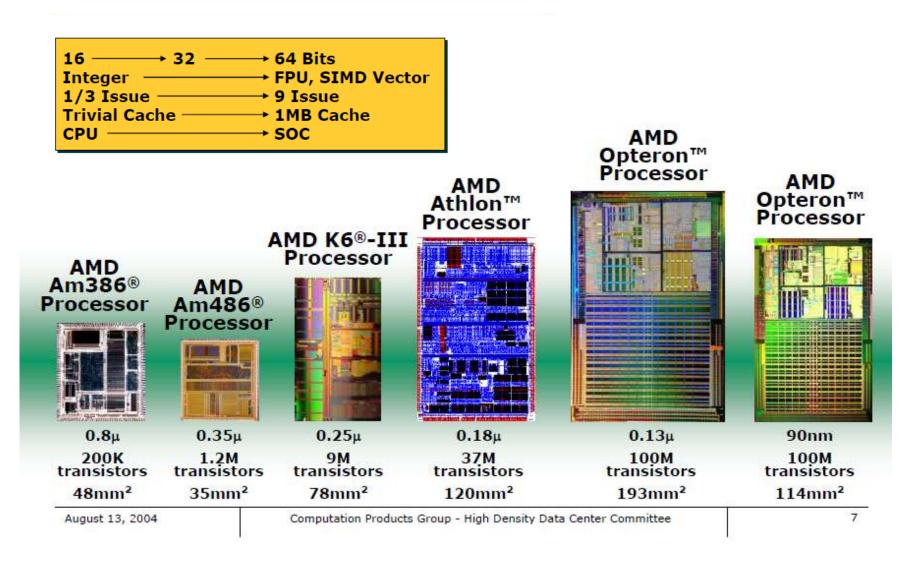

#### **Evolution of AMD's early processors** [2]

# **Historical remarks**

1) Beyond x86 processors AMD also designed and marketed two embedded processor families;

- the 2900 family of bipolar, 4-bit slice microprocessors (1975-?) used in a number of processors, such as particular DEC 11 family models, and

- the 29000 family (29K family) of CMOS, 32-bit embedded microcontrollers (1987-95).

In late 1995 AMD cancelled their 29K family development and transferred the related design team to the firm's K5 effort, in order to focus on x86 processors [3].

2) Initially, AMD designed the Am386/486 processors that were clones of Intel's processors.

- 3) Then the K5 was AMD's first in-house designed processor.

- 4) The K6 was originally developed by NexGen, a firm that AMD purchased in 1995. This processor was pin-compatible with Intel's Pentium. Subsequent K6 models became competitive with Intel's Pentium II/III.

# The K and Family xxh nomenclature of AMD's processor families

- The K designation used previously by AMD is a counterpart of Intel's P designation for their processor families.

- It was inspired by comic books, since Kryptonite was the only substance that could bring Superman to knees. Obviously, Superman stays for Intel [4].

- Presumably, a similar inspiration is behind AMD's core names such as Sledgehammer, Clawhammer, or even Bulldozer and its successors including Piledriver, Steamroller etc.

- In Nov. 2004 AMD abandoned using the K moniker for their basic architectures in order to signalize their move to enter a wide variety of markets and started to use their own in-house Family xxh designations.

- Nevertheless, outside AMD the K designation was used further on for simplicity and clarity more or less until arriving the Family 11h (Griffin-based) lines.

- In this chapter we will also make use of the K nomenclature including the K10.5 family and will change to the Family 1xh designation beginning with the Family 11h (Griffin-based).

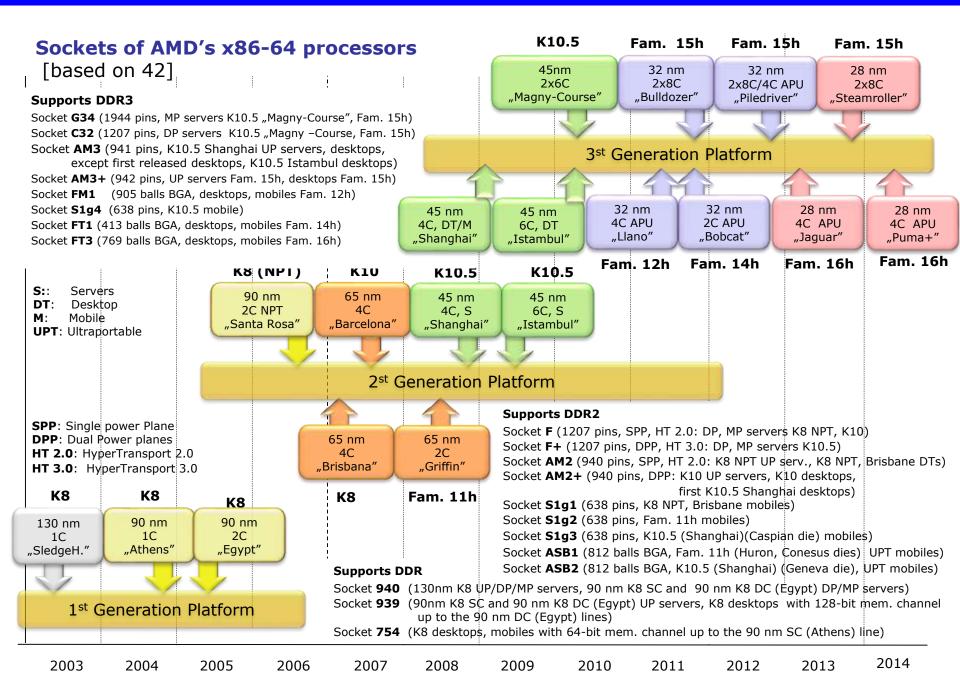

# AMD's x86-64 family designations and related main features

| FamilyE      | Intro. | Core                                               | Techn.<br>(nm) | Used<br>typically in           | Core<br>contr. | Market<br>segment |

|--------------|--------|----------------------------------------------------|----------------|--------------------------------|----------------|-------------------|

|              | 2003   | Sledghammer                                        | 130            | Sledgehammer                   | 1              | S, DT, M          |

| F0h<br>(K8)  | 2004   | Athens                                             | 90             | Athens                         | 1              | S, DT, M          |

|              | 2005   | Egypt                                              | 90             | Egzpt                          | 2              | S, DT, M          |

| 0Fh NPT (K8) | 2006   | Hammer                                             | 90             | Santa Rose                     | 2              | S, DT, M          |

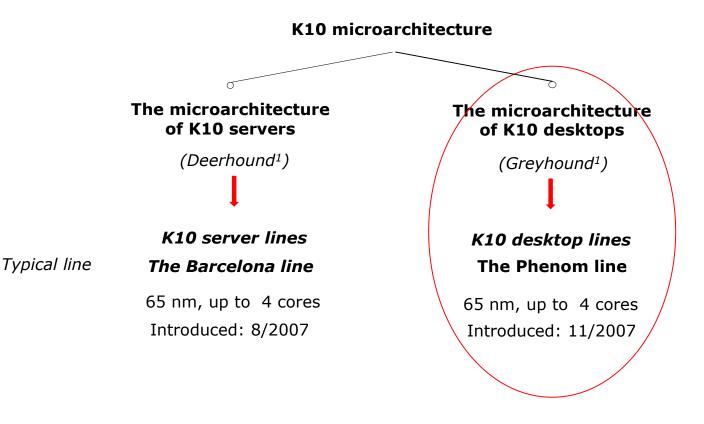

|              | 2007   | Greyhound                                          | 65             | Barcelona                      | 4              | S, DT             |

|              | 2008   |                                                    | 45             | Shanghai                       | 4              | S, DT, M          |

| 10h          | 2009   | Greyhound+                                         |                | Istambul                       | 6              | S, DT             |

|              | 2010   |                                                    |                | Magny Course                   | 2*6            | S                 |

| 11h          | 2008   | Griffin                                            | 65             | Lion                           | 2              | DT, M             |

| 12h          | 2011   | Husky (Liano)                                      | 32             | Fusion A/E2                    | 4+ GPU         | DT, M             |

| 14h          | 2011   | Bobcat                                             | 40             | Fusion C/E/G/Z                 | 2 + GPU        | М                 |

| 15h          | 2011   | Bulldozer/Piledriver/<br>Steamroller/<br>Excavator | 32             | Interlagos (S)<br>Zambezi (DT) | 2*8<br>8       | S, DT             |

| 16h          | 2012   | Jaguar/Puma+                                       | 28             | Fusion C/E/G/Z                 | 2 + GPU        | М                 |

| 17h          | 2017   | Zen                                                |                | EPYC/ThreadRipper/<br>Ryzen    | 8/16/32        | S, DT, M          |

S: Server DT: Desktop M: Mobile

## **Brand names of AMD's processor lines**

AMD typically, assigns unique brand names to their processor lines that indicate

- the processor famiy

- market segment and

- relative performance

the particular processor line supports.

# Main market segments

- AMD strives to cover main market segments.

- Salient market segments vary however, temporally.

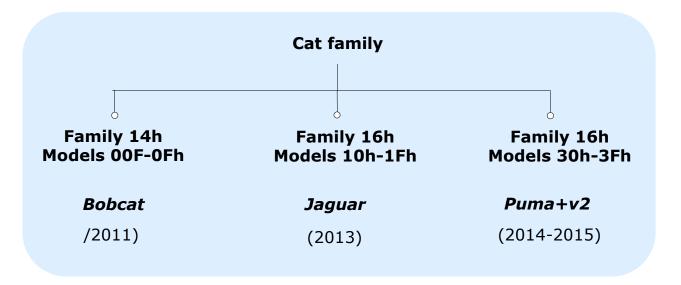

- Concerning this, AMD designed and marketed a low-power oriented processor family, targeting tablets and smart phones, the Cat family, in the first halve of the 2010's (between 2011 and 2015).

Nevertheless, the Cat family was not successful and AMD cancelled the Cat line in 2015.

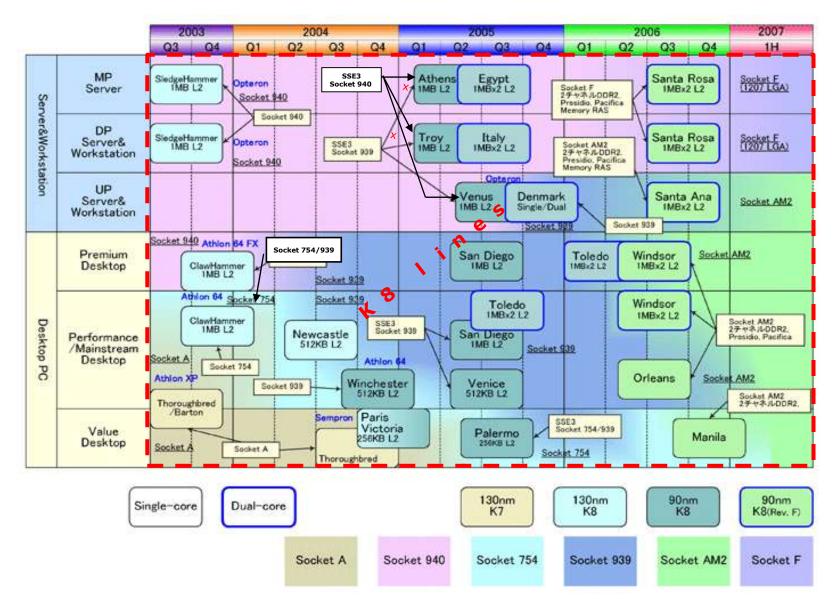

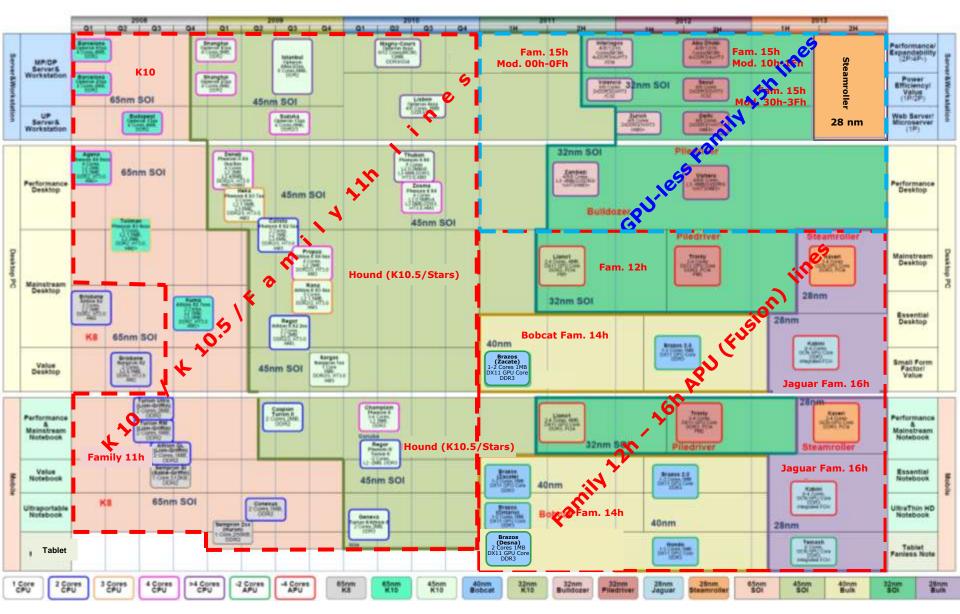

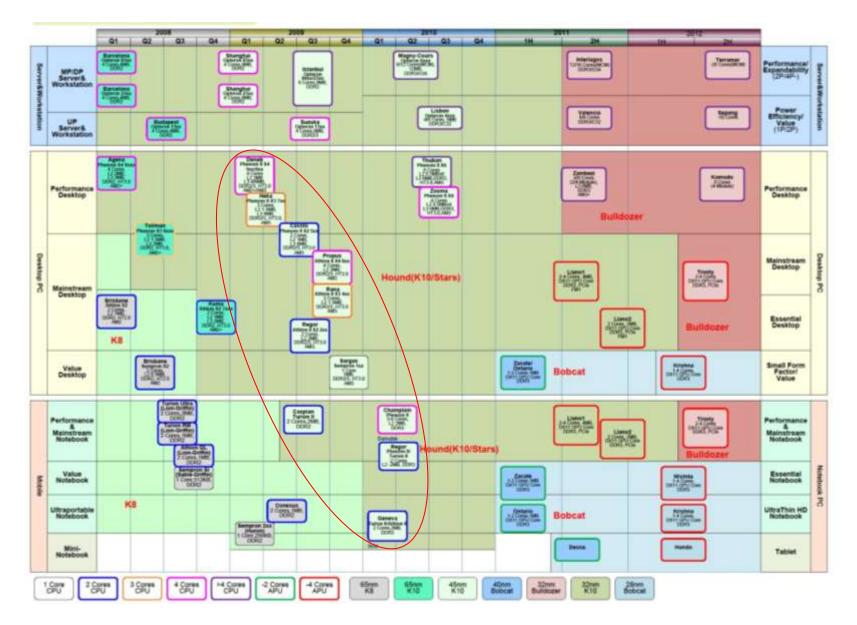

As an example for the main market segments, the next Figure shows AMD's market segments favored in their Hammer family (K8 to K10,5), that is

- servers

- desktops and

- mobiles.

- Obviously, AMD's different processor families emphasize different market segments.

# **Example for main market segments in AMD's K8 – K10.5h processor lines**

|                       |                            | 2003-2007                                                  | 2007-2008                 | 2008-2011                                                                     | 2009                    | 2009                     |

|-----------------------|----------------------------|------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------|-------------------------|--------------------------|

|                       |                            | K8<br>(Hammer)                                             | K10<br>(Barcelona)        | K10.5<br>(Shanghai)                                                           | K10.5<br>(Istanbul)     | K10.5<br>(Magny- Course) |

| r s                   | 4P servers                 |                                                            | Barcelona<br>(834x-836x)) | Shanghai<br>(837x-839x)                                                       | lstambul<br>(8410-8430) | Magny-Course<br>(6100)   |

| r v e                 | 2P servers                 | See Section 4                                              | Barcelona<br>(234x-236x)  | Shanghai<br>(237x-239x)                                                       | lstambul<br>(241x-243x) | Lisbon<br>(4100)         |

| Se                    | 1P servers                 |                                                            | Budapest<br>(135x-136x)   | Suzuka<br>(138x-139x)                                                         |                         |                          |

| o p s                 | High perf.<br>(~80-120W)   |                                                            | Phenom<br>X4-X2           | Phenom II<br>X4-X2                                                            | Phenom II<br>X6-X4      |                          |

| skto                  | Mainstream<br>(~60-90W)    | Athlon 64<br>Athlon 64 X2                                  | Athlon X2                 | Athlon II X4-X2                                                               |                         |                          |

| De                    | <b>Value</b><br>(~40-60W)  | Sempron                                                    |                           | Sempron                                                                       |                         |                          |

| S                     | High perf.<br>(~30-40W)    | Turion 64 X2<br>(TL 6/5)<br>Turion 64 (ML/MT)              |                           | Phenom II<br>(N/P 9xx-6xx)<br>Turion II Ultra (M6xx)<br>Turion II (M/N/P 5xx) |                         |                          |

| Mobile                | Mainstream<br>(~20-30W)    | Athlon 64 X2<br>(TK-5x/4x)<br>Athlon 64<br>(2xxx+-4xxx+)   |                           | Athlon II (M/N/P 3xx)<br>Sempron (M1xx)                                       |                         |                          |

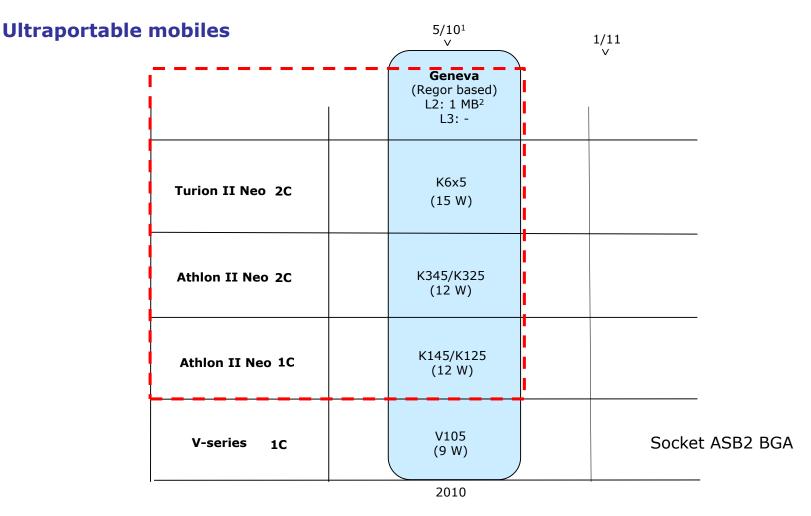

|                       | Ultraportable<br>(~10-20W) | Mobile Sempron<br>(2xxx+-4xxx+)<br>Sempron 2100<br>fanless |                           | Turion II Neo (K6xx)<br>Athlon II Neo (K1xx)<br>V-series (V1xx)               |                         |                          |

| Embedded<br>(~10-20W) |                            |                                                            |                           | Turion II Neo X2<br>Athlon II Neo X2<br>Athlon II Neo                         |                         |                          |

## **Performance classes within market segments**

Typically, in each market segment processor lines are broken down into performance classes, indicating the relative performance of the processor lines within a particular market segment, like

- high performance desktops

- mainstream desktops and

- value desktops,

as shown below again for the Hammer family (K8 – K10.5) for the desktop lines.

# Example for performance classes within the desktop segment in AMD's K8 – K10.5h lines

|             |                                | 2003-2007                                                                             | 2007-2008                 | 2008-2011                                                                  | 2009                    | 2009                     |

|-------------|--------------------------------|---------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|-------------------------|--------------------------|

|             |                                | K8<br>(Hammer)                                                                        | K10<br>(Barcelona)        | K10.5<br>(Shanghai)                                                        | K10.5<br>(Istanbul)     | K10.5<br>(Magny- Course) |

| L S         | 4P servers                     |                                                                                       | Barcelona<br>(834x-836x)) | Shanghai<br>(837x-839x)                                                    | Istambul<br>(8410-8430) | Magny-Course<br>(6100)   |

| rve         | 2P servers                     | See Section 4                                                                         | Barcelona<br>(234x-236x)  | Shanghai<br>(237x-239x)                                                    | lstambul<br>(241x-243x) | Lisbon<br>(4100)         |

| Se          | 1P servers                     |                                                                                       | Budapest<br>(135x-136x)   | Suzuka<br>(138x-139x)                                                      |                         |                          |

| o p s       | High perf.<br>(~80-120W)       |                                                                                       | Phenom<br>X4-X2           | Phenom II<br>X4-X2                                                         | Phenom II<br>X6-X4      |                          |

| skto        | Mainstream<br>(~60-90W)        | Athlon 64<br>Athlon 64 X2                                                             | Athlon X2                 | Athlon II X4-X2                                                            |                         |                          |

| De          | <b>Value</b><br>(~40-60W)      | Sempron                                                                               |                           | Sempron                                                                    |                         |                          |

|             | <b>High perf.</b><br>(~30-40W) | Turion 64 X2<br>(TL 6/5)<br>Turion 64 (ML/MT)                                         |                           | Phenom II (N/P 9xx-6xx)<br>Turion II Ultra (M6xx)<br>Turion II (M/N/P 5xx) |                         |                          |

| o b I l e s | Mainstream<br>(~20-30W)        | Athlon 64 X2 (TK-5x/4x)<br>Athlon 64 (2xxx+-4xxx+)<br>Mobile Sempron<br>(2xxx+-4xxx+) |                           | Athlon II (M/N/P 3xx)<br>Sempron (M1xx)                                    |                         |                          |

| ο<br>Μ      | Ultraportable<br>(~10-20W)     | Sempron 2100 fanless                                                                  |                           | Turion II Neo (K6xx)<br>Athlon II Neo (K1xx)<br>V-series (V1xx)            |                         |                          |

|             | <b>Embedded</b><br>(~10-20W)   |                                                                                       |                           | Turion II Neo X2<br>Athlon II Neo X2<br>Athlon II Neo                      |                         |                          |

### **Brand names of AMD's processor lines**

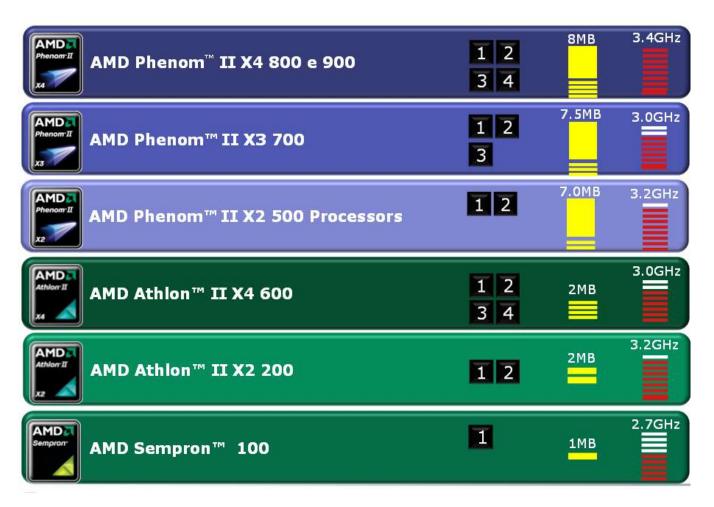

As an example, the next Figure shows brand names of K10.5 Shanghai based desktop processor lines of different performance potentials, such as:

- Phenom II

- Athlon II and

- Sempron.

# Brand names of AMD's 64-bit K8 – Family 10.5h processor lines

|                       |                                | 2003-2007                                                  | 2007-2008                 | 2008-2011                                                                     | 2009                    | 2009                     |

|-----------------------|--------------------------------|------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------|-------------------------|--------------------------|

|                       |                                | K8<br>(Hammer)                                             | K10<br>(Barcelona)        | K10.5<br>(Shanghai)                                                           | K10.5<br>(Istanbul)     | K10.5<br>(Magny- Course) |

| r s                   | 4P servers                     |                                                            | Barcelona<br>(834x-836x)) | Shanghai<br>(837x-839x)                                                       | lstambul<br>(8410-8430) | Magny-Course<br>(6100)   |

| r v e                 | 2P servers                     | See Section 4                                              | Barcelona<br>(234x-236x)  | Shanghai<br>(237x-239x)                                                       | lstambul<br>(241x-243x) | Lisbon<br>(4100)         |

| S<br>e                | 1P servers                     |                                                            | Budapest<br>(135x-136x)   | Suzuka<br>(138x-139x)                                                         |                         |                          |

| s d o                 | High perf.<br>(~80-120W)       |                                                            | Phenom<br>X4-X2           | Phenom II<br>X4-X2                                                            | Phenom II<br>X6-X4      |                          |

| skto                  | Mainstream<br>(~60-90W)        | Athlon 64<br>Athlon 64 X2                                  | Athlon X2                 | Athlon II X4-X2                                                               |                         |                          |

| De                    | <b>Value</b><br>(~40-60W)      | Sempron                                                    |                           | Sempron                                                                       |                         |                          |

| e s                   | <b>High perf.</b><br>(~30-40W) | Turion 64 X2<br>(TL 6/5)<br>Turion 64 (ML/MT)              |                           | Phenom II<br>(N/P 9xx-6xx)<br>Turion II Ultra (M6xx)<br>Turion II (M/N/P 5xx) |                         |                          |

| Mobil                 | Mainstream<br>(~20-30W)        | Athlon 64 X2<br>(TK-5x/4x)<br>Athlon 64<br>(2xxx+-4xxx+)   |                           | Athlon II (M/N/P 3xx)<br>Sempron (M1xx)                                       |                         |                          |

|                       | Ultraportable<br>(~10-20W)     | Mobile Sempron<br>(2xxx+-4xxx+)<br>Sempron 2100<br>fanless |                           | Turion II Neo (K6xx)<br>Athlon II Neo (K1xx)<br>V-series (V1xx)               |                         |                          |

| Embedded<br>(~10-20W) |                                |                                                            |                           | Turion II Neo X2<br>Athlon II Neo X2<br>Athlon II Neo                         |                         |                          |

# Model designations within a processor line

In addition to the brand names model designations differentiate particular models of a processor line.

Model designations

- may include a tag, such as X2 or X4 that indicates the number of cores (e.g. X2 meaning dual cores etc.) and

- a model number that specifies the features of the processor, such as the clock frequency, L2 or L3 cache size, wattage (dissipation etc.) as shown in an example given for the K10.5 Shanghai based Phenom II X3 7xx line in the next table.

# 1. Introduction to AMD's processor families (14)

# Example: Processor model designations of the Phenom II X3 line (Desktop line based on the K10.5 Shanghai derived Deneb core) [5]

| Model Number                                             | Step. | Freq.   | L2 Cache  | L3 Cache | нт          | Multi <sup>1</sup> | Voltage              | TDP  | Socket | Release<br>Date  |

|----------------------------------------------------------|-------|---------|-----------|----------|-------------|--------------------|----------------------|------|--------|------------------|

| Phenom II X3<br>700e                                     | C2    | 2.4 GHz | 3x 512 KB | 6 MB     | 2 GHz       | 12x                | 0.825 -<br>1.25      | 65 W | AM3    | June 2,<br>2009  |

| Phenom II X3<br>705e                                     | C2    | 2.5 GHz | 3x 512 KB | 6 MB     | 2 GHz       | 12.5x              | 0.800 -<br>1.25      | 65 W | AM3    | June 2,<br>2009  |

| Phenom II X3<br>710                                      | C2    | 2.6 GHz | 3x 512 KB | 6 MB     | 2 GHz       | 13x                | 0.875 -<br>1.42<br>5 | 95 W | AM3    | Febr. 9,<br>2009 |

| Phenom II X3<br>715<br><i>Black Edition<sup>2</sup></i>  | C2    | 2.8 GHz | 3x 512 KB | 6 MB     | 1.8 GH<br>z | 14x                | 0.875 -<br>1.42<br>5 | 95 W | AM2+   | ???              |

| Phenom II X3<br>720                                      | C2    | 2.8 GHz | 3x 512 KB | 6 MB     | 2 GHz       | 14x                | 0.875 -<br>1.42<br>5 | 95 W | AM3    | ???              |

| Phenom II X3<br>720<br><i>Black Edition<sup>2</sup></i>  | C2    | 2.8 GHz | 3x 512 KB | 6 MB     | 2 GHz       | 14x                | 0.850 -<br>1.42<br>5 | 95 W | AM3    | Febr. 9,<br>2009 |

| Phenom II X3<br>740<br><i>Black Edition</i> <sup>2</sup> | C2    | 3.0 GHz | 3x 512 KB | 6 MB     | 2 GHz       | 15x                | 0.850 -<br>1.42<br>5 | 95 W | AM3    | Sept.<br>2009    |

### Implementation of cores in a processor family

- Each processor family, like the K10.5 Shanghai family, etc. often is based on a number of processor lines with each line based on one or more different cores having different features, like the number of CPU cores or the size of the L2 cache.

- Obviously, different processor cores target different market segments (like servers, desktopsr or mobiles) and performance levels, like high-performance, mainstream or low cost processors.

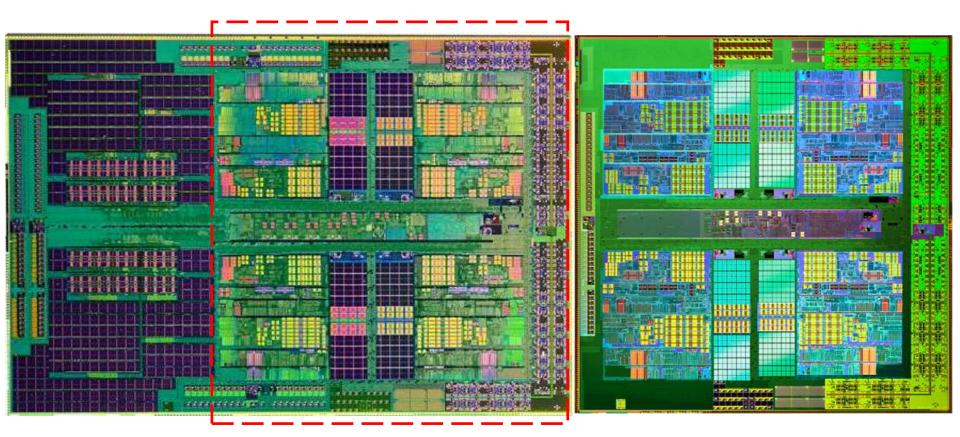

- As an example, the next slide depicts all the cores of the K10.5 (Shanghai) family.

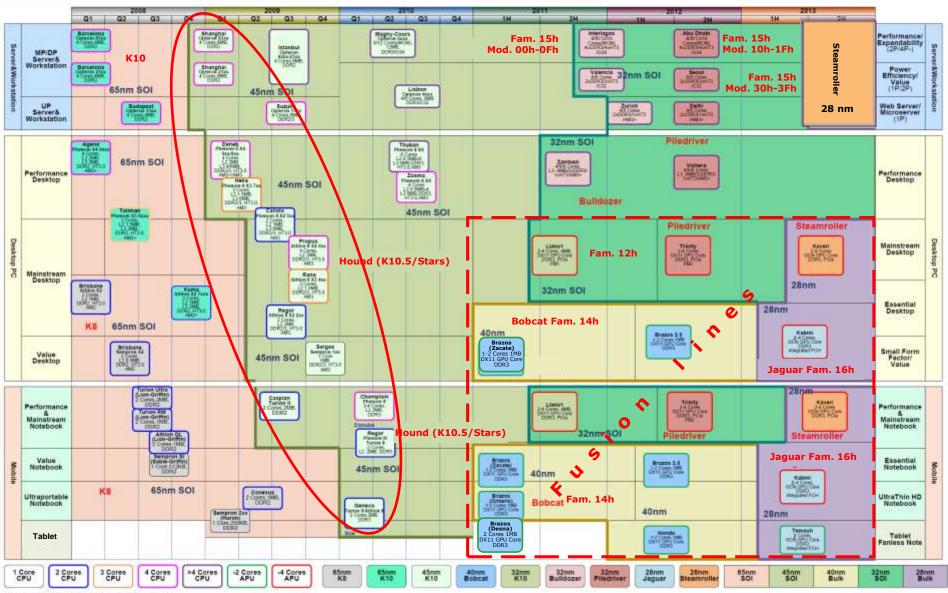

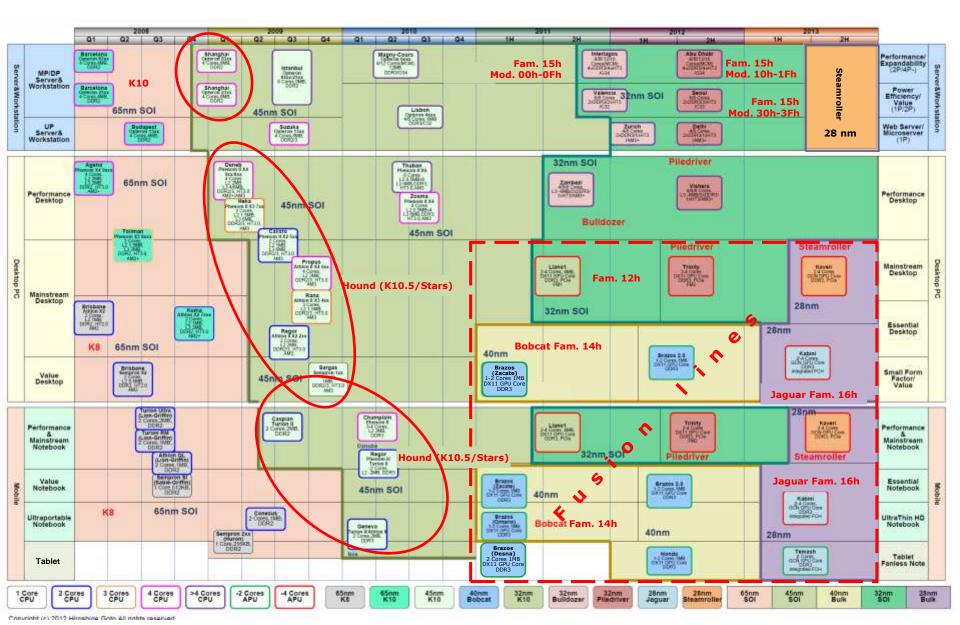

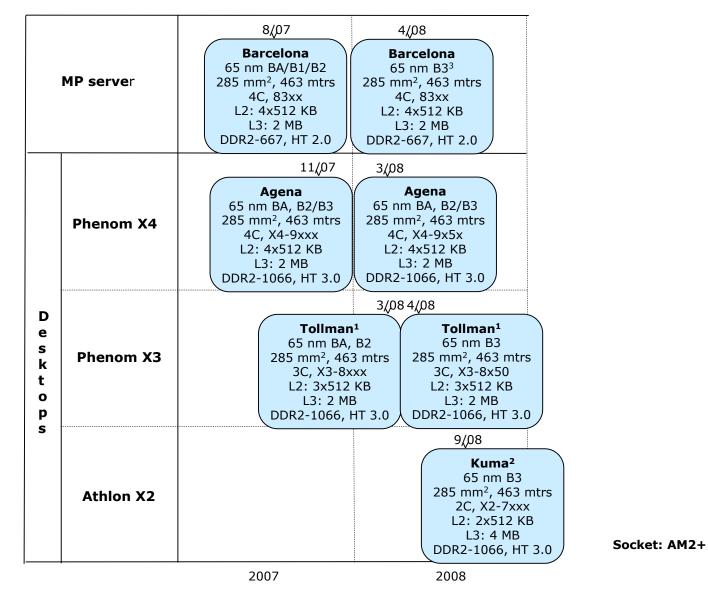

#### AMD's K10.5 Shanghai based processor lines [based on xx]

Convolability 2012 Hiroshine Goth All rights reserved

#### Set of processor cores targeting a particular market segment

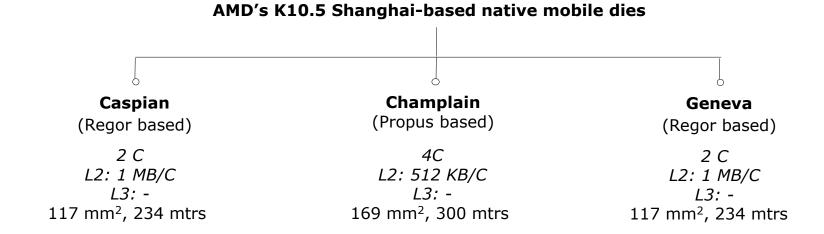

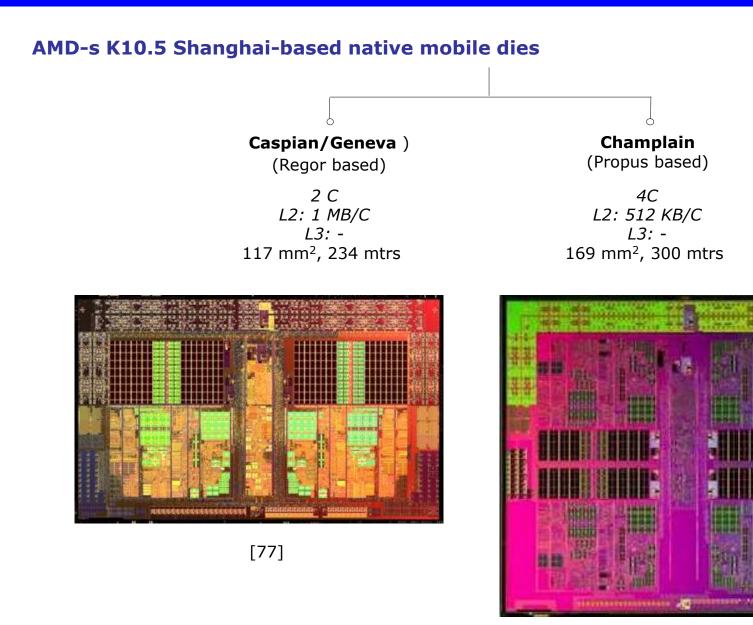

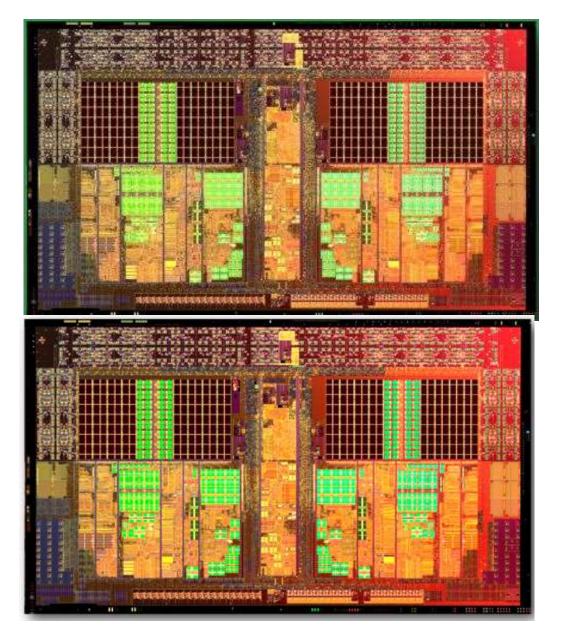

Typically, cores of a processor family, like the K10.5 Shanghai family, may be subdivided into a certain core sets, with each set aiming at different market segments, such as the server, desktop or mobile segment, as the next example for the K10.5 Shanghai family shows.

#### Sets of processor cores in the K10.5 Shanghai family [based on xx]

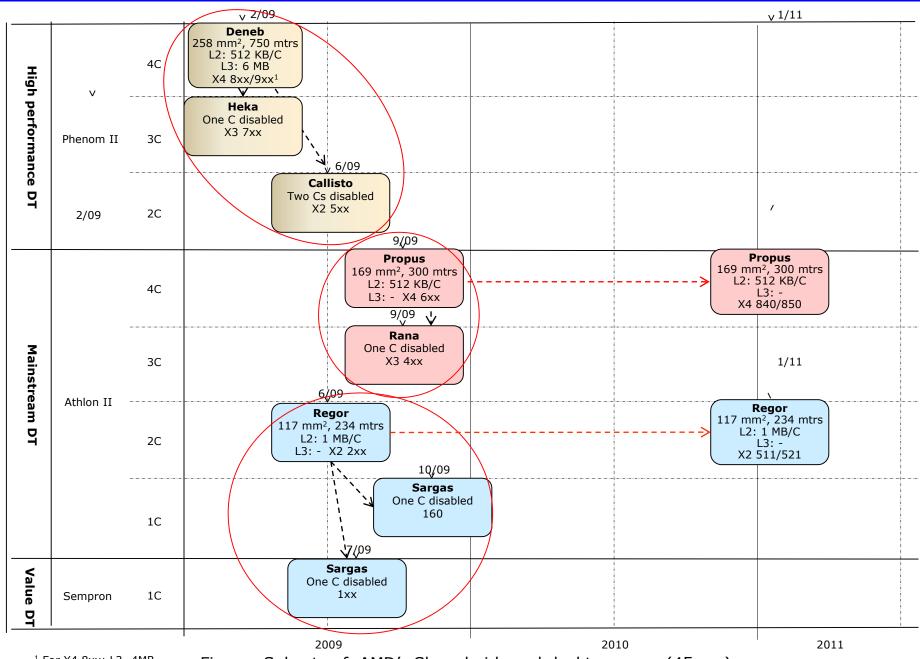

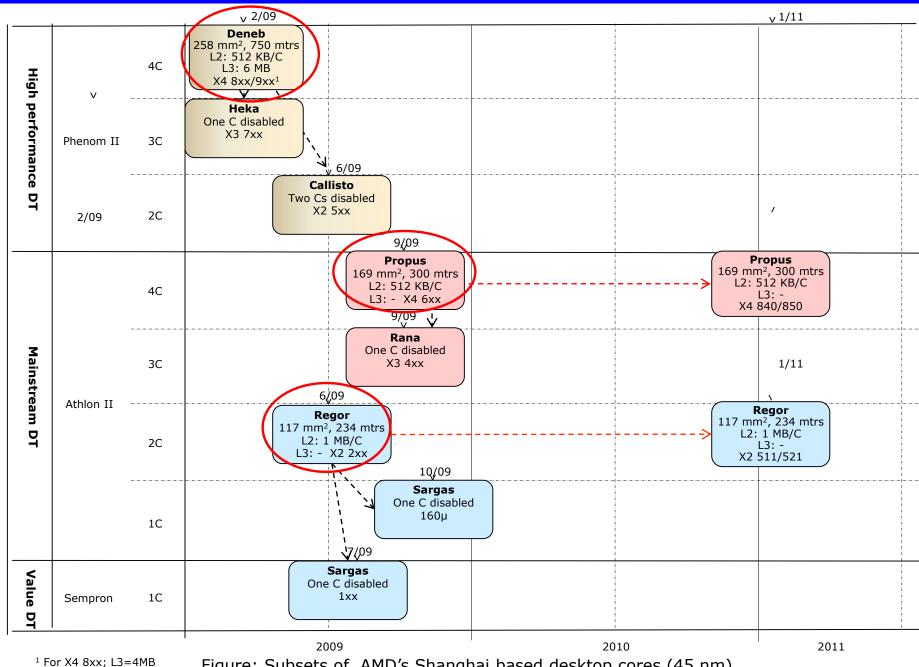

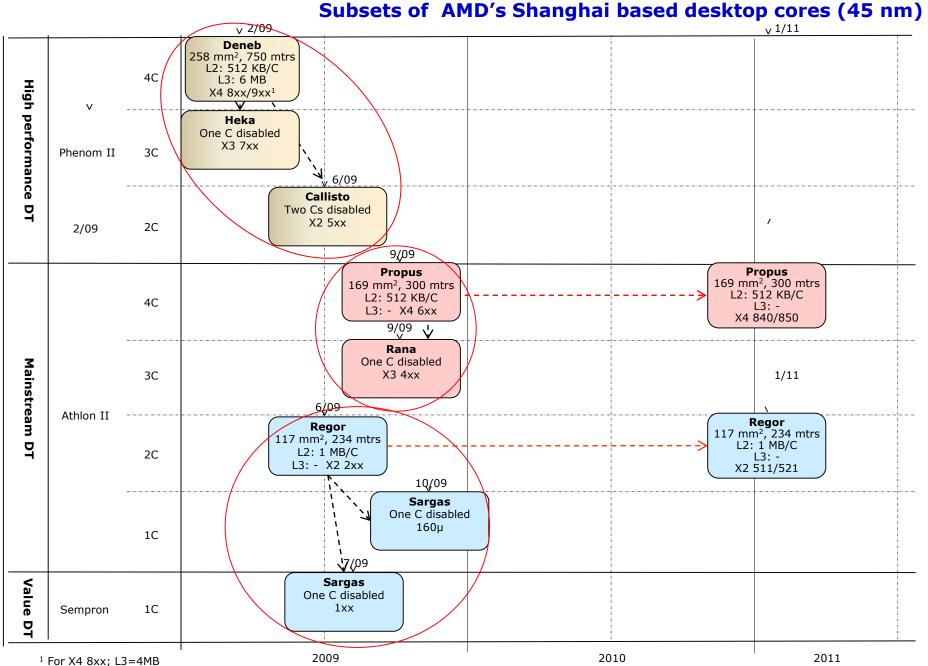

#### Subsets of processor cores within a set of cores

In some cases even a given set of processor cores that targets a particular market segment consists of a few subsets, each targeting different performance levels, such as high-performance, mainstream or low-cost processors, like the desktop cores of the K10.5 Shanghai family, as the next figure shows.

# 1. Introduction to AMD's processor families (20)

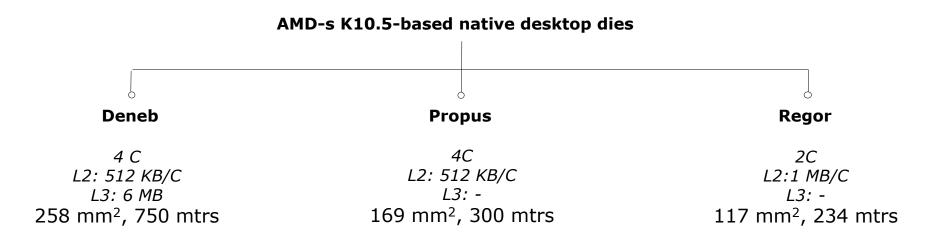

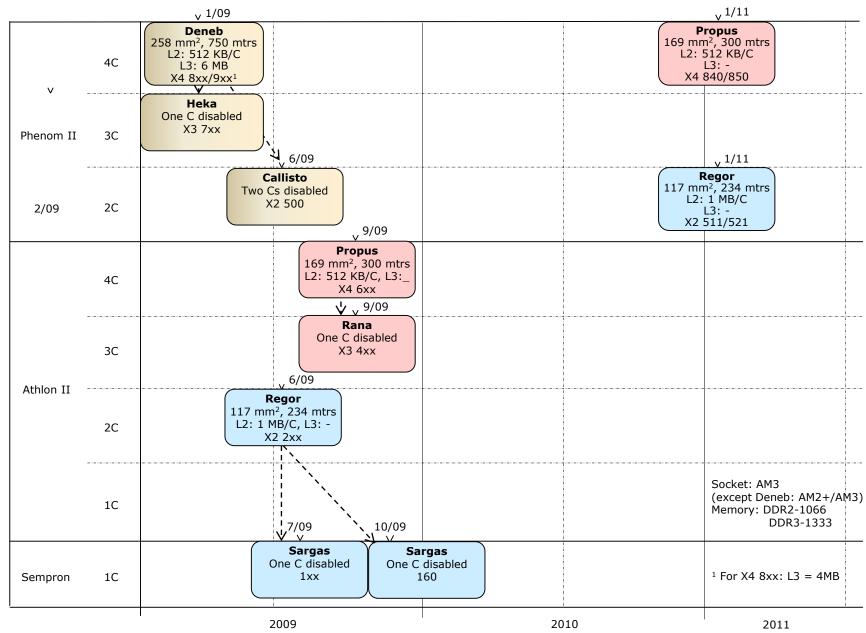

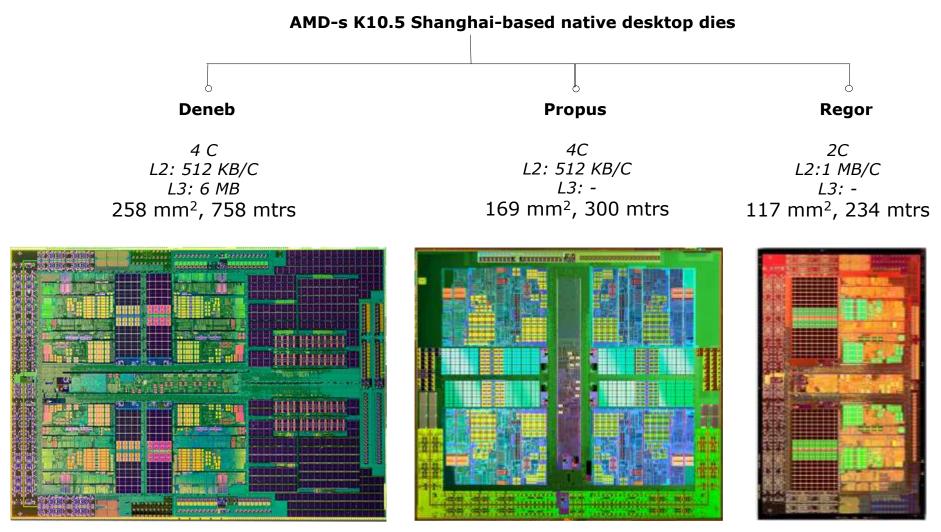

<sup>1</sup> For X4 8xx; L3=4MB Figure: Subsets

Figure: Subsets of AMD's Shanghai based desktop cores (45 nm)

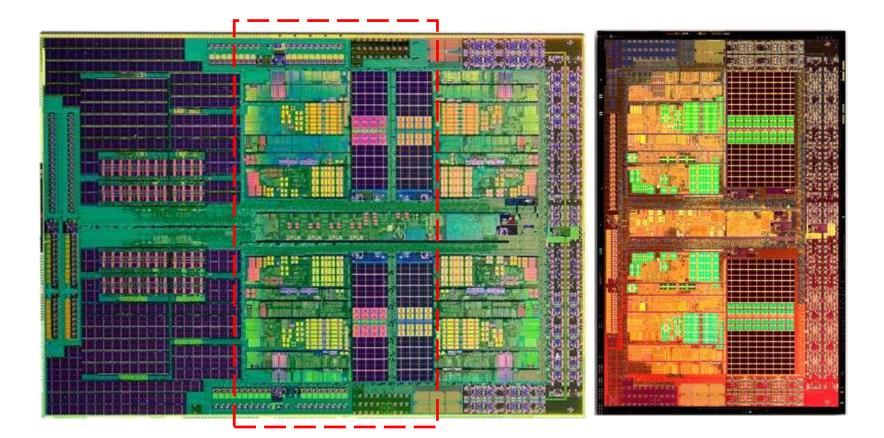

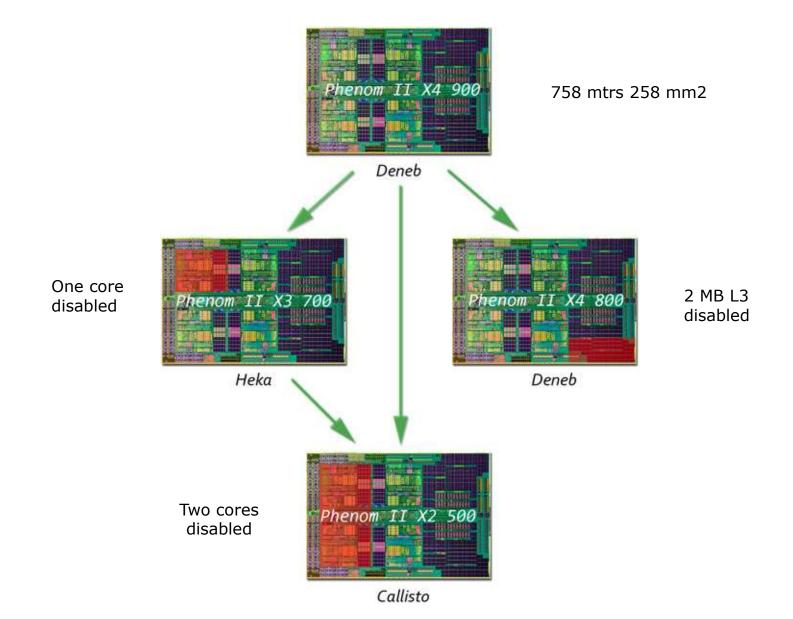

# Native designs and partly disabled cores

Sets of cores that can not be broken down into subsets or particular subsets typically include a native design and a few partly disabled cores.

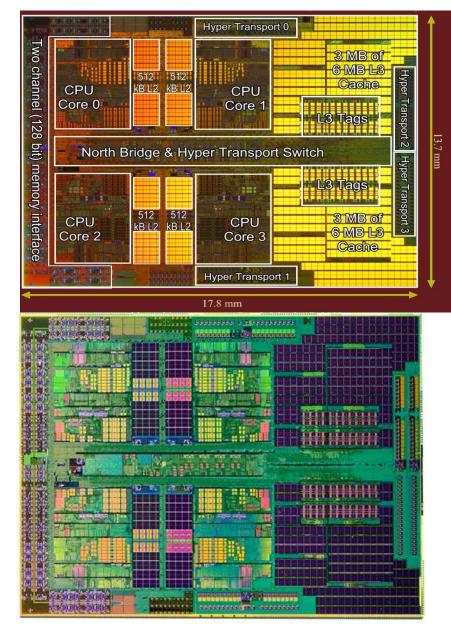

As an example, the desktop cores of the K10.5 Shanghai family are based on three native core designs, called the

- Deneb

- Propus and

- Regor,

cores, as indicated in the next figure.

# 1. Introduction to AMD's processor families (22)

Figure: Subsets of AMD's Shanghai based desktop cores (45 nm)

In the above Figure arrows indicate partly disabled cores that are derived from the native designs;

- E.g. In the Phenom II lines of the desktop cores of the K10.5 Shanghai family the 4-core Deneb core represents the native design whereas

- the Heka core is in fact a Deneb core with a single core disabled and

- the Callisto core is a Deneb core with two cores disabled,

as the next Figure shows.

# 1. Introduction to AMD's processor families (24)

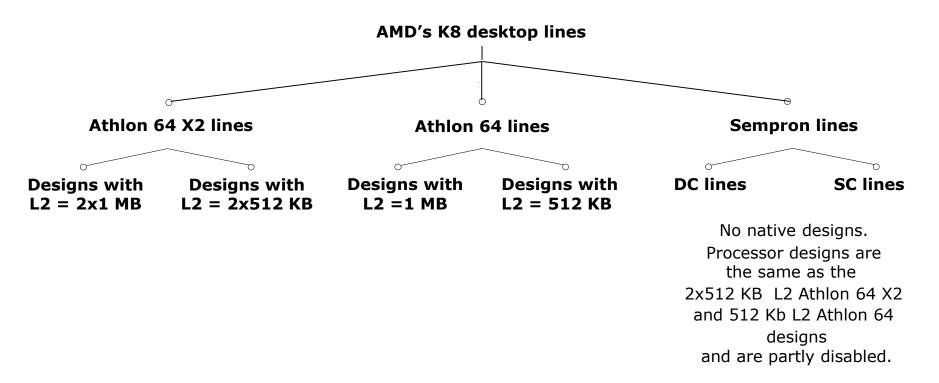

# Possible aims of disabling features of native designs

Disabling defective units Disabling available features to reduce functionality

Aim: To sell processors with defective features, such as less cores, smaller L2, no SSE3 or AMD-V at lower price

E.g. models of a particular line with smaller L2, e.g. 512 K L2 instead of 1 MB L2  $\,$

Aim: To avoid separate designs for lower priced lines but to maintain enough difference in functionality to higher priced lines

E.g. Sempron lines are typically native 512 KB L2 Athlon 64 designs with reduced functionality, such as 128/256 KB L2 and disabled SSE3 or AMD-V

#### Remark

In this chapter we focus on AMD's processor designs rather than marketing issues, so typically we disregard partly disabled native designs.

#### Remark

Core designations are often irritating and serve marketing purposes as for example the previous figure demonstrates.

## **Overview of AMD's processor lines**

#### Remark

Before the K5 AMD manufactured (licensed) Intel designed processors rather than own designs

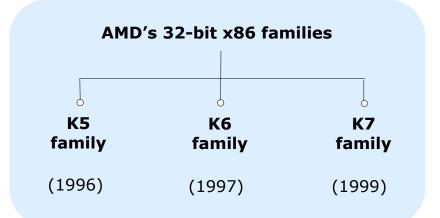

# AMD's 32-bit x86 families

## **Overview and major innovations of AMD's K5/K6 families**

| CPU Family               | Intro.               | CPU core                 | Brand name | Techn.<br>(µm)       | New key feature                                               | Typ.<br>Application |

|--------------------------|----------------------|--------------------------|------------|----------------------|---------------------------------------------------------------|---------------------|

| К5                       | 1996                 |                          | К5         | 0.5/0.35             | 2. gen. superscalar (32-bit),<br>Pentium competitor           | DT                  |

| К6                       | 1997                 |                          | К6         | 0.35/0.25            | 2.5 gen. superscalar, MMX<br>(NexGen design)                  | DT/M                |

| K6-2                     | 1998                 | Chomper                  | К6         | 0.25                 | 3. gen. superscalar, 3DNow!                                   | DT/M                |

| K6III<br>K6-2+<br>K6III+ | 1999<br>2000<br>2000 | Sharptooth<br>na.<br>na. | K6         | 0.25<br>0.18<br>0.18 | On-die L2<br>PowerNow! <sup>1</sup><br>PowerNow! <sup>1</sup> | DT/M                |

<sup>1</sup> PowerNow! was introduced in the Mobile K6-2+ and Mobile K-III+ processors in 2000

<sup>2</sup> Athlon: Attained performance lead over Intel's Pentium III

# **Overview and major innovations in AMD's K7 (Athlon) families**

|    | e arch./<br>epping | Intro.  | Core           | Brand<br>name         | Techn.<br>(µm) | L2                    | cache                 | FSB        | ISA                 | PowerNow! | Typ.<br>Appl |

|----|--------------------|---------|----------------|-----------------------|----------------|-----------------------|-----------------------|------------|---------------------|-----------|--------------|

|    | Mod.1              | 6/1999  | Argon          | Athlon                | 0.25           | In-package integrated |                       |            |                     |           |              |

|    | Mod.2              | 11/2000 | Pluto/Orion    | Atmon                 |                | 5                     | 12 KB                 |            |                     |           | DT           |

|    |                    | 6/2000  |                | Duron                 |                |                       |                       |            | Enh.<br>3DNow!      |           |              |

|    | Mod.3              | 1/2001  | Spitfire       | Mobile<br>Duron       |                | 64 KB                 | 64 KB                 |            |                     |           | М            |

|    | Mod.4              | 6/2000  | Thunderbird    | Athlon                |                |                       |                       |            |                     |           | DT           |

|    |                    | 7/2001  |                | Mobile<br>Athlon4     | 0.18           | 256 KB                |                       |            | 3DNow!<br>Prof./SSE | PowerNow! | М            |

|    | Mod.6              | 10/2001 | Palomino       | Athlon XP             | -              |                       |                       |            |                     | -         | DT           |

|    |                    | 4/2001  |                | Athlon MP             |                |                       |                       |            |                     |           | S            |

|    |                    | 8/2001  | Morgan         | Duron                 |                | 64 KB                 | On-die<br>(exclusive) | DDR<br>FSB |                     |           | DT           |

| K7 | Mod.7              | 1/2001  | Camaro         | Mobile<br>Duron       |                |                       |                       |            |                     | PowerNow! | М            |

|    |                    | 11/2002 | Thoroughbred   | Duron                 |                |                       |                       |            |                     | -         | DT           |

|    |                    | 3/2003  | ritorougribreu | Athlon XP             |                | 256 КВ                |                       |            |                     |           | S            |

|    | Mod.8              | 8/2003  | Applebread     | Athlon MP             |                |                       |                       |            |                     |           |              |

|    |                    | 4/2002  | Thoroughbred   | Mobile<br>Athlon XP-M |                |                       |                       |            |                     |           | М            |

|    |                    | 9/2003  | Thorton        | Athlon XP             | 0.13           |                       |                       |            |                     |           | DT           |

|    |                    | 9/2003  |                |                       | -              |                       |                       |            |                     |           | וס           |

|    | Mod.10             | 5/2003  | Barton         | Athlon MP             |                | 512 KB                |                       |            |                     |           | S            |

|    |                    | 3/2003  |                | Mobile<br>Athlon XP-M |                |                       |                       |            |                     | PowerNow! | М            |

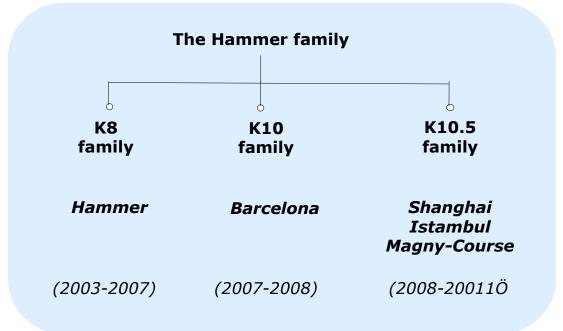

#### **The Hammer family**

# Brand names of AMD's 64-bit K8 – Family 10.5h processor lines

|                       |                                | 2003-2007                                                  | 2007-2008                 | 2008-2011                                                                     | 2009                    | 2009                     |

|-----------------------|--------------------------------|------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------|-------------------------|--------------------------|

|                       |                                | K8<br>(Hammer)                                             | K10<br>(Barcelona)        | K10.5<br>(Shanghai)                                                           | K10.5<br>(Istanbul)     | K10.5<br>(Magny- Course) |

| r s                   | 4P servers                     |                                                            | Barcelona<br>(834x-836x)) | Shanghai<br>(837x-839x)                                                       | lstambul<br>(8410-8430) | Magny-Course<br>(6100)   |

| r v e                 | 2P servers                     | See Section 4                                              | Barcelona<br>(234x-236x)  | Shanghai<br>(237x-239x)                                                       | lstambul<br>(241x-243x) | Lisbon<br>(4100)         |

| Se                    | 1P servers                     |                                                            | Budapest<br>(135x-136x)   | Suzuka<br>(138x-139x)                                                         |                         |                          |

| o p s                 | High perf.<br>(~80-120W)       |                                                            | Phenom<br>X4-X2           | Phenom II<br>X4-X2                                                            | Phenom II<br>X6-X4      |                          |

| skto                  | Mainstream<br>(~60-90W)        | Athlon 64<br>Athlon 64 X2                                  | Athlon X2                 | Athlon II X4-X2                                                               |                         |                          |

| De                    | <b>Value</b><br>(~40-60W)      | Sempron                                                    |                           | Sempron                                                                       |                         |                          |

| e s                   | <b>High perf.</b><br>(~30-40W) | Turion 64 X2<br>(TL 6/5)<br>Turion 64 (ML/MT)              |                           | Phenom II<br>(N/P 9xx-6xx)<br>Turion II Ultra (M6xx)<br>Turion II (M/N/P 5xx) |                         |                          |

| Mobil                 | Mainstream<br>(~20-30W)        | Athlon 64 X2<br>(TK-5x/4x)<br>Athlon 64<br>(2xxx+-4xxx+)   |                           | Athlon II (M/N/P 3xx)<br>Sempron (M1xx)                                       |                         |                          |

|                       | Ultraportable<br>(~10-20W)     | Mobile Sempron<br>(2xxx+-4xxx+)<br>Sempron 2100<br>fanless |                           | Turion II Neo (K6xx)<br>Athlon II Neo (K1xx)<br>V-series (V1xx)               |                         |                          |

| Embedded<br>(~10-20W) |                                |                                                            |                           | Turion II Neo X2<br>Athlon II Neo X2<br>Athlon II Neo                         |                         |                          |

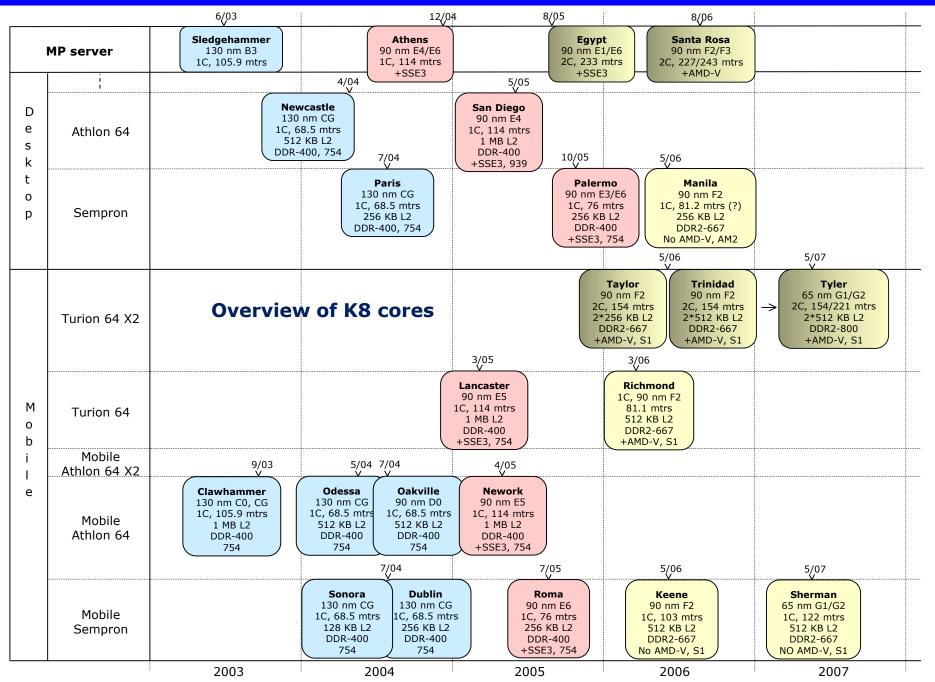

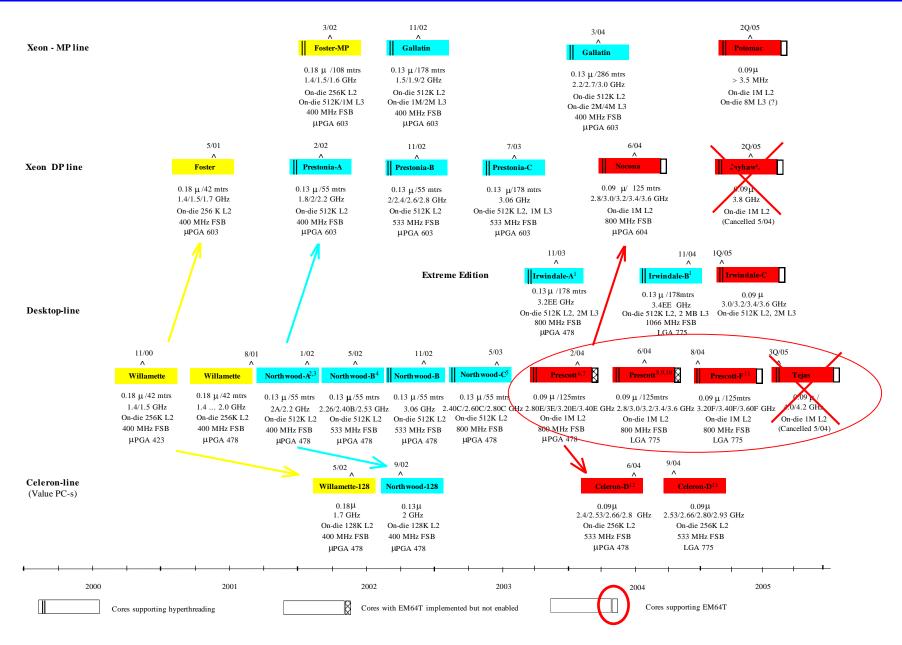

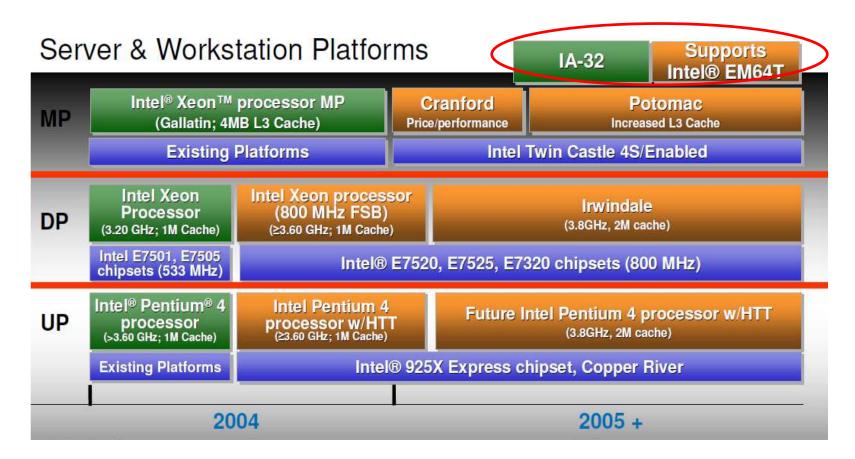

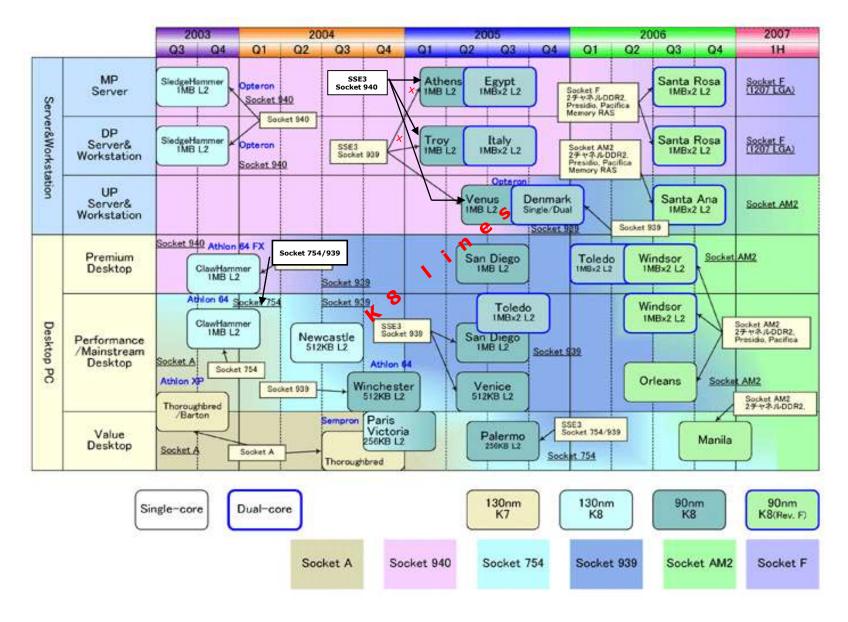

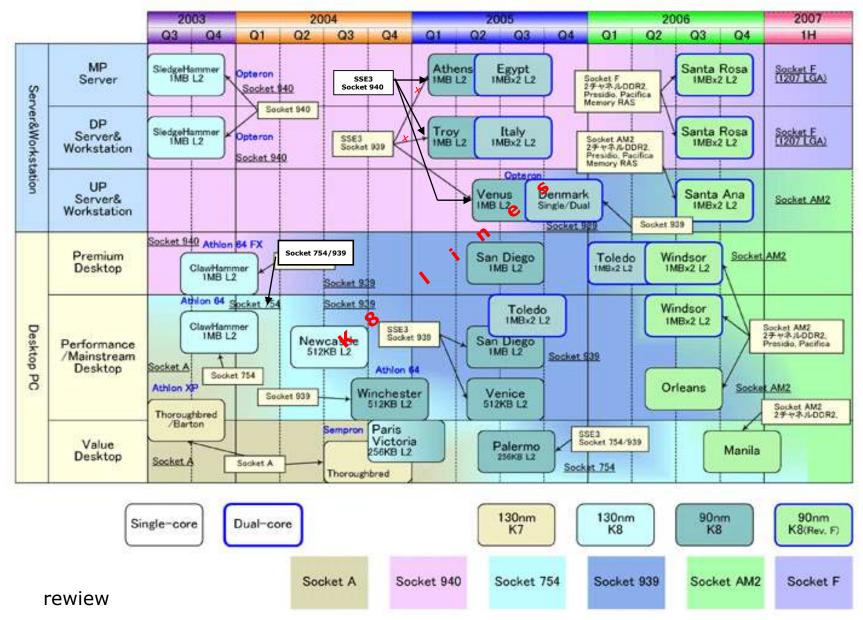

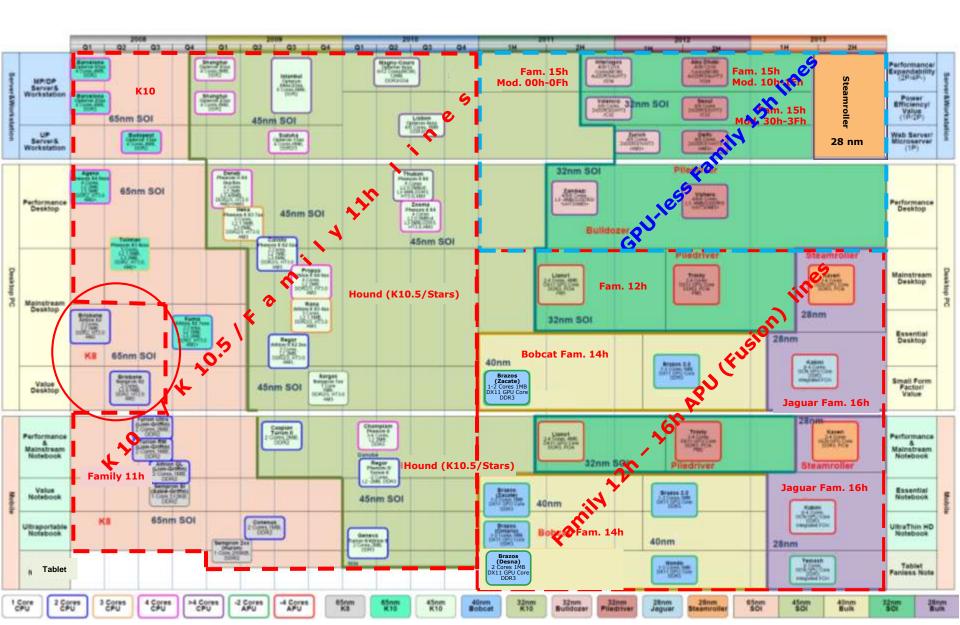

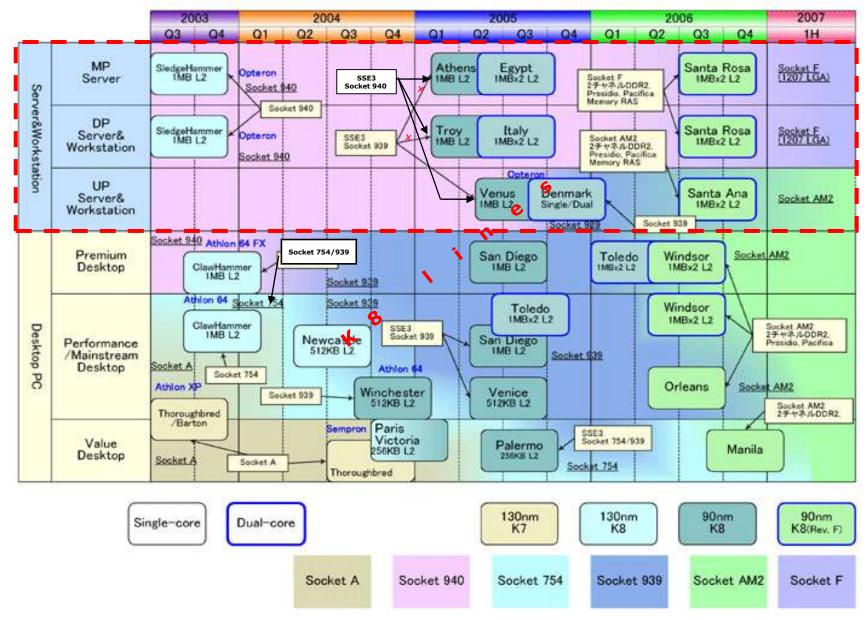

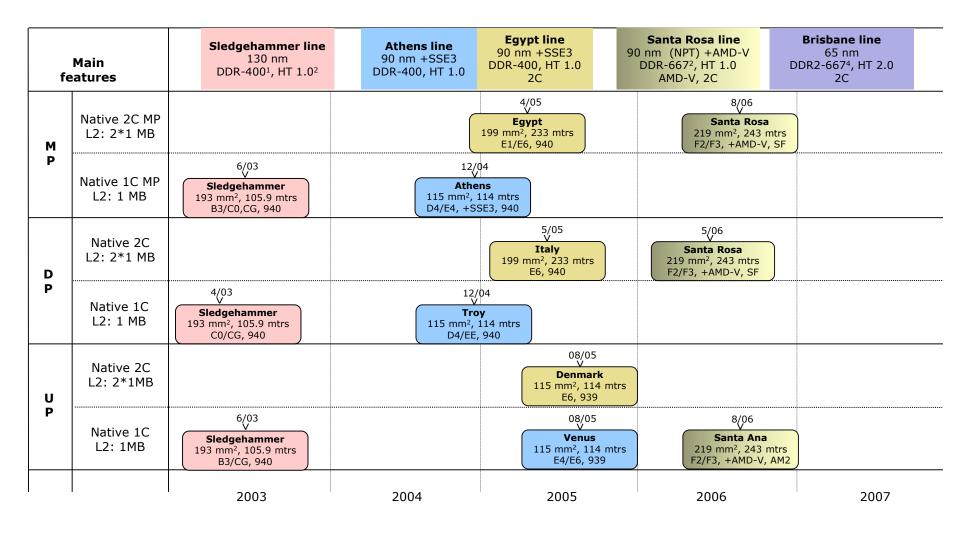

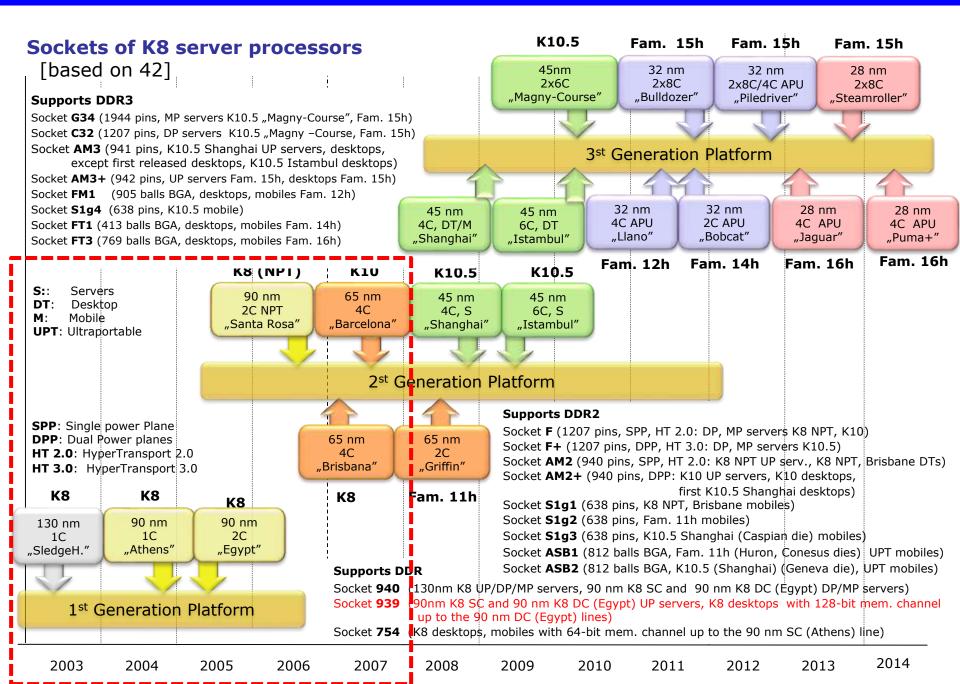

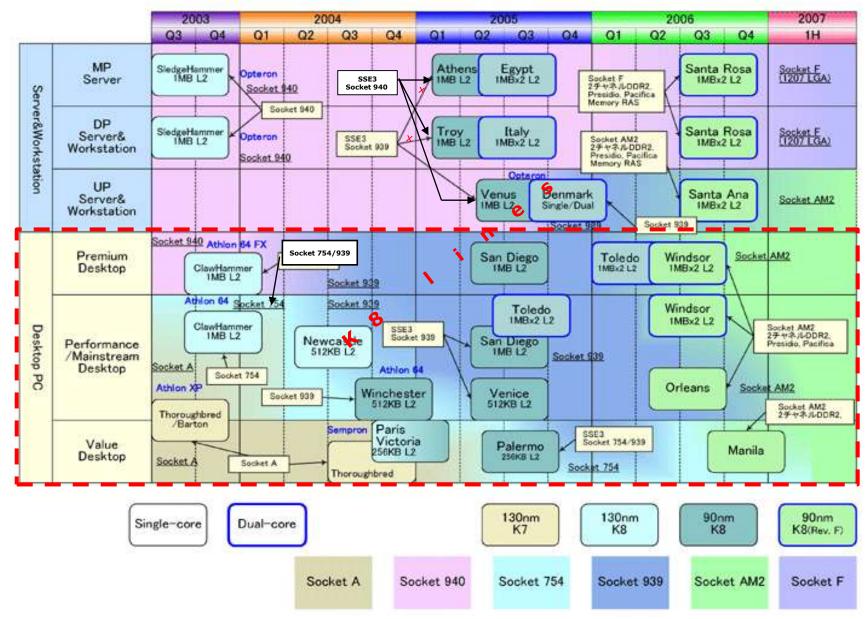

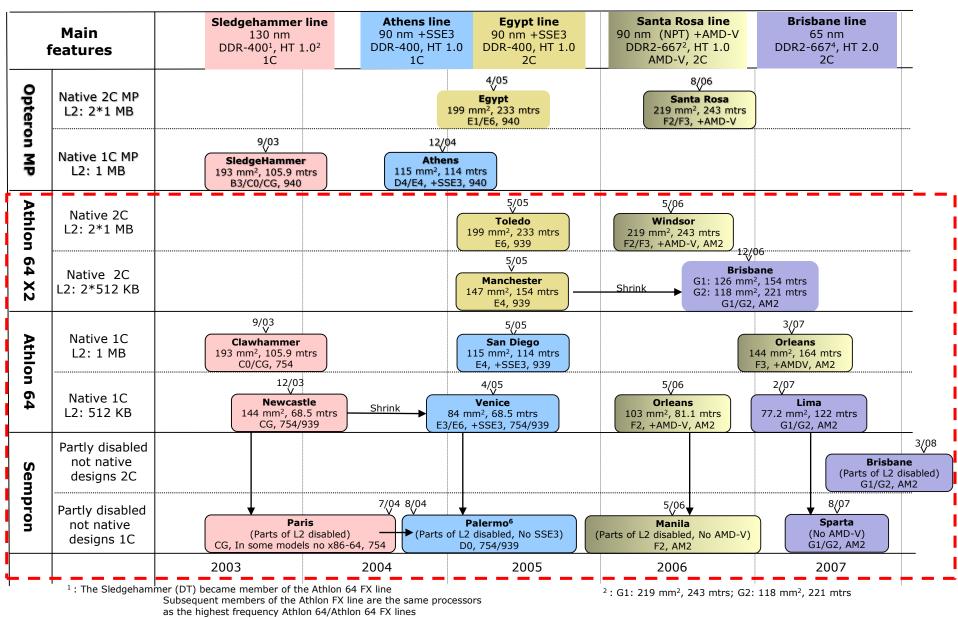

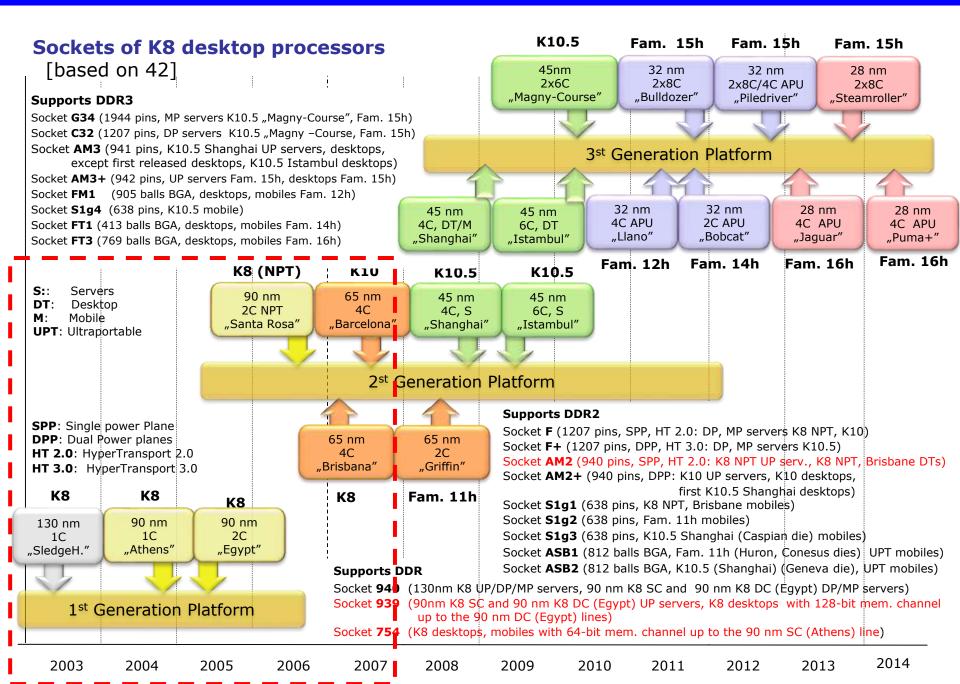

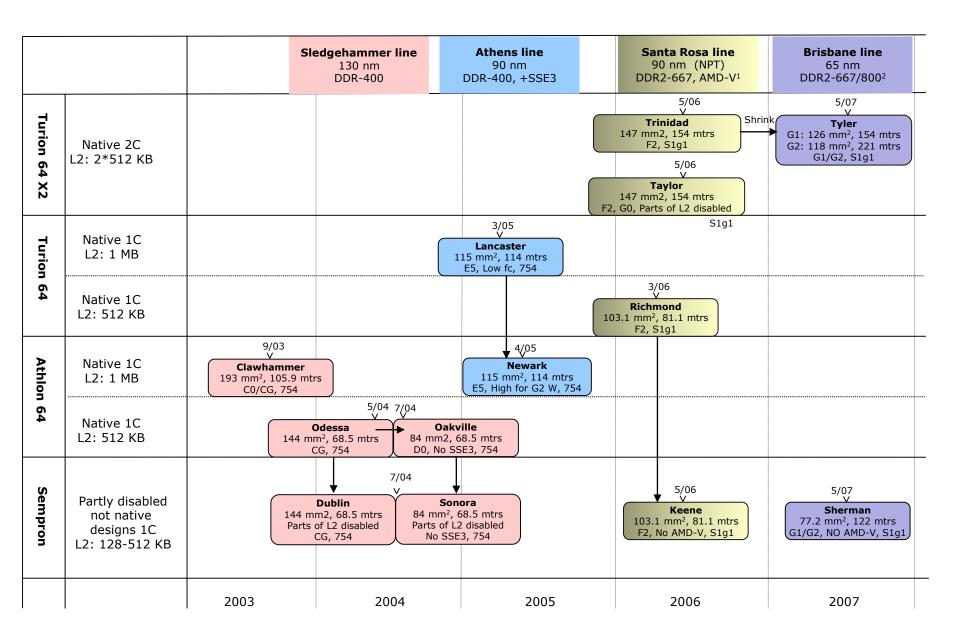

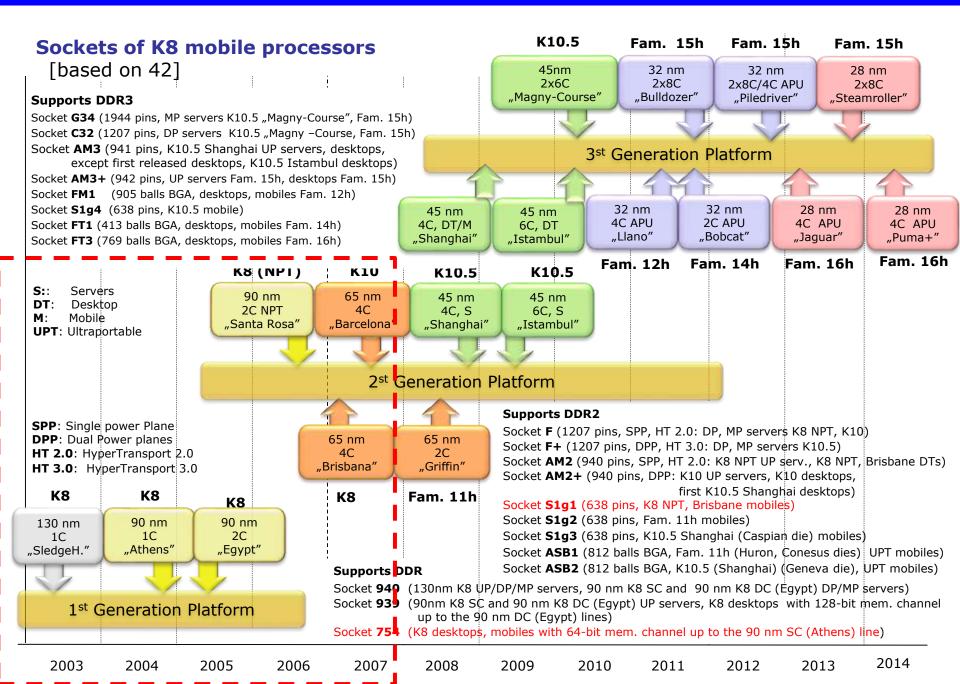

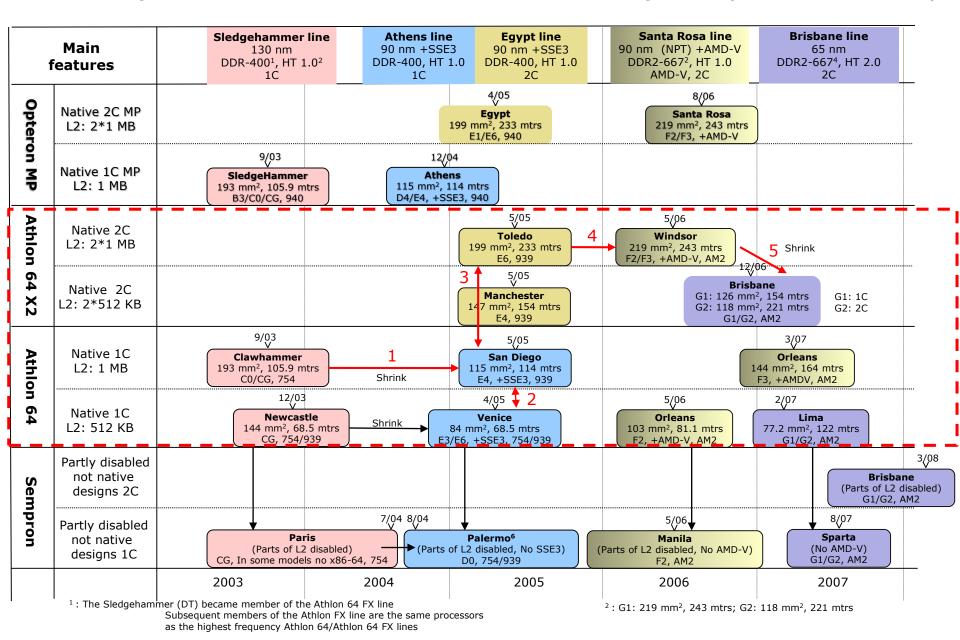

# Overview of AMD's K8-based processor lines The 130 nm – 90 nm K8-based lines [13]

# 1. Introduction to AMD's processor families (34)

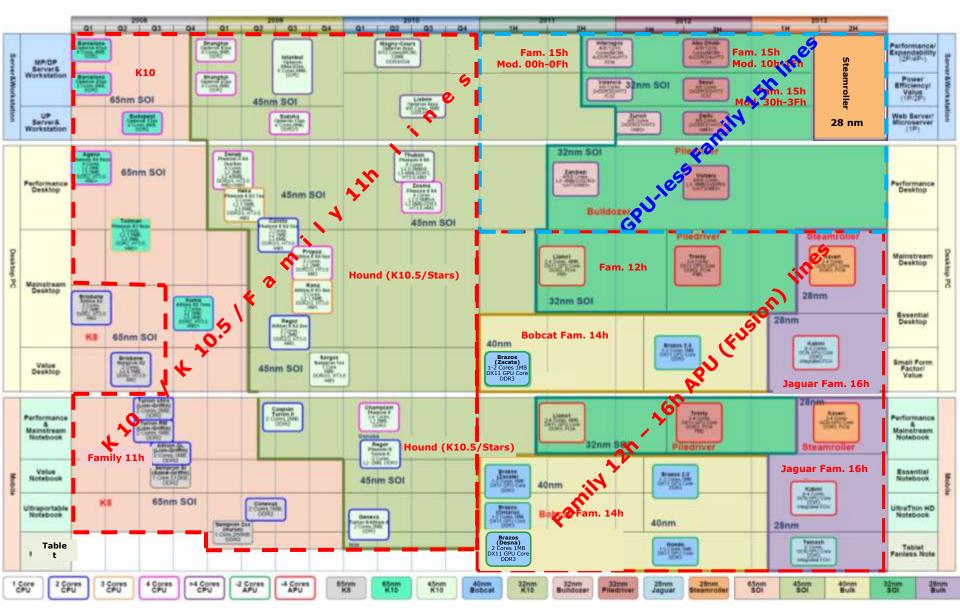

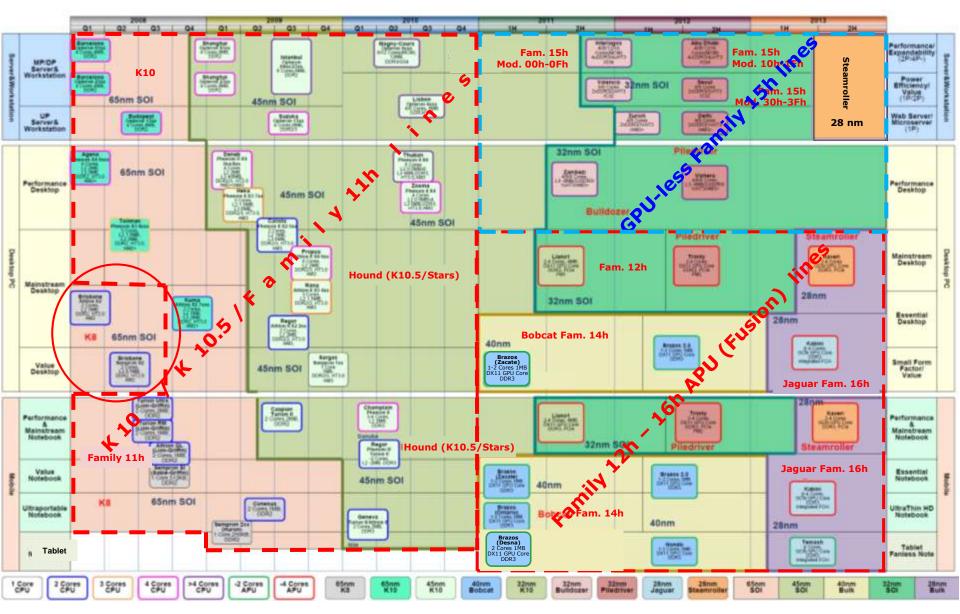

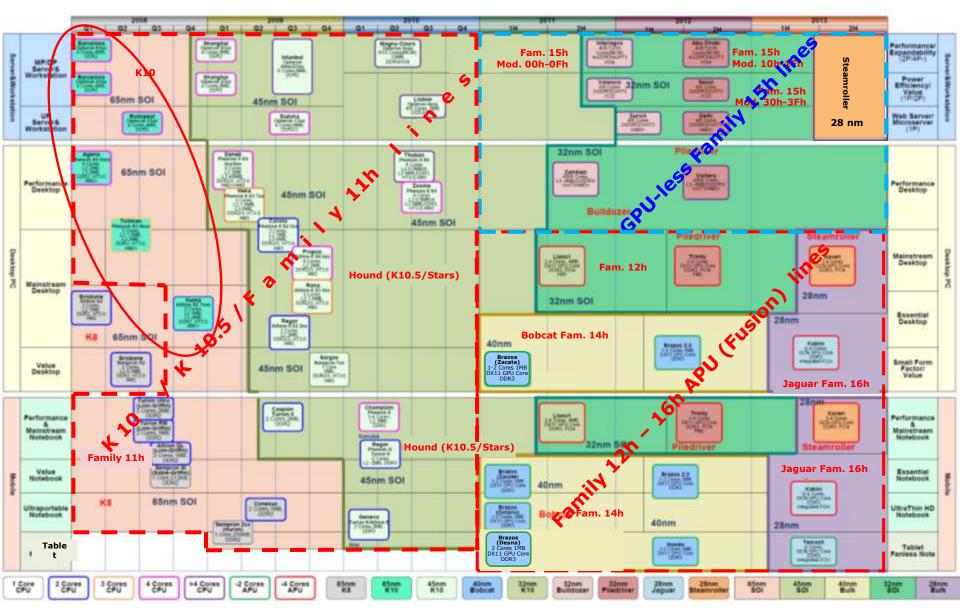

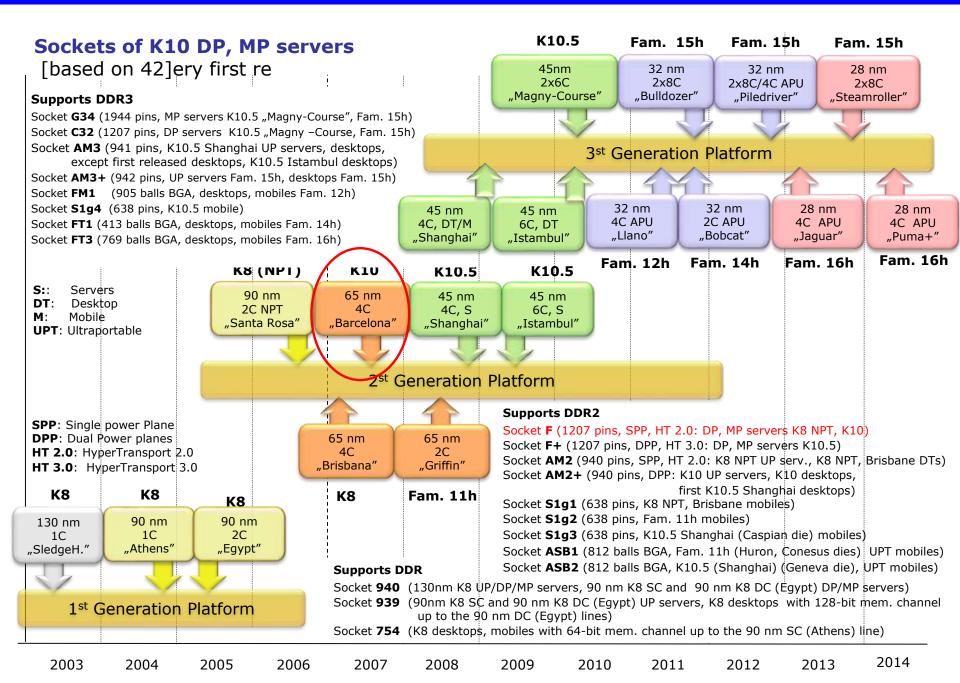

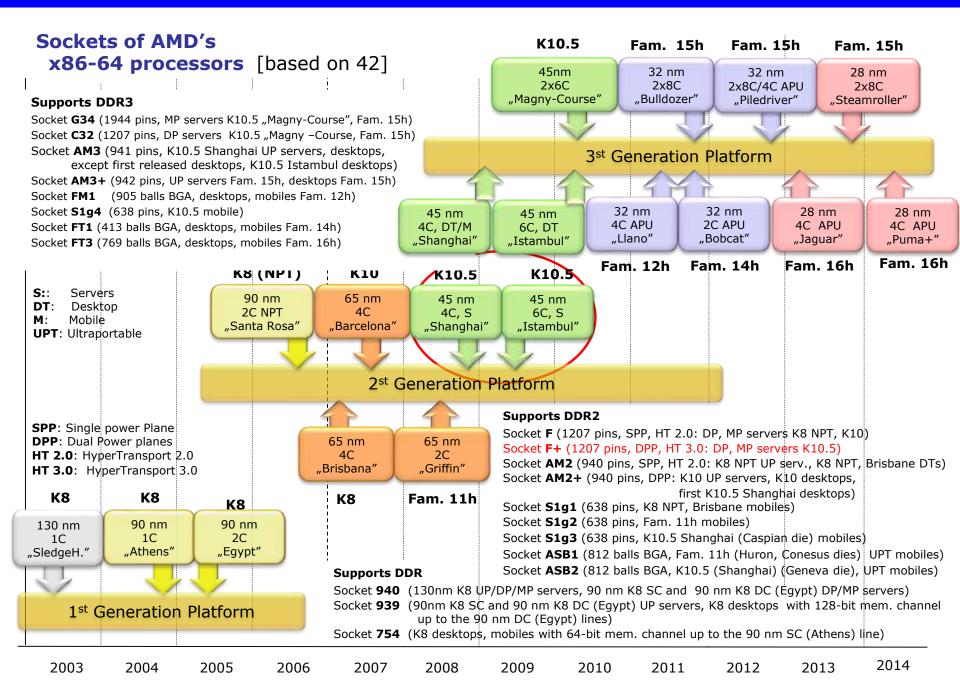

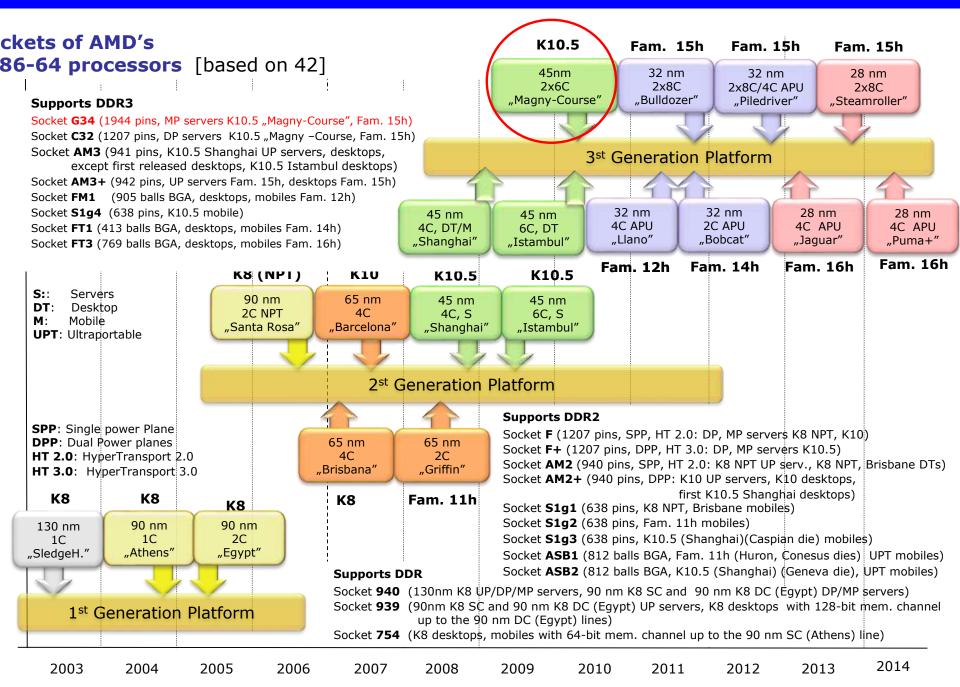

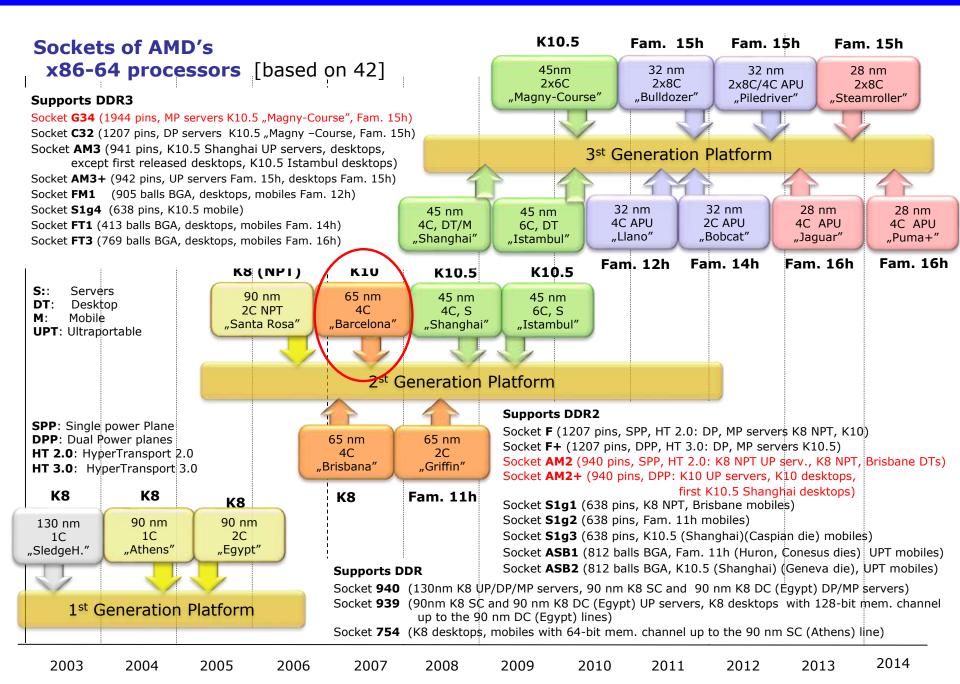

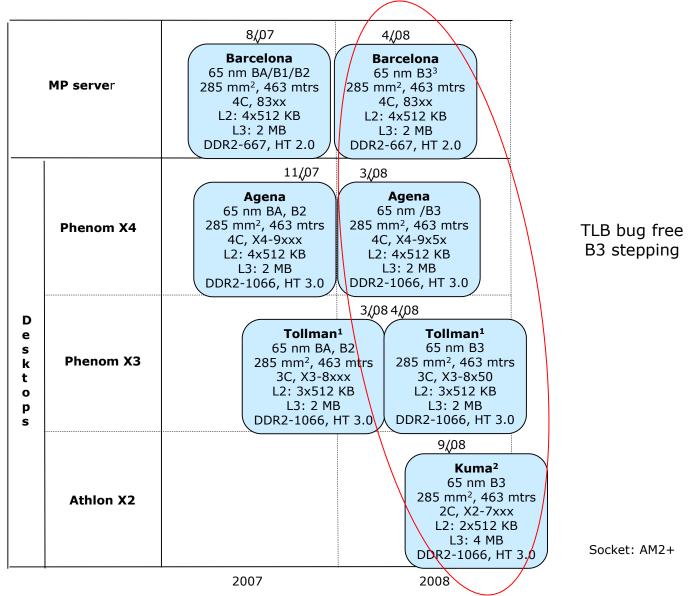

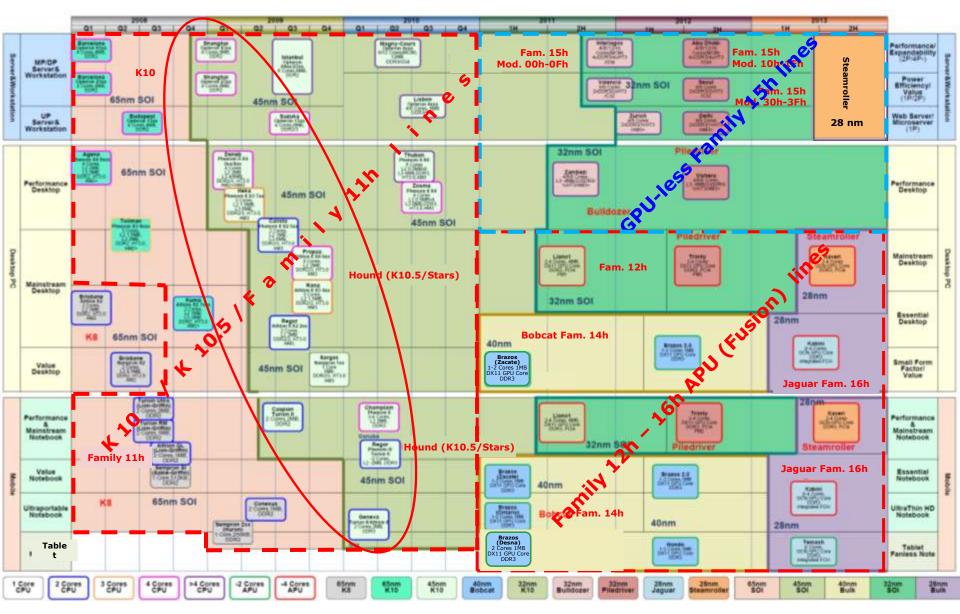

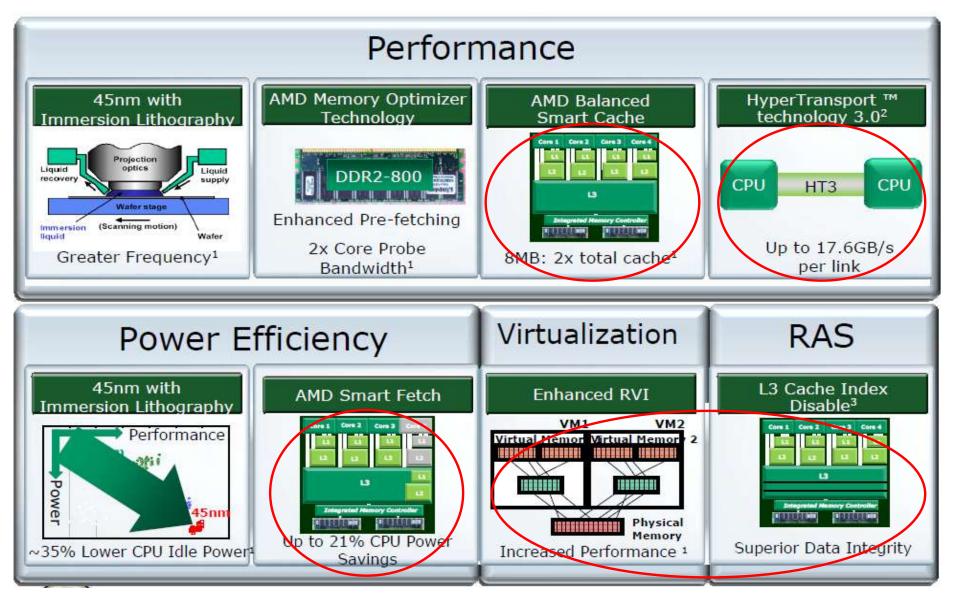

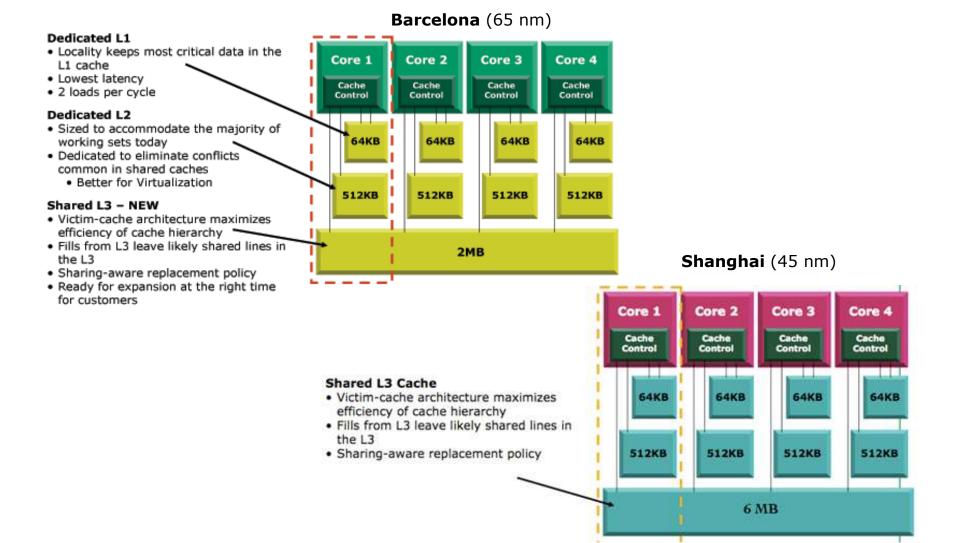

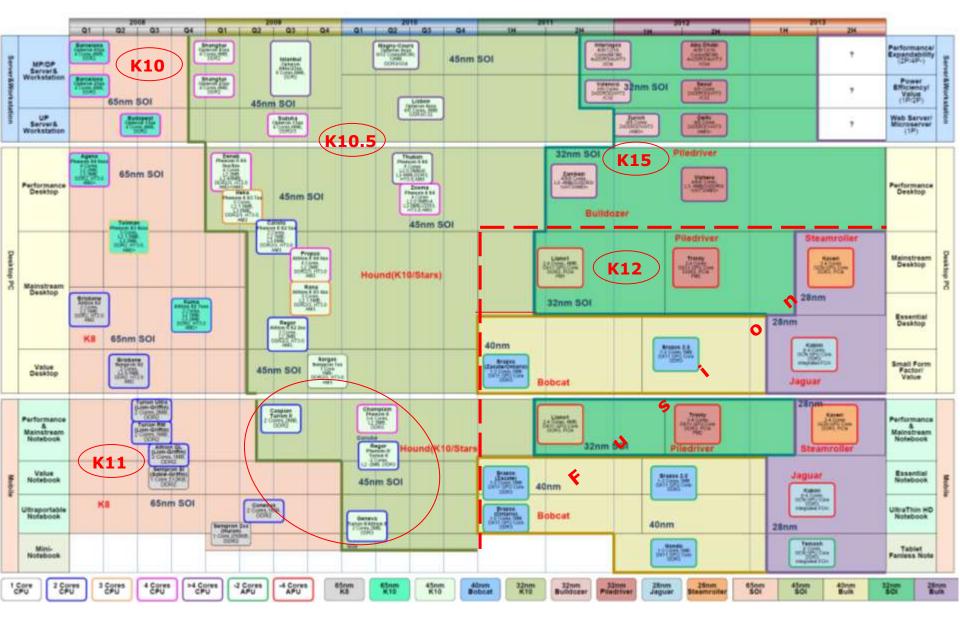

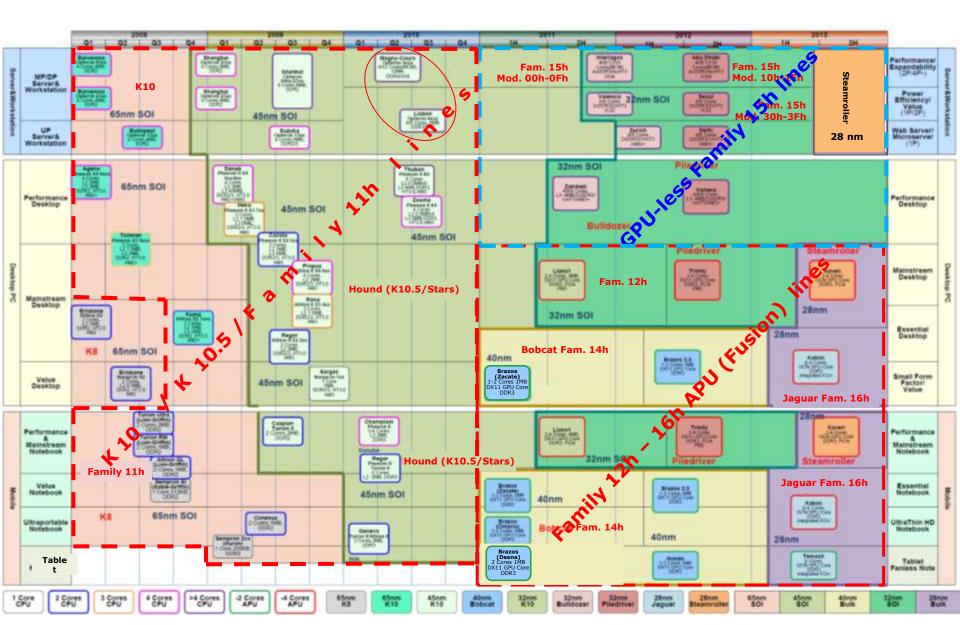

**Overview of AMD's K10/K10.5-based processor lines** [14]

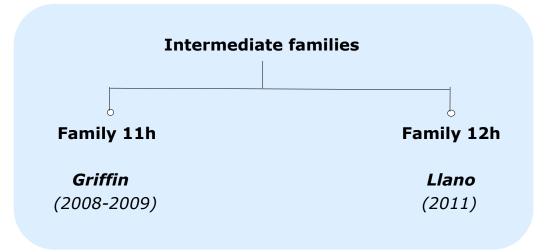

#### **AMD's intermediate families**

# Brand names of AMD's Intermediate (Family 11h – Family 12h) processor lines

|           | Launched in                         | 2008-2009                                                                                | 2011                            |

|-----------|-------------------------------------|------------------------------------------------------------------------------------------|---------------------------------|

|           |                                     | Family 11h<br>(Griffin)                                                                  | Family 12h<br>(Llano)           |

|           | 4P servers                          |                                                                                          |                                 |

| ers       | 2P servers                          |                                                                                          |                                 |

| Servers   | 1P servers                          |                                                                                          |                                 |

| S         | (85-140 W)                          |                                                                                          |                                 |

| SC        | <b>High perf.</b><br>(~95-125 W)    |                                                                                          |                                 |

| Desktops  | Mainstream<br>(~65-100 W)           |                                                                                          | Llano A8/A6/A4/E2<br>Sempron X2 |

| De        | Entry level<br>(40-60 W)            |                                                                                          |                                 |

|           | <b>High perf.</b><br>(~30-60 W)     | Turion X2 Ultra (ZM-xx)<br>Turion X2 (RM-xx)                                             | Llano A8 M                      |

| Notebooks | Mainstream/Entry<br>(~20-30 W)      | Athlon X2 (QL-xx)<br>Sempron (SI-xx)                                                     | Llano A6/A4/E2 M                |

| Note      | <b>Ultra portable</b><br>(~10-15 W) | Turion Neo X2 (L6xx)<br>Turion X2 (RM-xx)<br>Athlon Neo X2 (L3xx)<br>Sempron (200U/210U) |                                 |

|           | Tablet (~5 W)                       |                                                                                          |                                 |

|           | <b>Embedded</b><br>(~10 – 20 W)     | Turion Neo X2 (L6xx)<br>Athlon Neo X2 (L3xx)<br>Sempron (200U/210U)                      |                                 |

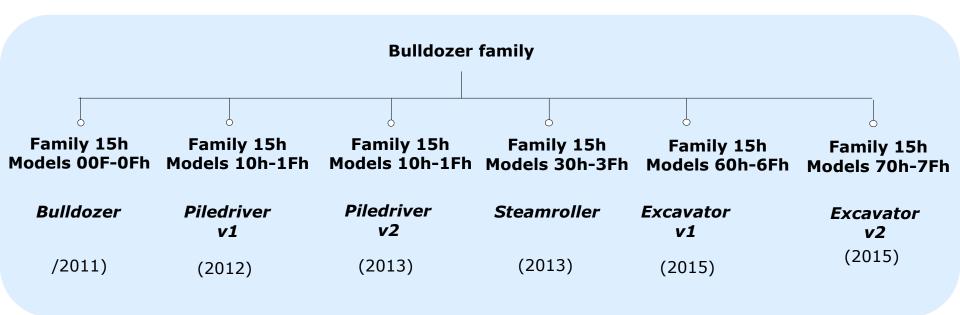

#### The Bulldozer family

# Brand names of AMD's Bulldozer-based processor lines

|                   | Launched in                              | 2011                                   | 2012                                    | 2013                                           | 2013                                     | 2015                                          | 2016                                          |

|-------------------|------------------------------------------|----------------------------------------|-----------------------------------------|------------------------------------------------|------------------------------------------|-----------------------------------------------|-----------------------------------------------|

|                   |                                          | Family 15h<br>(00h-0Fh)<br>(Bulldozer) | Family 15h<br>(10h-1Fh)<br>(Piledriver) | Family 15h<br>(10h-1Fh)<br>(Piledriver<br>v.2) | Family 15h<br>(30h-3Fh)<br>(Steamroller) | Family 15h<br>(60h-6Fh)<br>(Excavator<br>v.1) | Family 15h<br>(77h-3Fh)<br>(Excavator<br>v.2) |

|                   | <b>4P servers</b><br>(85-140 W)          | Interlagos                             | Abu Dhabi                               |                                                |                                          |                                               |                                               |

| Servers           | <b>2P servers</b><br>(85-140 W)          | Valencia                               | Seoul                                   |                                                |                                          |                                               |                                               |

| Š                 | <b>1P servers</b><br>(85-140 W)          | Zurich                                 | Delhi                                   |                                                |                                          |                                               |                                               |

| sd                | High perf.<br>(~95-125 W)                | Zambezi<br>FX-Series                   | Vishera<br>FX-Series                    |                                                |                                          |                                               |                                               |

| Desktops          | <b>Mainstream</b><br>(~65-100 W)         |                                        | Trinity<br>A10-A4 Series                | Richland<br>A10-A4 Series                      | Kaveri<br>A10-A8                         |                                               |                                               |

|                   | Entry level<br>(~40-60W)                 |                                        |                                         |                                                |                                          |                                               |                                               |

| oks               | High perf.<br>(~30-40 W)                 |                                        | Trinity<br>A10 M-A6 M                   | Richland<br>A10 M-A4 M                         | Kaveri<br>FX/A10/A8                      |                                               |                                               |

| Tablets/Notebooks | Mainstream/<br>Entry level<br>(~20-30 W) |                                        | Trinity<br>A10 M-A6 M                   | Richland<br>A10 M-A4 M                         | Kaveri<br>FX/A10/A8/A6                   | Carrizo<br>FX/A12-A6                          | Bristol Ridge<br>FX/A12/A10                   |

| blets/            | Ultra portable<br>(~10 - 15 W)           |                                        |                                         |                                                |                                          |                                               | Stoney Ridge<br>A9/A6/A4/E2                   |

| Tal               | Tablet<br>(~5 W)                         |                                        |                                         |                                                |                                          |                                               |                                               |

#### The Cat family

# Brand names of AMD's Family 12h, 14h and 16h-based processor lines

|           | Launched in                                         | 2011                                      | 2012                                | 2013                                | 2014                               | 2015                              |

|-----------|-----------------------------------------------------|-------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|-----------------------------------|

|           |                                                     | Family 14h<br>(00h-0Fh)<br>(Bobcat)       | Family 14h<br>(00h-0Fh)<br>(Bobcat) | Family 16h<br>(00h-0Fh)<br>(Jaguar) | Family 16h<br>(30h-3Fh)<br>(Puma+) | Family 16h<br>(30h-3Fh)<br>(Puma+ |

|           | 4P servers                                          |                                           |                                     |                                     |                                    |                                   |

| S         | 2P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Servers   | 1P servers                                          |                                           |                                     |                                     |                                    |                                   |

| Se        | (85-140 W)                                          |                                           |                                     |                                     |                                    |                                   |

|           | <b>High perf.</b><br>(~95-125 W)                    |                                           |                                     |                                     |                                    |                                   |

| Desktops  | Mainstream<br>(~65-100 W)                           |                                           |                                     |                                     |                                    |                                   |

| Des       | <b>Entry level</b><br>(~30-60 W)                    |                                           |                                     |                                     |                                    |                                   |

| oks       | High performance/<br>mainstream/entry<br>(~30-60 W) |                                           |                                     | Kabini A6                           |                                    |                                   |

| Notebooks | <b>Ultra portable</b><br>(~10-15 W)                 | Zacate<br>E-Series<br>Ontario<br>C-Series | Zacate<br>E1/E2                     | Kabini<br>A/E-Series                | Beema<br>A/E-Series                | Carrizo-L<br>A/L-Series           |

|           | <b>Tablet</b><br>(~5 W)                             | Desna<br>Z-Series                         |                                     | Temash<br>A Series                  | Mullins<br>A Series/E1             |                                   |

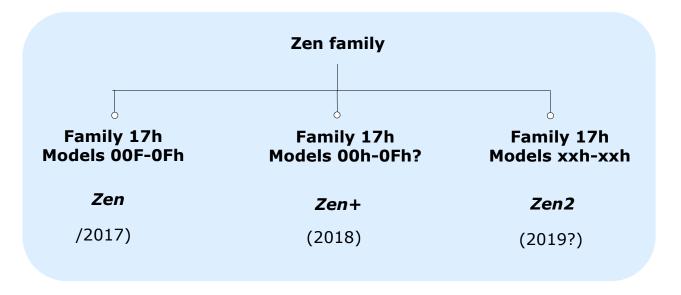

#### **The Zen family**

#### Brand names of AMD's Family 17h-based processor lines

|           | Launched in                             | 2017-2018                                                                               | 2018                                     | 2019?                             |

|-----------|-----------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

|           |                                         | <b>Family 17h</b><br>(00h-0Fh)<br>( <b>Zen</b> )                                        | Family 17h<br>(00h-0Fh)<br>(Zen+)        | Family 17h<br>(xxh-xxh)<br>(Zen2) |

|           | 4P servers                              |                                                                                         |                                          |                                   |

| Servers   | 2P servers                              | Epyc 7xx1                                                                               |                                          |                                   |

| erv       | 1P servers                              | Epyc 7xx1P                                                                              |                                          |                                   |

| S         | (85-140 W)                              |                                                                                         |                                          |                                   |

| S         | High perf.<br>(~95-125 W)               | ThreadRipper<br>(TR 1xxxX)                                                              | ThreadRipper<br>(TR 2xxxX/WX)            |                                   |

| Desktops  | Mainstream/<br>Entry level<br>(30-95 W) | Summit Ridge<br>(Ryzen 7/5/3 1xxx/1xxxX)<br>Raven Ridge (APU)<br>(Ryzen 7/5/3 2000G/GE) | Pinnacle Ridge<br>(Ryzen 7/5 2xxx/2xxxX) |                                   |

| ks        | High perf.<br>(~30-60 W)                |                                                                                         |                                          |                                   |

| Notebooks | Mainstream/Entry<br>(~20-30 W)          |                                                                                         |                                          |                                   |

| No        | Ultra portable<br>(~10-15 W)            | Raven Ridge (APU)<br>(Ryzen 7/5/3 2x00U)                                                |                                          |                                   |

|           | Tablet (~5 W)                           |                                                                                         |                                          |                                   |

#### Main features of AMD's server lines

|       | arch./<br>pping                      | Intro   | 4P Server<br>family name      | Series | Techn•    | Cores<br>(up to)  | L2<br>(up to)   | L3<br>(up to)       | Memory<br>(up to) | HT/ dir.<br>(up to)            | Sock<br>et |

|-------|--------------------------------------|---------|-------------------------------|--------|-----------|-------------------|-----------------|---------------------|-------------------|--------------------------------|------------|

|       | C0/CG                                | 4/2003  | Sledge-<br>hammer             | 800    | 130<br>nm | 1C                | 1 MB            | -                   | DDR-333           | HT 1.0:<br>3.2 GB/s            | 940        |

|       | E4/E6                                | 12/2004 | Athens                        | 800    | 90 nm     | 1C                | 1 MB            | -                   | DDR-400           | HT 2.0:<br>4.0 GB/s            | 940        |

| К8    | E1/E6                                | 4/2005  | Egypt                         | 800    | 90 nm     | 2C                | 2*1 MB          | -                   | DDR-400           | HT 2.0:<br>4.0 GB/s            | 940        |

|       | F2/F3                                | 8/2006  | Santa Rosa<br>(NPT)           | 8200   | 90 nm     | 2C                | 2*1 MB          | -                   | DDR2-667          | HT 2.0:<br>4.0 GB/s            | F          |

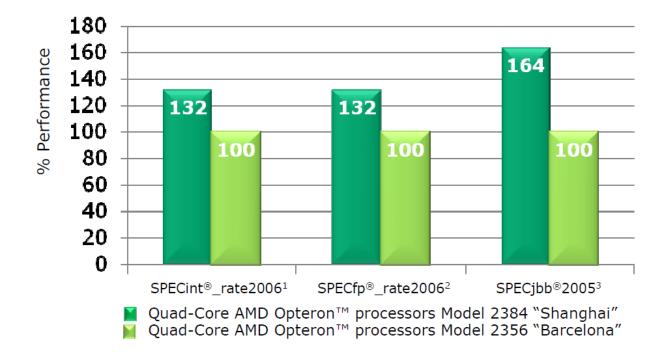

| K10   | BA/B1-<br>B3                         | 8/2007  | Barcelona                     | 8300   | 65 nm     | 4C                | 4*1/2 MB        | 2 MB                | DDR2-667          | HT 2.0:<br>4.0 GB/s            | F          |

|       | C2/C3                                | 11/2008 | Shanghai                      | 8300   | 45 nm     | 4C                | 4*1/2 MB        | 6 MB                | DDR2-800          | HT 2.0/3.0:<br>4.0/8.8<br>GB/s | F          |

| K10.5 | CE                                   | 6/2009  | Istambul                      | 8400   | 45 nm     | 6C                | 6*1/2 MB        | 6 MB                | DDR2-800          | HT 3.0:<br>9.6 GB/s            | F          |

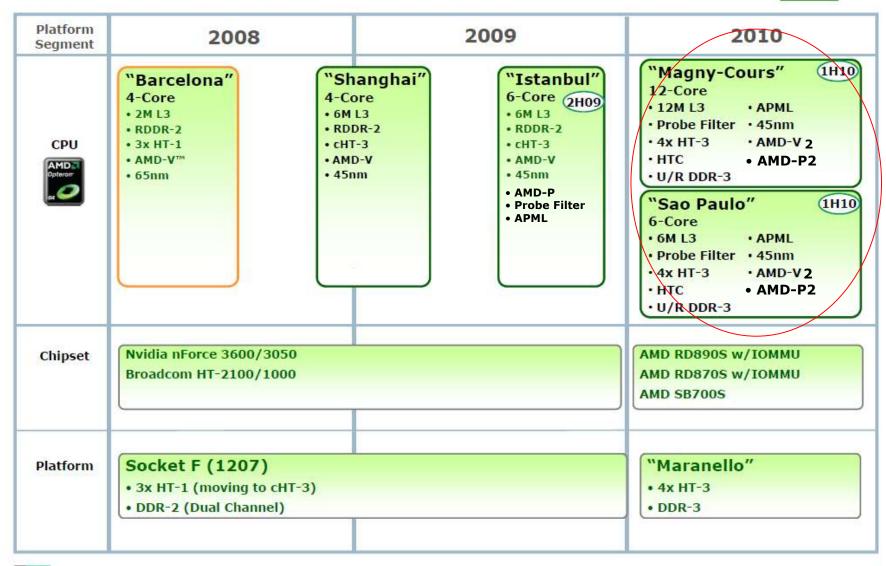

|       | D1                                   | 3/2010  | Magny Course<br>(2xIstambul)  | 6100   | 45 nm     | 2x6C              | 12*1/2<br>MB    | 6 MB                | DDR3-<br>1333     | HT 3.1:<br>12.8 GB/s           | G34        |

| Mod.  | <b>n 15h</b><br>00h-0Fh<br>ldozer)   | 11/2011 | Interlagos<br>(2xOrochi die)  | 6200   | 32 nm     | 2x4 CM<br>(2x8 C) | 2*4*<br>2 MB/CM | 2*<br>8MB/<br>4 CM  | DDR3-<br>1600     | HT 3.1:<br>12.8 GB/s           | G34        |

| Mod.  | <b>n. 15h</b><br>10h-1Fh<br>edriver) | 11/2012 | Abu Dhabi<br>(2 dies)         | 6300   | 32 nm     | 2x4 CM<br>(2x8 C) | 2*4*<br>2 MB/CM | 2*<br>8 MB/<br>4 CM | DDR3-<br>1866     | HT 3.1<br>12.8 GB/s            | G34        |

| -     | n. 17h<br>00h-0Fh                    | 6/2017  | Epyc (2S!!)<br>(4 dies/proc.) | 7000   | 14 nm     | 4x(2x4)<br>(32C)  | ½ MB/C          | 2 MB/C              | DDR4-<br>2666     | IFIS<br>75.8 GB/s              | SP3        |

#### **Evolution of main features of AMD's DP/MP servers**

| Bac         | e arch./    |         |                   | Techn    | Server family                |       |               |      | New I        | key featur | es                                             |      |        |

|-------------|-------------|---------|-------------------|----------|------------------------------|-------|---------------|------|--------------|------------|------------------------------------------------|------|--------|

|             | epping      | Intro.  | Core              | (nm)     | name                         | Cores | L3            | Mem. | On-die<br>MC | нт         | ISA<br>extension                               | NX   | Use    |

|             | B3/CG       | 4/2003  |                   | 130      | Sledgehammer                 | 1C    |               |      |              | 3xHT 1.0   | +SSE2                                          |      |        |

| К8          | E4          | 12/2004 |                   |          | Athens                       | IC    |               | DDR  |              |            |                                                |      |        |

| NO          | E1/E6       | 4/2005  | Sledge-<br>hammer | 90       | Egypt                        |       | - 1           |      |              |            | +SSE3                                          |      | S/DT/M |

|             | F2/F3       | 8/2006  |                   |          | Santa Rosa                   | 2C    |               |      |              | 3xHT 2.0   | ) +55E3                                        |      |        |

|             | G1/G2       | 12/2006 |                   | 65<br>65 | DT: Brisbane                 |       |               |      |              |            |                                                |      | DT     |

| K10         | B2/B3       | 9/2007  | Greyhound         | 65       | Barcelona⁵                   | 4C    |               | DDR2 |              |            |                                                |      | S/DT   |

|             | C2/C3       | 11/2008 |                   |          | Shanghai                     | 6C    | 6<br>MB       |      | +On-die      | 3xHT 3.0   |                                                | +NX  | S/DT/M |

| К10.        | CE          | 6/2009  | Greyhound<br>+    | 45       | Istambul                     |       |               |      | MC           |            | +SSE4a                                         | -bit | S/DT   |

|             | D1          | 3/2010  |                   |          | Magny Course<br>(2xIstambul) | 2x6C  | 2x<br>6 MB    |      |              |            |                                                |      | S      |

| Fam.<br>15h | Mod. 0xh    | 11/2011 | Bulldozer         | 32       | Interlagos<br>(2xOrochi)     | 2x8C  | 2x<br>8 MB    | DDR3 |              | 4xHT 3.1   | +SSE4.1/4.2,<br>AES, AVX,<br>XOP,<br>FMA4,CMUL |      | S/DT   |

| 1511        | Mod.<br>1xh | 11/2012 | Piledriver        |          | Abu Dhabi<br>(Dual dies)     |       |               |      |              |            | +FMA3,<br>CVT16, BMI,<br>TBM                   |      | S/DT/M |

| Fam<br>17h  | Mod.<br>0xh | 6/2017  | Zen               | 14       | DT: Epic<br>(4 dies)         | 4x8C  | 2 MB/<br>core | DDR4 |              | IFIS       | na.                                            |      | S/HED  |

<sup>1</sup> x4UMI: 4x PCIe 2.0

2 ISA enh.: +AES, +AVX, +FMA4, +XOP, +PCLMULQDQ <sup>3</sup> PCIe 1.0/2.0

<sup>4</sup> 3DNow! Prof. dropped

<sup>5</sup> The Barcelona die supports already 4xHT 3.0 and DDR3 but Socket F used for DP/MP servers restricts supported features to 3xHT 2.0 and DDR2

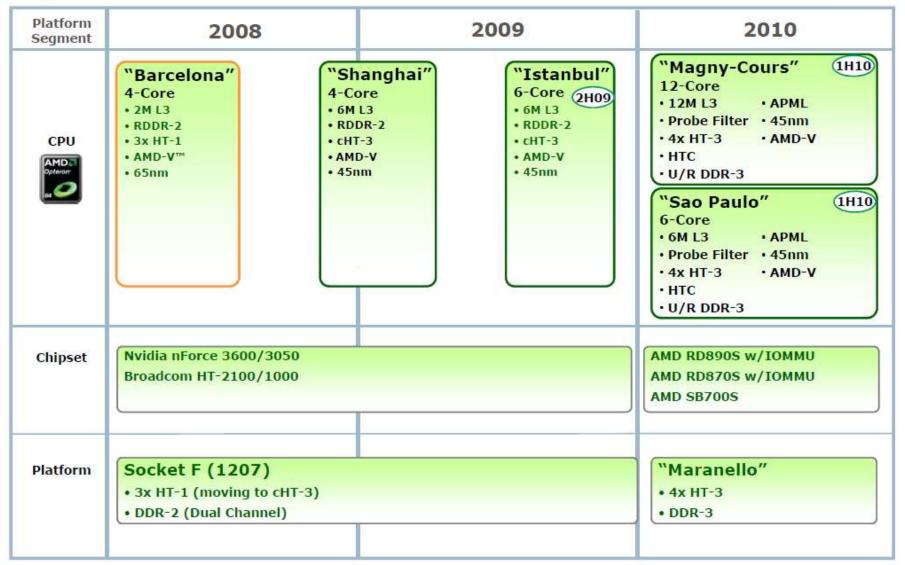

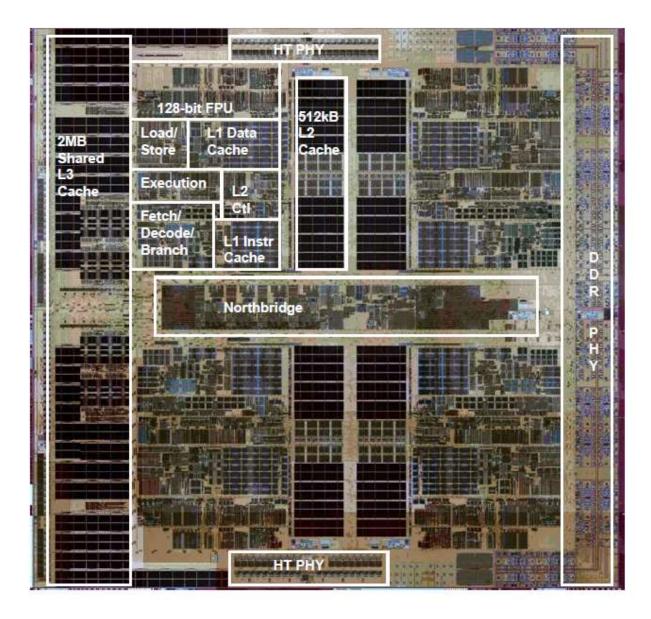

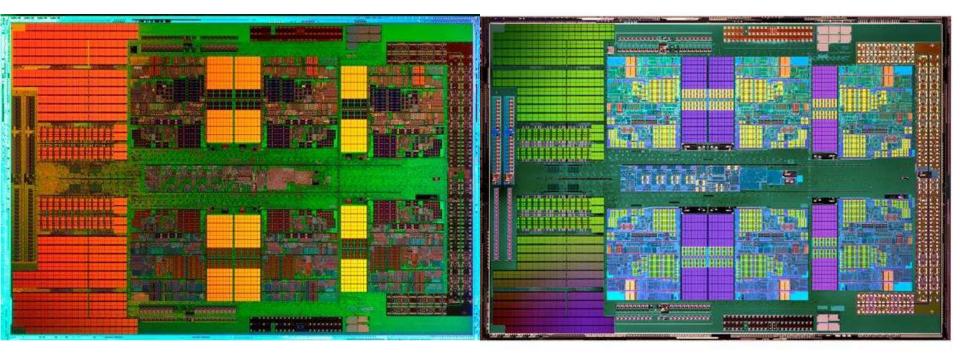

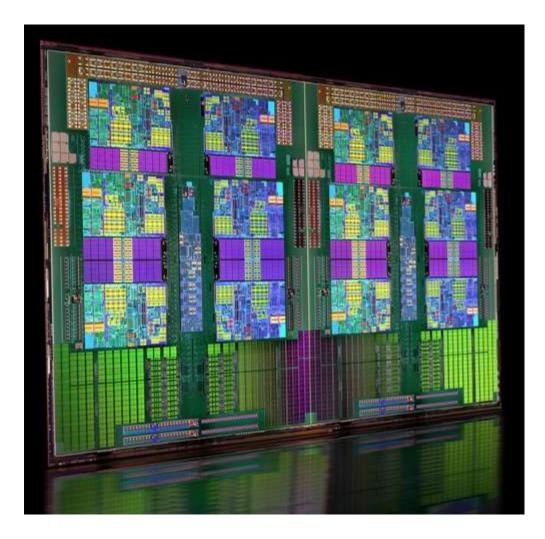

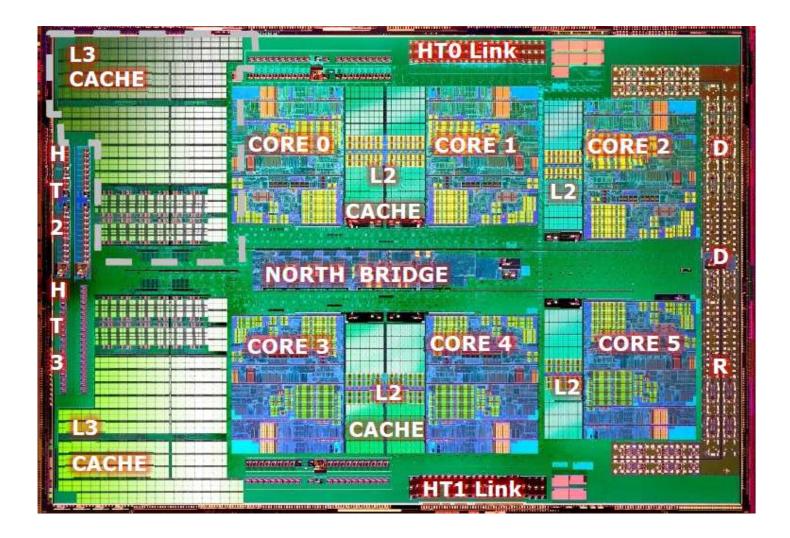

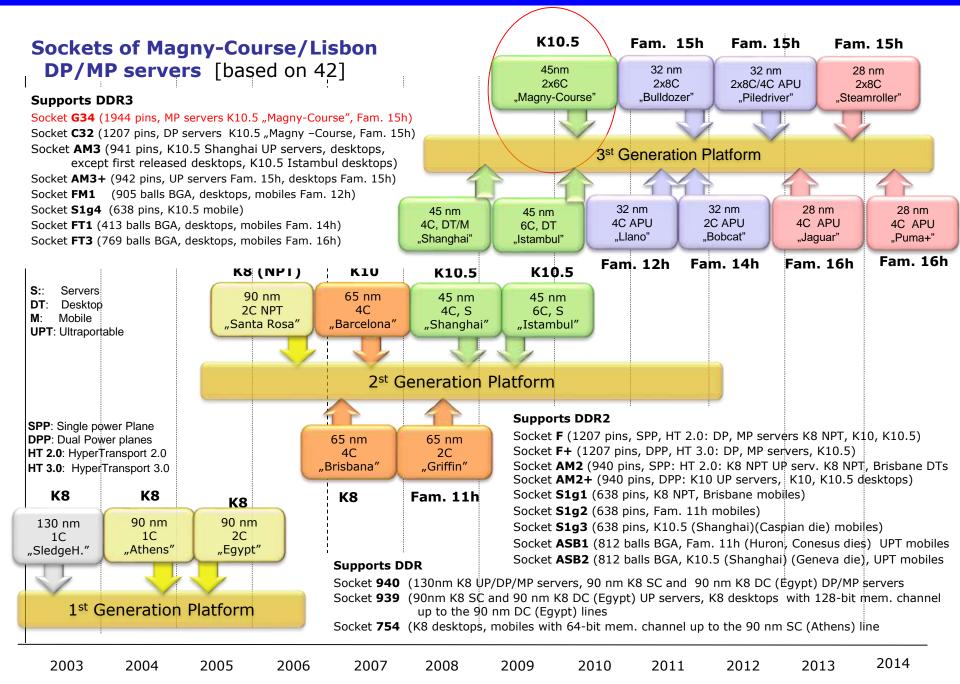

#### **Overview of subsequent K10/K10.5** implementations (as used in MP/DP servers) [88]

65 nm

45nm

# MP/DP Platforms – 8000 and 2000 Series

#### Key parameters of subsequent versions of the HyperTransport standard [58]

| HT<br>version | Year | Max. HT<br>frequency | Max.<br>link width | Max. bandwidth at 16-bit unidirectional |

|---------------|------|----------------------|--------------------|-----------------------------------------|

| 1.0           | 2001 | 800 MHz              | 32-bit             | 3.2 GB/s                                |

| 1.1           | 2002 | 800 MHz              | 32-bit             | 3.2 GB/s                                |

| 2.0           | 2004 | 1.4 GHz              | 32-bit             | 5.6 GB/s                                |

| 3.0           | 2006 | 2.6 GHz              | 32-bit             | 10.4 GB/s                               |

| 3.1           | 2008 | 3.2 GHz              | 32-bit             | 12.8 GB/s                               |

# Main features of AMD's high-performance desktop lines (except Bulldozer-based lines)

|                | arch./<br>oping       | Intro             | High<br>perf. DT<br>family | Series          | Techn.    | Core<br>count<br>(up to) | L2<br>(up to) | L3<br>(up<br>to) | Memory<br>(up to)      | HT/ dir.<br>(up to) | Socket      |

|----------------|-----------------------|-------------------|----------------------------|-----------------|-----------|--------------------------|---------------|------------------|------------------------|---------------------|-------------|

|                | CG                    | 9/2003            | Claw-<br>Hammer            | Athlon<br>64    | 130<br>nm | 1                        | 1 MB          | -                | DDR-400                | HT 2.0:<br>4.0 GB/s | 754/<br>939 |

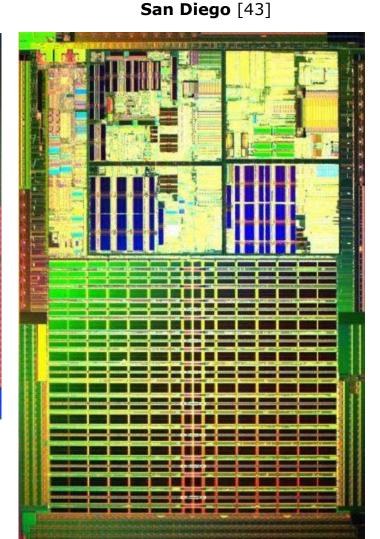

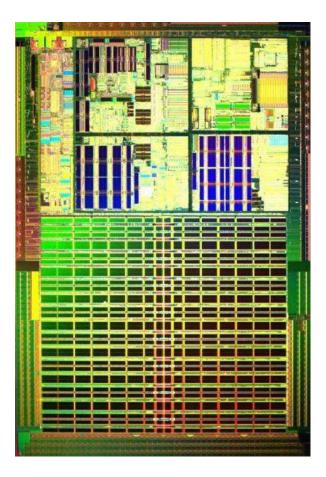

| К8             | E4                    | 4/2005            | San<br>Diego               | Athlon<br>64    | 90 nm     | 1                        | 1 MB          | -                | DDR-400                | HT 2.0:<br>4.0 GB/s | 939         |

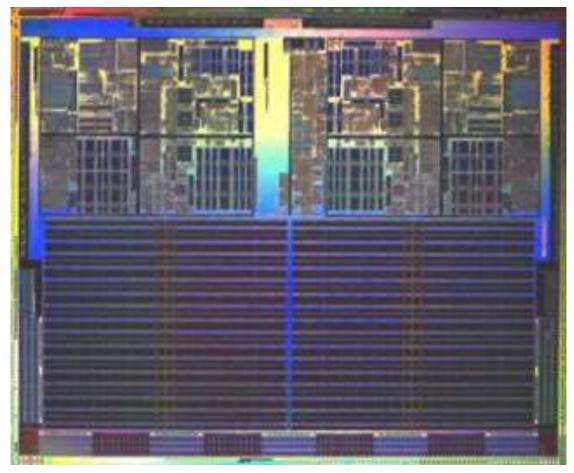

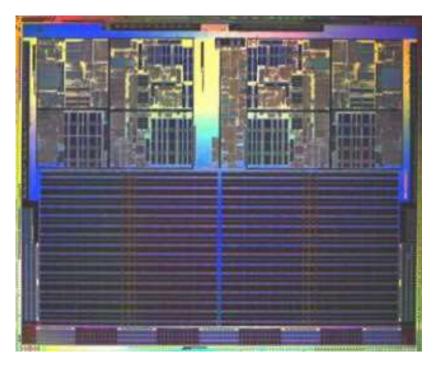

| Kð             | E6                    | 5/2005            | Toledo                     | Athlon<br>64 X2 | 90 nm     | 2                        | 2*1 MB        | -                | DDR-400                | HT 2.0:<br>4.0 GB/s | 939         |

|                | E2/E3                 | 5/2006            | Windsor                    | Athlon<br>64 X2 | 90 nm     | 2                        | 2*1 MB        | -                | DDR2-800               | HT 2.0:<br>4.0 GB/s | AM2         |

| К10            | B2<br>B3              | 11/2007<br>3/2008 | Agena                      | Phenom<br>X4    | 65 nm     | 4                        | 4*1⁄2 MB      | 2 MB             | DDR2-1066              | HT 3.0:<br>8.0 GB/s | AM2+        |

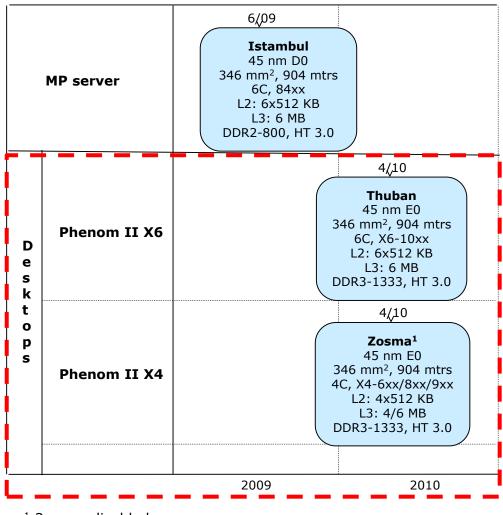

| K10.5          | C2<br>C2/C3           | 1/2009<br>2/2009  | Deneb                      | Phenom<br>II X4 | 45 nm     | 4                        | 4*1⁄2MB       | 6 MB             | DDR2-1066<br>DDR3-1333 | HT 3.0:<br>8.0 GB/s | AM2+<br>AM3 |

| <b>R10.5</b>   | E0                    | 4/2010            | Thuban                     | Phenom<br>II X6 | 45 nm     | 6                        | 6*1⁄2MB       | 6 MB             | DDR2-1066<br>DDR3-1333 | HT 3.0:<br>8.0 GB/s | AM3         |

| Fam. 11        | <b>h</b> (Griffin)    | -                 | -                          | -               | -         | -                        | -             | -                | -                      | -                   | -           |

|                | <b>1. 12h</b><br>ano) | 6/2011            | Llano                      | Fusion<br>A8    | 32 nm     | 4                        | 4*1 M         | -                | DDR3-1866              | UMI:<br>5 GT/s      | FM1         |

| Fam. 17h       | <b>h</b> (Zen)        | 3/2017            | Summit<br>Ridge            | Ryzen 7         | 14 nm     | 8                        | 8x1/2 MB      | 16 MB            | DDR4-2993              | -                   | AM4         |

| Fam. 17 (Zen+) |                       | 4/2018            | Pinnacle<br>Ridge          | Ryzen 7         | 12 nm     | 8                        | 8x1/2 MB      | 16 MB            | DDR4-2933              | -                   | AM4         |

# Main features of AMD's high-performance desktop lines (except Zen-based lines)

|                                                   | arch./<br>oping       | Intro             | High<br>perf. DT<br>family | Series          | Techn.    | Core<br>count<br>(up to) | L2<br>(up to) | L3<br>(up<br>to) | Memory<br>(up to)      | HT/ dir.<br>(up to)     | Socket      |

|---------------------------------------------------|-----------------------|-------------------|----------------------------|-----------------|-----------|--------------------------|---------------|------------------|------------------------|-------------------------|-------------|

|                                                   | CG                    | 9/2003            | Claw-<br>Hammer            | Athlon<br>64    | 130<br>nm | 1                        | 1 MB          | -                | DDR-400                | HT 2.0:<br>4.0 GB/s     | 754/<br>939 |

| К8                                                | E4                    | 4/2005            | San<br>Diego               | Athlon<br>64    | 90 nm     | 1                        | 1 MB          | -                | DDR-400                | HT 2.0:<br>4.0 GB/s     | 939         |

| NO                                                | E6                    | 5/2005            | Toledo                     | Athlon<br>64 X2 | 90 nm     | 2                        | 2*1 MB        | -                | DDR-400                | HT 2.0:<br>4.0 GB/s     | 939         |

|                                                   | E2/E3                 | 5/2006            | Windsor                    | Athlon<br>64 X2 | 90 nm     | 2                        | 2*1 MB        | -                | DDR2-800               | HT 2.0:<br>4.0 GB/s     | AM2         |

| К10                                               | B2<br>B3              | 11/2007<br>3/2008 | Agena                      | Phenom<br>X4    | 65 nm     | 4                        | 4*1⁄2 MB      | 2 MB             | DDR2-1066              | HT 3.0:<br>8.0 GB/s     | AM2+        |

| K10.5                                             | C2<br>C2/C3           | 1/2009<br>2/2009  | Deneb                      | Phenom<br>II X4 | 45 nm     | 4                        | 4*1⁄2MB       | 6 MB             | DDR2-1066<br>DDR3-1333 | HT 3.0:<br>8.0 GB/s     | AM2+<br>AM3 |

| K10.5                                             | E0                    | 4/2010            | Thuban                     | Phenom<br>II X6 | 45 nm     | 6                        | 6*1⁄2MB       | 6 MB             | DDR2-1066<br>DDR3-1333 | HT 3.0:<br>8.0 GB/s     | AM3         |

| Fam. 11                                           | <b>ı</b> (Griffin)    | -                 | -                          | -               | -         | -                        | -             | -                | -                      | -                       | -           |

|                                                   | <b>1. 12h</b><br>ano) | 6/2011            | Llano                      | Fusion<br>A8    | 32 nm     | 4                        | 4*1 M         | -                | DDR3-1866              | UMI:<br>5 GT/s          | FM1         |

| Fam. 14h                                          | <b>1</b> (Bobcat)     | -                 | -                          | -               | -         | -                        | -             | -                | -                      | -                       | -           |

| <b>Fam. 15h</b><br>Models 00h-0Fh<br>(Bulldozer)  |                       | 10/2011           | Zambezi                    | FX-series       | 32 nm     | 4 CM<br>(8 C)            | 4x2 MB/CM     | 8 MB             | DDR3-1866              | HT 3.1:<br>12.8<br>GB/s | AM3+        |

| <b>Fam. 15h</b><br>Models 10h-1Fh<br>(Piledriver) |                       | 10/2012           | Vishera                    | FX-series       | 32 nm     | 4 CM<br>(8 C)            | 4*2 MB/CM     | 8 MB             | DDR3-1866              | HT 3.1:<br>12.8<br>GB/s | AM3+        |

| No further Fam. 15h<br>based lines                |                       | -                 | -                          | -               | -         | -                        | -             | -                | -                      | -                       | -           |

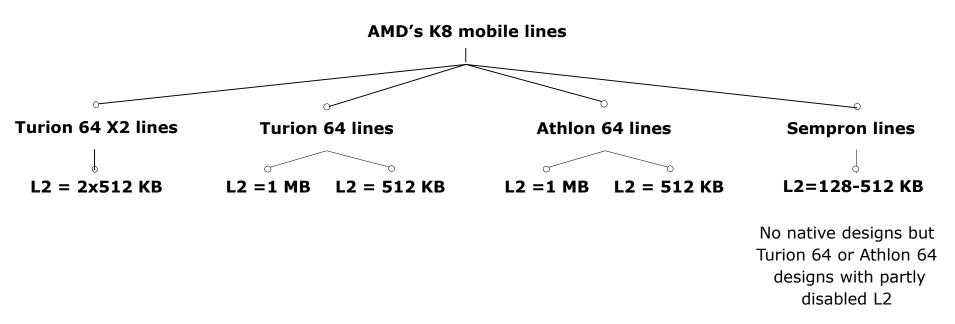

#### Main features of Hammer (K8 – K 10.5)-based high performance mobile lines

| Base arch./<br>stepping |        | Intro  | High perf.<br>mobile<br>family<br>name | Series                 | Techn. | Core<br>count<br>(up to) | L2<br>(up to)                    | L3 | Memory<br>(up to) | HT/ dir.<br>(up to) | Sock<br>et |

|-------------------------|--------|--------|----------------------------------------|------------------------|--------|--------------------------|----------------------------------|----|-------------------|---------------------|------------|

|                         | C0, CG | 9/2003 | Clawhammer                             | Mobile<br>Athlon<br>64 | 130 nm | 1                        | 512 KB                           | -  | DDR-400           | HT 1.0:<br>3.2 GB/s | 754        |

| K8                      | E5     | 3/2005 | Lancaster                              | Turion<br>64           | 90 nm  | 1                        | 1 MB                             | -  | DDR-400           | HT 1.0:<br>3.2 GB/s | 754        |

|                         | F2     | 5/2006 | Trinidad                               | Turion<br>64 X2        | 90 nm  | 2                        | 2*512 KB                         | -  | DDR2-667          | HT 1.0:<br>3.2 GB/s | S1         |

| K10                     | -      | -      | -                                      | -                      | -      | -                        | -                                | -  | -                 | -                   | -          |

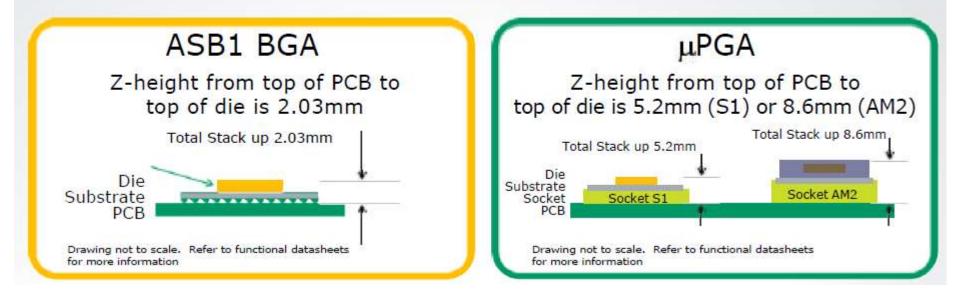

| K10.5                   | DA-C2  | 9/2009 | Caspian                                | Turion<br>II           | 45 nm  | 2                        | 2*512 KB/<br>2*1 MB <sup>1</sup> | -  | DDR2-800          | HT 3.0:<br>7.2 GB/s | S1g3       |

|                         | DA-C3  | 5/2010 | Champlain                              | Turion<br>X4           | 45 nm  | 4                        | 4*512 KB                         | -  | DDR3-1066         | HT 3.0:<br>7.2 GB/s | S1g4       |

<sup>1</sup>: 2\*512 KB for Turion II, 2\*1 MB for Turion II Ultra

#### Main features of the Intermediate-based high-performance mobile lines

| Base arch./<br>stepping          | Intro  | High perf.<br>mobile<br>family name | Series                | Techn. | Core<br>count<br>(up to) | L2<br>(up to)                       | L3 | Memory<br>(up to) | HT/ dir.<br>(up to)  | Sock<br>et |

|----------------------------------|--------|-------------------------------------|-----------------------|--------|--------------------------|-------------------------------------|----|-------------------|----------------------|------------|

| Family 11h<br>(K11)<br>(Griffin) | 6/2008 | Lion (no APU)<br>(not SoC)          | Turion<br>X2<br>Ultra | 65 nm  | 2                        | 2x512<br>KB/<br>2*1 MB <sup>2</sup> | -  | DDR2-800          | HT 3.0:<br>10.4 GB/s | S1g2       |

| Family 12h<br>(K12)<br>(Llano)   | 6/2011 | Llano (APU)<br>(not SoC)            | Fusion<br>A8 M        | 32 nm  | 4                        | 4x1 MB                              | -  | DDR3-1600         | -                    | FM1        |

#### Main features of Cat and Zen-based ultra-portable mobile lines

| Base arch./<br>stepping                   | Intro       | Ultra-<br>portable<br>mobile<br>family | Series          | Techn. | Core count<br>(up to)                                  | L2<br>(up to)               | L3            | GPU<br>(APU) | Memory<br>(up to) | TDP<br>[W] | Socke<br>t   |

|-------------------------------------------|-------------|----------------------------------------|-----------------|--------|--------------------------------------------------------|-----------------------------|---------------|--------------|-------------------|------------|--------------|

|                                           | 1/2011      | Zacate<br>(not SoC)                    | E<br>Series     | 40 nm  | 2                                                      | 512 KB/<br>core<br>Private  | -             | Yes          | DDR3L-<br>1333    | 18         | FT1<br>(BGA) |

| <b>Family14h</b><br>(00h-0Fh)<br>(Bobcat) | 6/2012      | Zacate<br>(not SoC)                    | E1/E2<br>Models | 40 nm  | 2                                                      | 512 KB/<br>core<br>Private  | -             | Yes          | DDR3L-<br>1333    | 18         | FT1<br>(BGA) |

|                                           | 1/2011      | Ontario                                | C<br>Series     | 40 nm  | 2                                                      | 512 KB/<br>core<br>private  | -             | Yes          | DDR3-<br>1066     | 9          | FT1<br>(BGA) |

| Family 16h<br>(10H-1fH)<br>(Jaguar)       | 5/2013      | Kabini<br>(SoC)                        | A<br>Series     | 28 nm  | 4 00100                                                | 2 MB<br>shared              | -             | Yes          | DDR3L-<br>1866    | 9/<br>15   | FT3          |

| Family 16h                                | 4/2014      | Beema<br>(SoC)                         | A<br>Series     | 28 nm  | 4 cores<br>with a<br>shared L2<br>cache                | 2 MB<br>shared              | -             | Yes          | DDR3L-<br>1866    | 15         | FT3b         |

| (30H-3fH)<br>(Puma+)                      | 5/2015      | Carrizo-L<br>(SoC)                     | A<br>Series     | 28 nm  |                                                        | 2 MB<br>shared              | -             | Yes          | DDR3L-<br>1866    | 10/<br>15  | FP4          |

| Family 17h<br>(00H-0fH)<br>(Zen)          | 10/201<br>7 | Raven<br>Ridge<br>(SoC)                | Ryzen<br>7/5/3  | 14 nm  | 4-core CCX,<br>private L2<br>and shared<br>L3 cache(s) | <sup>1</sup> ⁄2 MB/<br>core | 1 MB/<br>core | Yes          | DDR4-<br>2400     | 15         | AM4          |

APU: Accelerated Processing Unit (CPU +GPU) CCX: Core CompleX

<sup>2</sup>: 2\*512 KB for Turion X2, 2\*1 MB for Turion X2 Ultra

UMI: Universal Media Interface

Remark

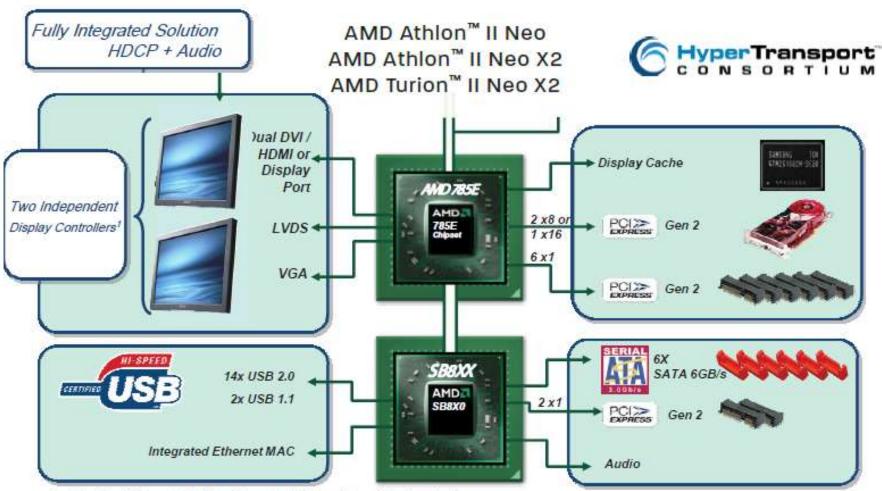

AMD's chipsets

- AMD started offering own chipsets to their processors with their 640/645 chipset (yet licensed from VIA) in 1997 to support their K6, Cyrix 6x6 and Pentium processors.

- It was followed by the in-house developed 750 chipset intended for the Athlon Model 1 (1999).

- Since then AMD usually provides own chipsets for their processors.

#### Introducing the platform concept by AMD-1

- For years AMD disdained the platform approach arguing that unlike Intel's Centrino platform they want to give OEMs the choice to select components from a wide range of suppliers.

But OEMs prefer platforms since its components are already tested and their integration is aready validated by the manufacturer [6].

- Also manufacturers benefit from the platform concept as it motivates OEMs to buy all key components of a computer system from the same manufacturer.

- For the reasons mentioned, two to three years after Intel, also AMD introduced the platform approach.

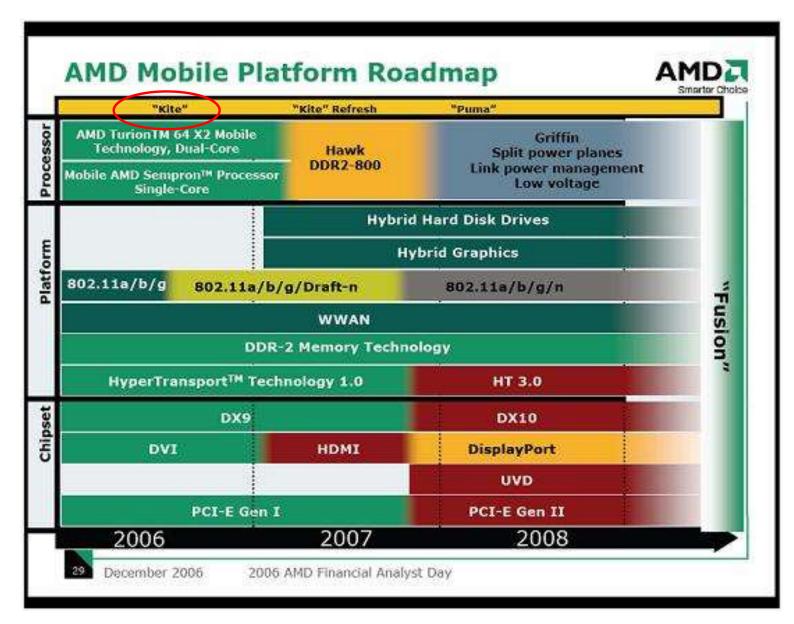

- First, AMD announced their platform concept in the mobile segment (like Intel) with their Kite platform in 2006.

- (This platform supported the K8-based dual core Turion 64 X2 and sigle core Turion 64 and Mobile Sempron processors, as shown in the next Figure).

#### AMD's 2006 mobile roadmap showing their first platform, the Kite mobile platform [130]

# Main features of the Kite platform [7]

Introduced in 2006

| AMD mobile     | Kite platform                                                                                  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------|--|--|--|

|                | Processors - Socket S1                                                                         |  |  |  |

| Mobile         | <ul> <li>Mobile Sempron single-core 64-bit processor (codenamed<br/>Keene), or</li> </ul>      |  |  |  |

| processor      | <ul> <li>Turion 64 single-core 64-bit processor (codenamed<br/><i>Richmond</i>), or</li> </ul> |  |  |  |

|                | <ul> <li>Turion 64 X2 dual-core 64-bit processor (codenamed<br/>Taylor, Trinidad)</li> </ul>   |  |  |  |

| Mobile chipset | <ul> <li>DVI and HyperTransport 1.0</li> </ul>                                                 |  |  |  |

| Mobile chipset | DDR2-667 SO-DIMM                                                                               |  |  |  |

| Mobile support | Wireless IEEE 802.11 b/g mini-PCIe WiFi adapter                                                |  |  |  |

#### Introducing the platform concept by AMD-2

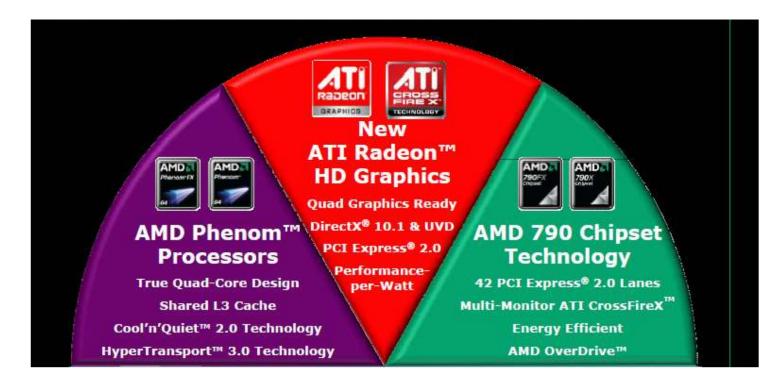

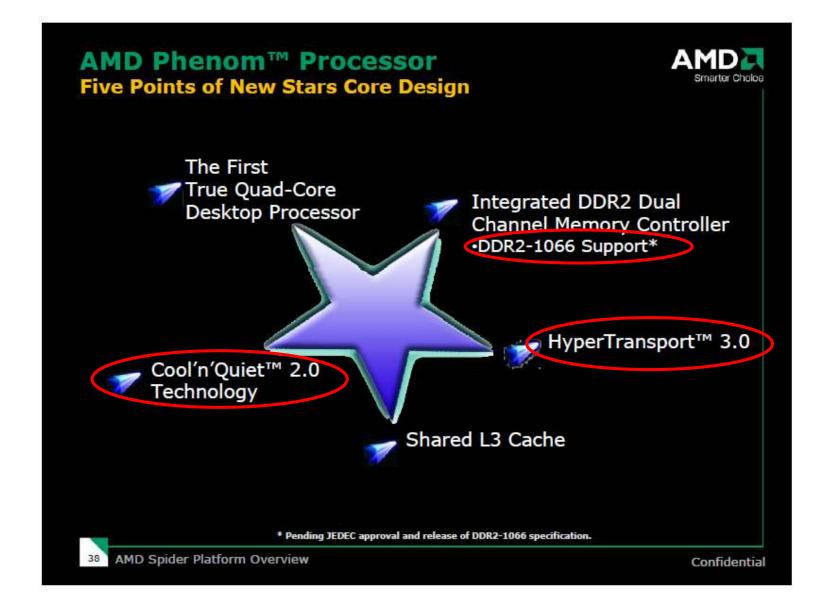

• In the desktop segment AMD introduced their platform concept in 2007 with their Spider platform.

The Spider platform supported the K10 Barcelon-based Phenom X2/X4 processors, as indicated in the next Figure.

The Phenom X2/X4 processors were built on the K10-based Agena and Kuma desktop cores and targeted gamers).

#### AMD's first desktop platform: the K10 Barcelona based Spider platform (2007) [8]

#### Introducing the platform concept by AMD-3

AMD's platform concept has a peculiarity, as AMD's desktop platforms cover - beyond the usual main components processor and chipset - also the graphics cards (see next slide).

This reflects AMD's strategy to support aggressively graphics, leading to the acquisition of one of the major graphics card supplier ATI in 2006.

#### Remark

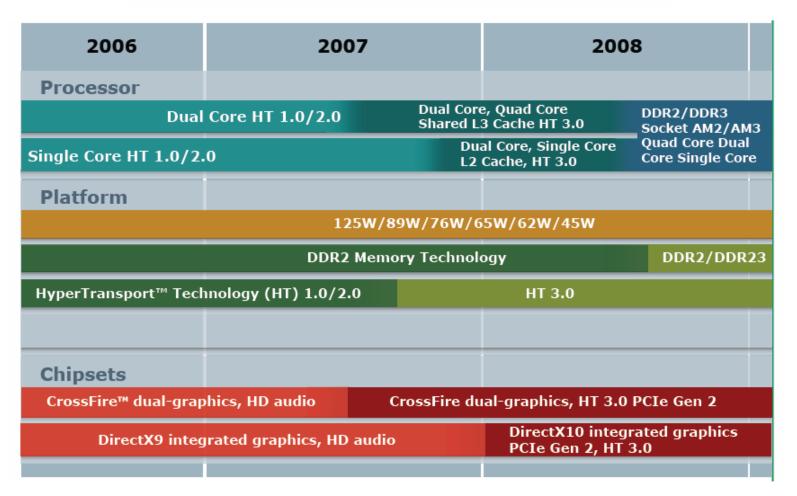

AMD revealed already in 2006 their desktop roadmap, nevertheless without publishing actual platform designations, as indicated below [131].

# **AMD Desktop Platform Roadmap**

AMD's first desktop roadmap with platform names (published in 2007) [128]

# AMD Desktop Performance Platform Roadmap: 2007-2009 (Planned)

| 1              | Matfems<br>Segment | 2007                                                                     | 2000                                                                                          | 2009                                                                          |                                                                     |

|----------------|--------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 4              |                    | Spider                                                                   | Leo                                                                                           | Python                                                                        |                                                                     |

|                |                    | CPU                                                                      | AMD Phenom X4, X2<br>2MB L3, HT3.0<br>EVP, Cool'n'Quiet<br>Technology<br>AM2+ Package<br>65nm | AMD Phenom X4, X2<br>6MB L3, HT3.0<br>EVP, Cool'n'Quiet<br>Technology<br>45nm | Native Quad-Core, DDR3<br>AM3 Package<br>32nm<br>DX10/11UVD 2nd Gen |

| distant in the | Chipset            | RD7XX Series<br>PCI-E Gen 11, HT3.0                                      | RD7XX Series<br>CrossFire 2X- 4X GPUs<br>PCI-E Gen 11<br>HT3.0                                | RD9XX                                                                         |                                                                     |

|                | GPU                | ATI Radeon HD 2900<br>GDDR3/GDDR4, DX10                                  | R7XX Series<br>DX 10+<br>55nm                                                                 | Next-generation GPU                                                           |                                                                     |

|                | Platform           | DDR2, HT1.0<br>Discrete or Integrated<br>Standard & Performance<br>Power | DDR2, HT3.0<br>Discrete or Integrated<br>Standard & Performance<br>Power                      | DDR3, HT3.0<br>Integrated Graphics<br>Standard & Performance<br>Power         |                                                                     |

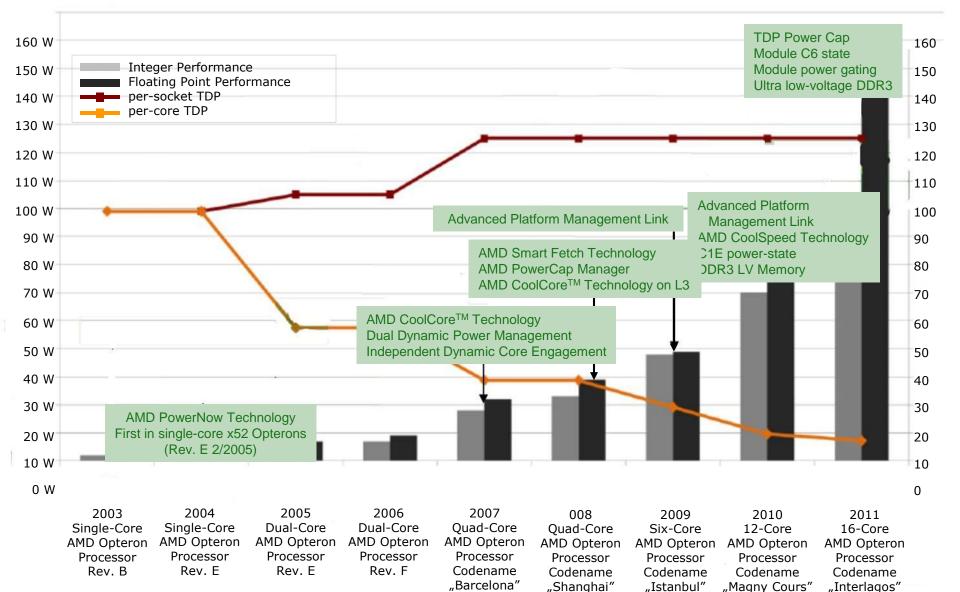

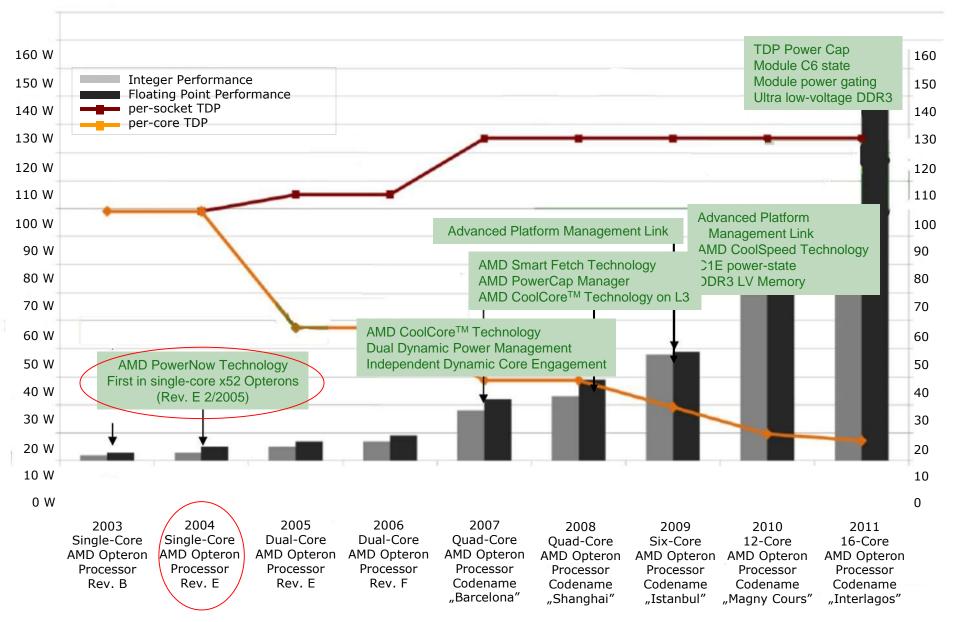

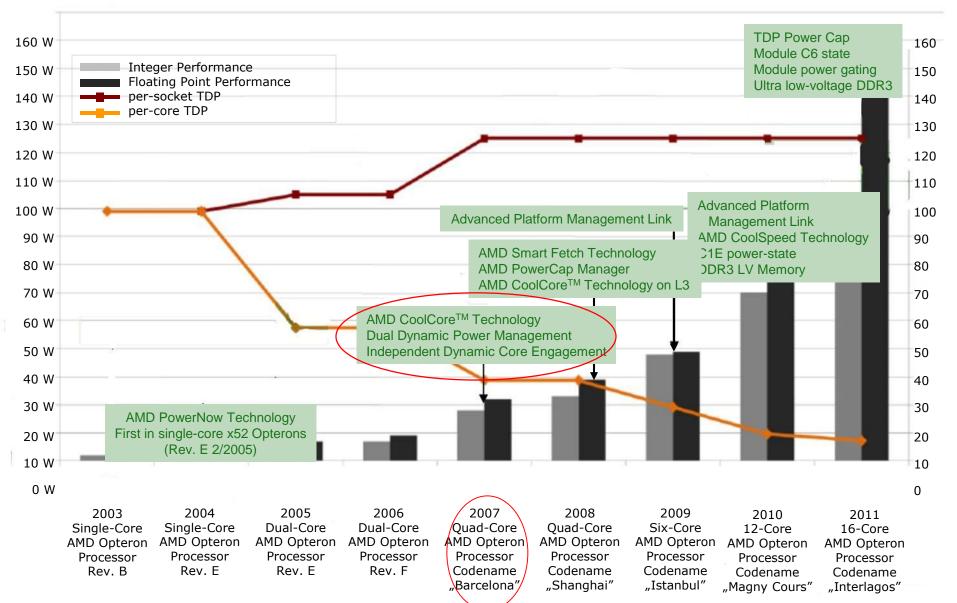

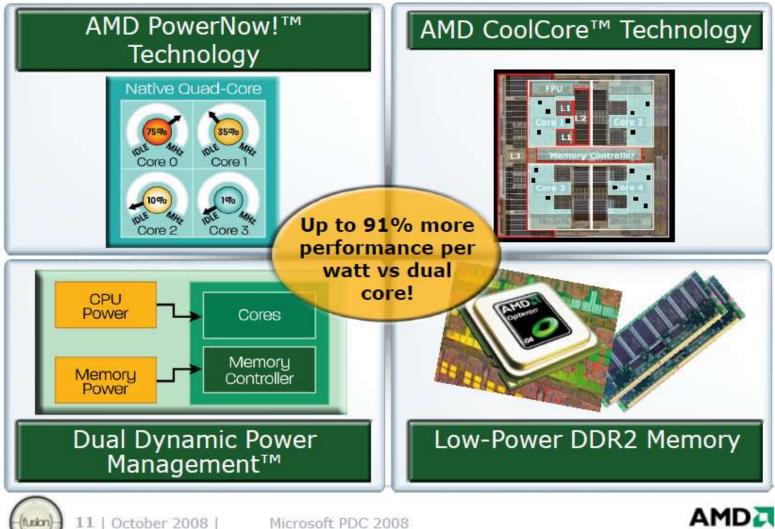

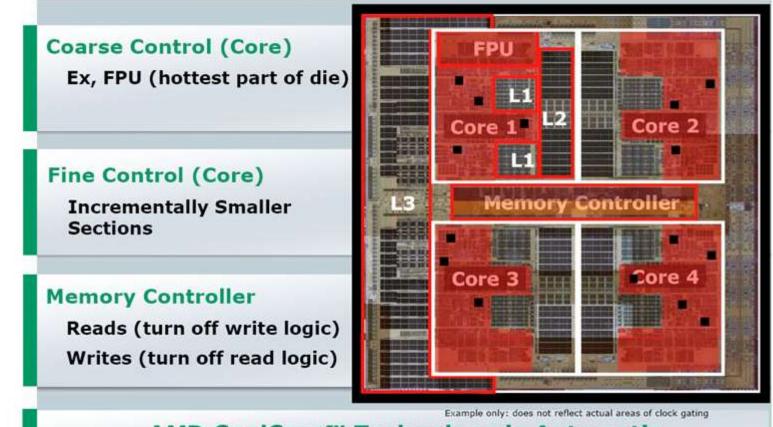

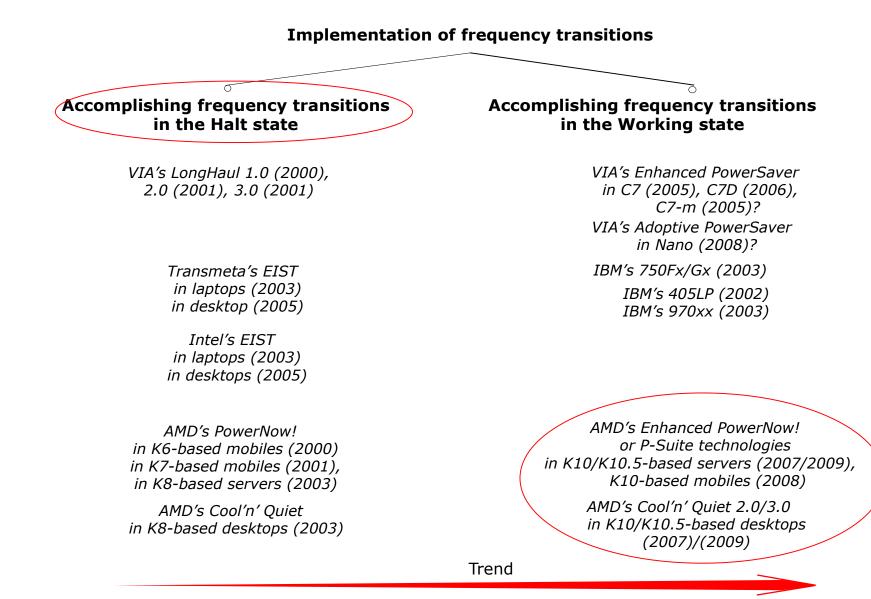

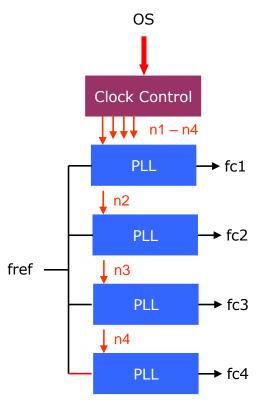

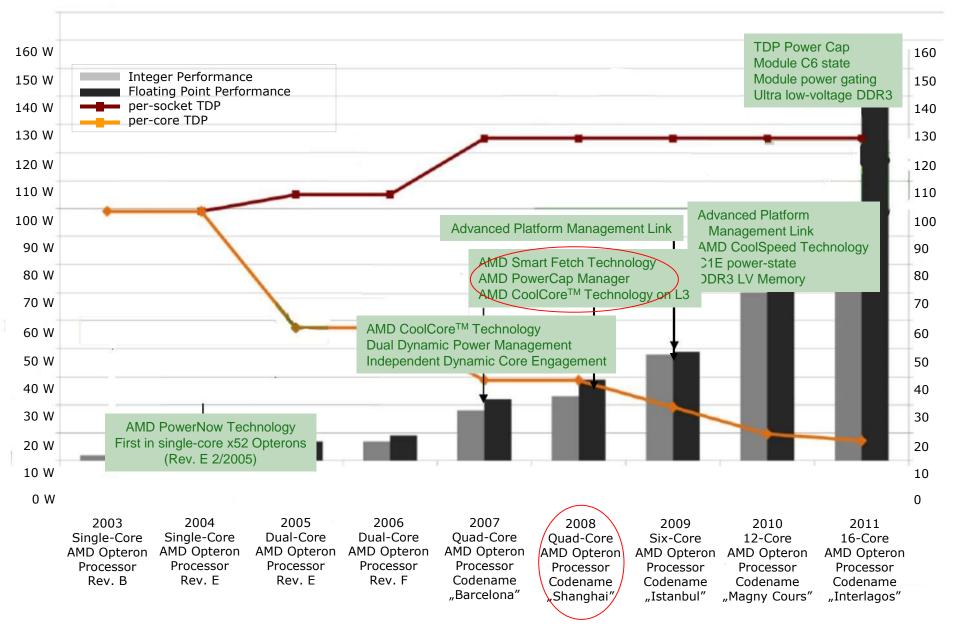

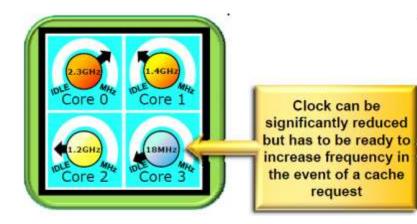

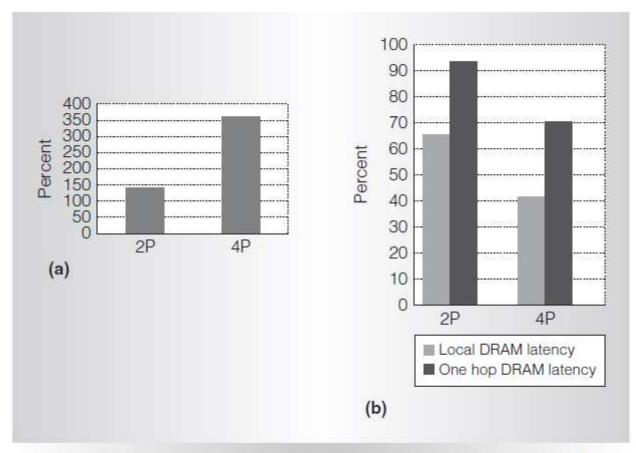

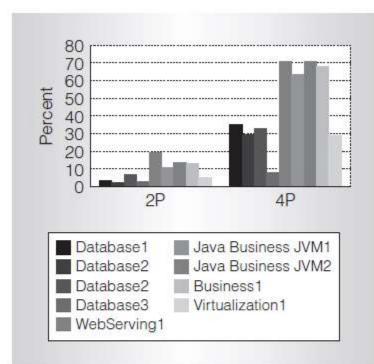

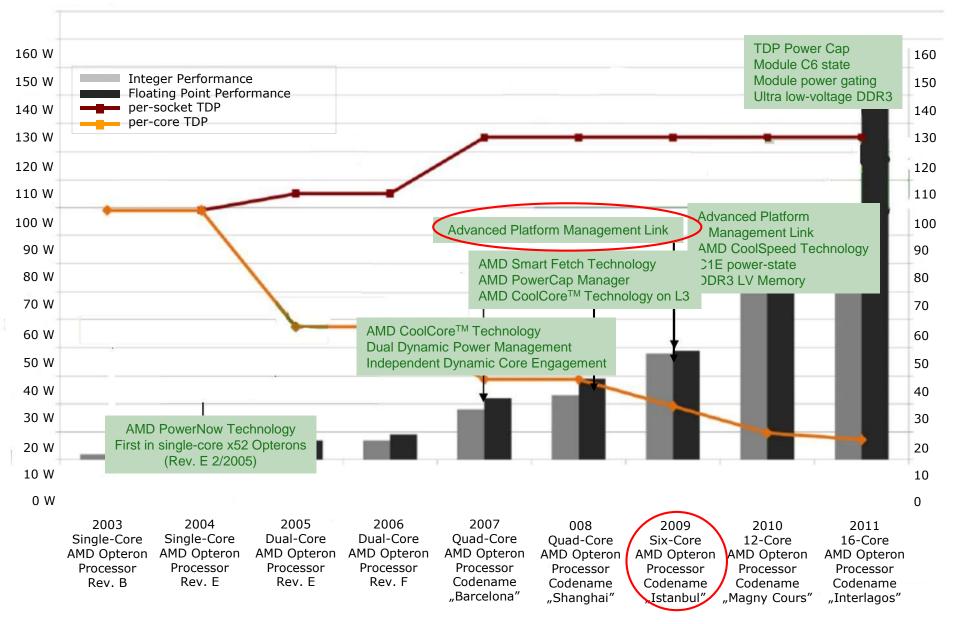

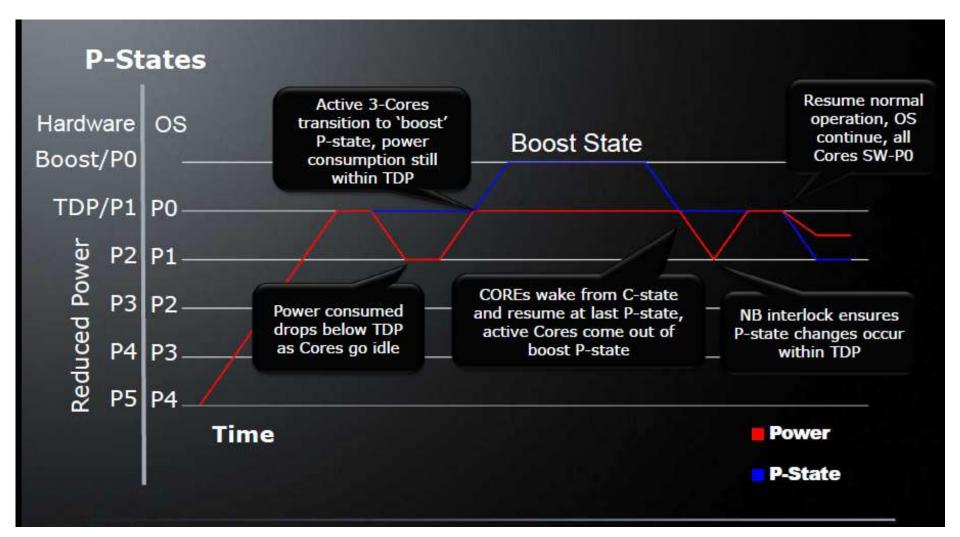

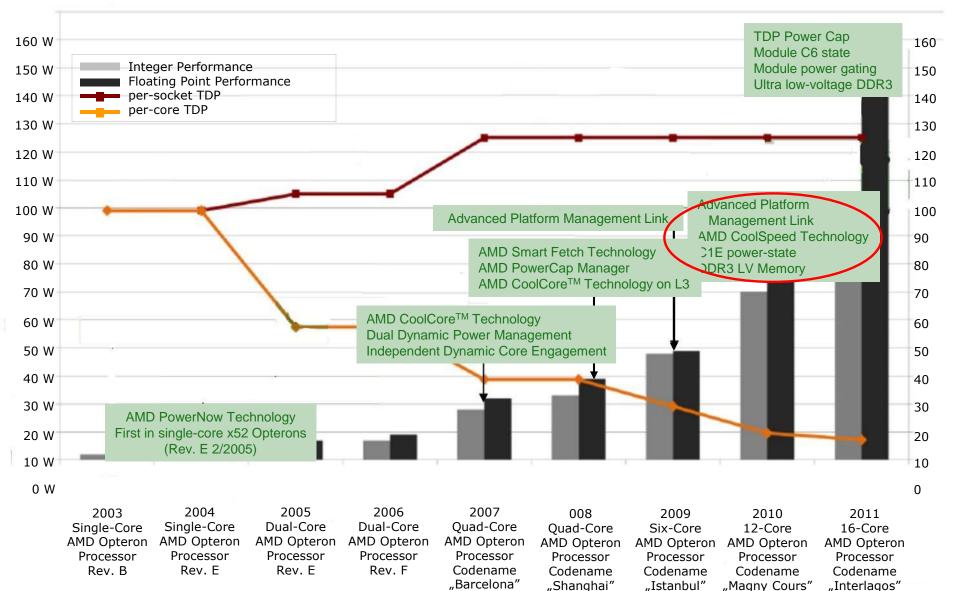

#### AMD's power management techniques K8 – Family 15h (Bulldozer) (based on [53])

# 1. Introduction to AMD's processor families (62)

# 2. AMD's 32-bit x86 families

#### 2. AMD's 32-bit x86 families

#### **Overview and major innovations in AMD's K5/K6 families**

| CPU Family               | Intro.               | CPU core                 | Brand name | Techn.<br>(µm)       | New key feature                                               | Typ.<br>Application |

|--------------------------|----------------------|--------------------------|------------|----------------------|---------------------------------------------------------------|---------------------|

| К5                       | 1996                 |                          | К5         | 0.5/0.35             | 2. gen. superscalar (32-bit),<br>Pentium competitor           | DT                  |

| К6                       | 1997                 |                          | К6         | 0.35/0.25            | 2.5 gen. superscalar, MMX<br>(NexGen design)                  | DT/M                |

| K6-2                     | 1998                 | Chomper                  | К6         | 0.25                 | 3. gen. superscalar, 3DNow!                                   | DT/M                |

| K6III<br>K6-2+<br>K6III+ | 1999<br>2000<br>2000 | Sharptooth<br>na.<br>na. | К6         | 0.25<br>0.18<br>0.18 | On-die L2<br>PowerNow! <sup>1</sup><br>PowerNow! <sup>1</sup> | DT/M                |

<sup>1</sup> PowerNow! was introduced in the Mobile K6-2+ and Mobile K-III+ processors in 2000

<sup>2</sup> Athlon: Attained performance lead over Intel's Pentium III

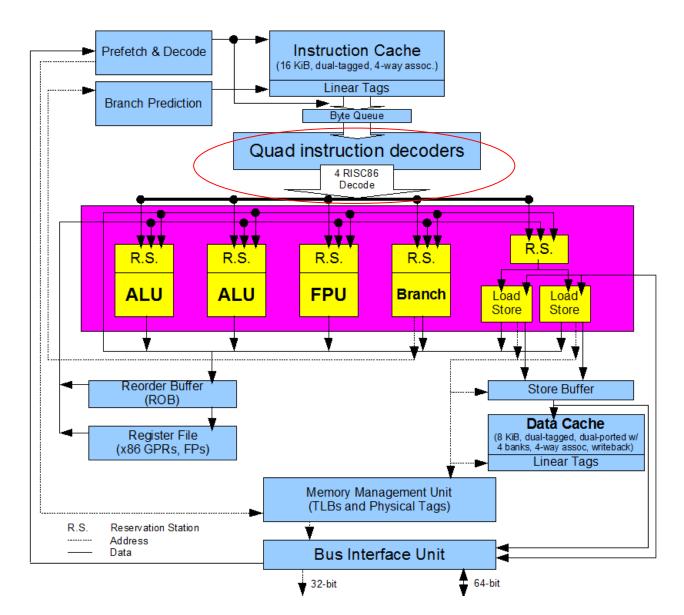

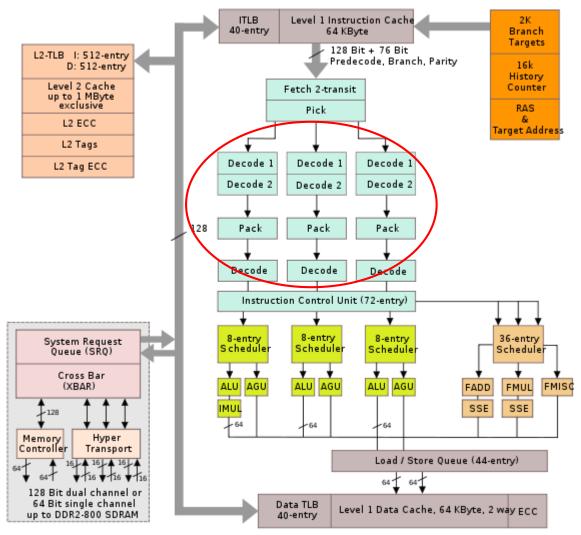

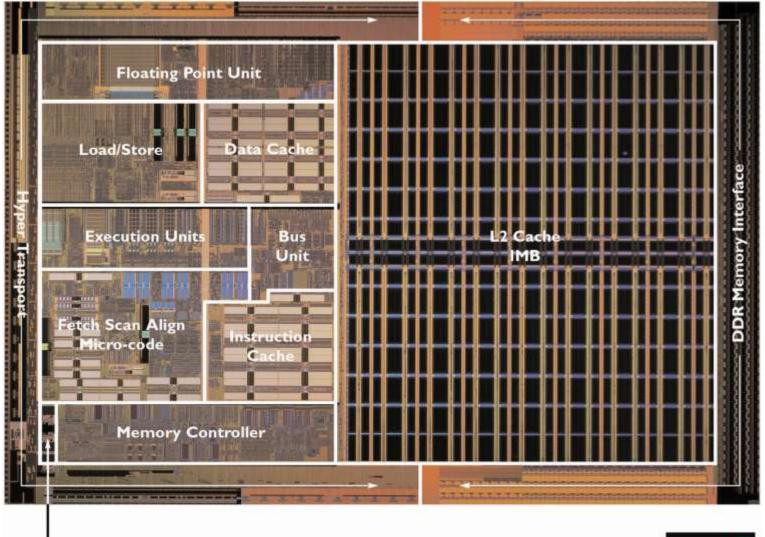

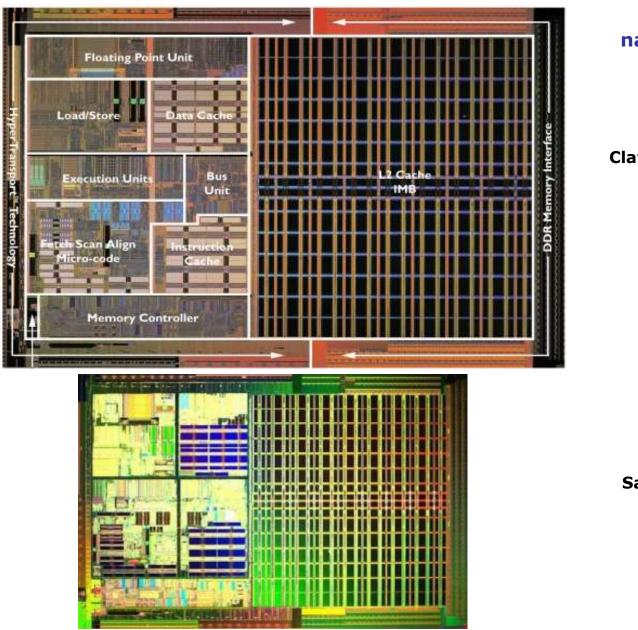

#### Microarchitecture of AMD's 2. generation superscalar K5 [9]

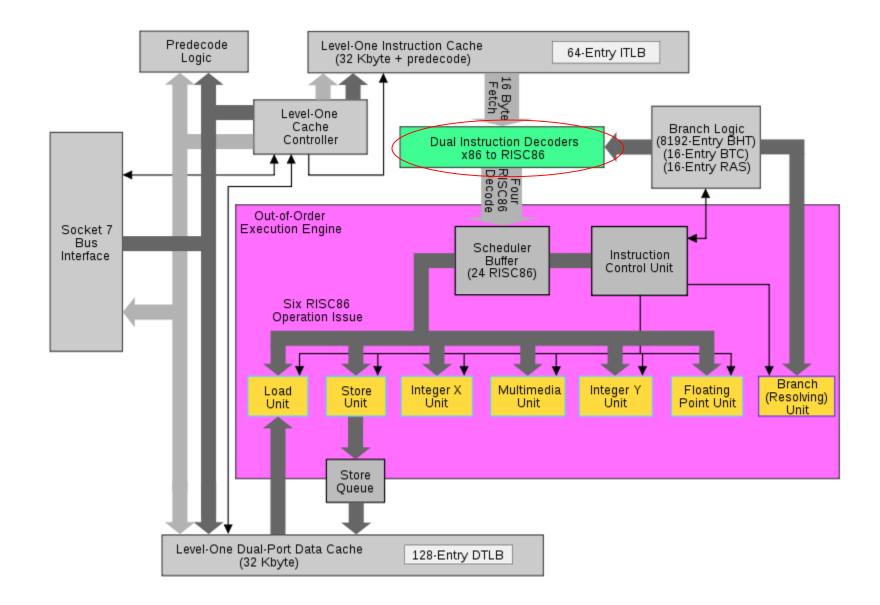

#### Microarchitecture of AMD's 2.5 generation superscalar K6 (NexGen design) [10]

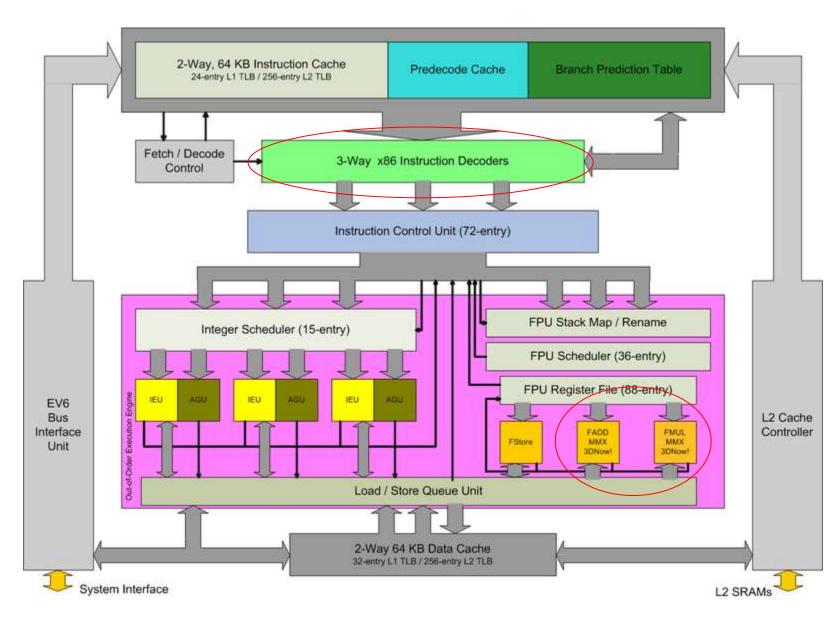

#### Microarchitecture of AMD's 3. generation superscalar K7 (Athlon) [12]

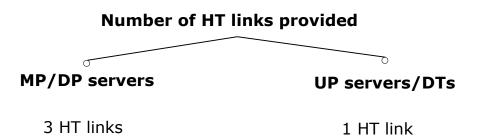

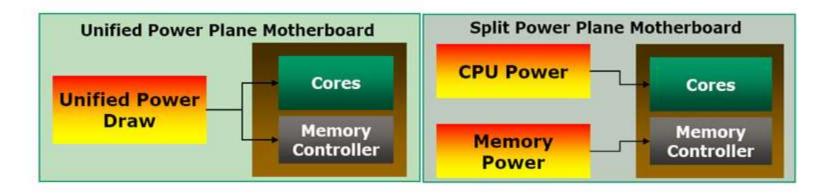

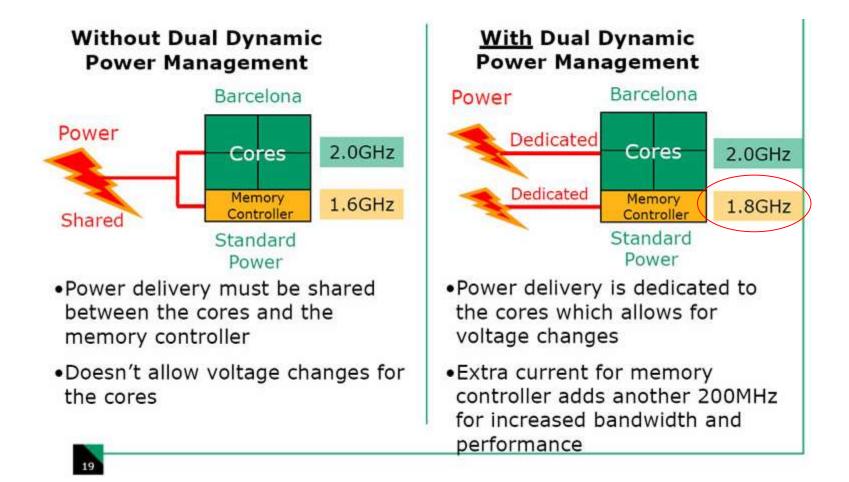

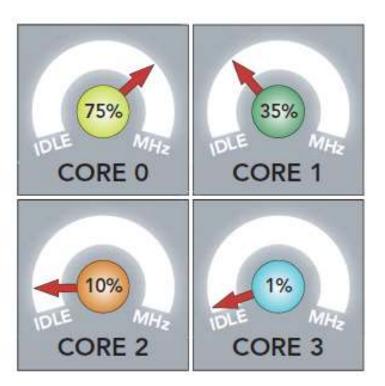

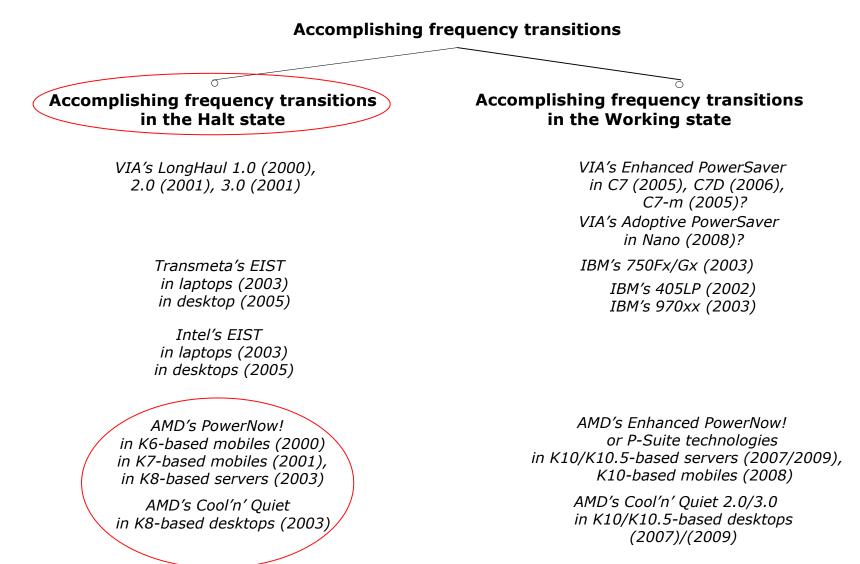

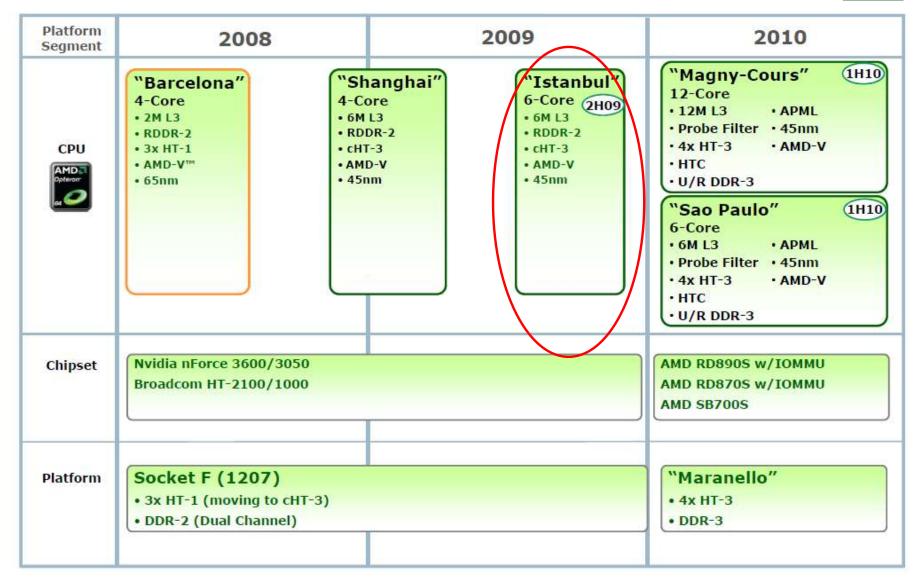

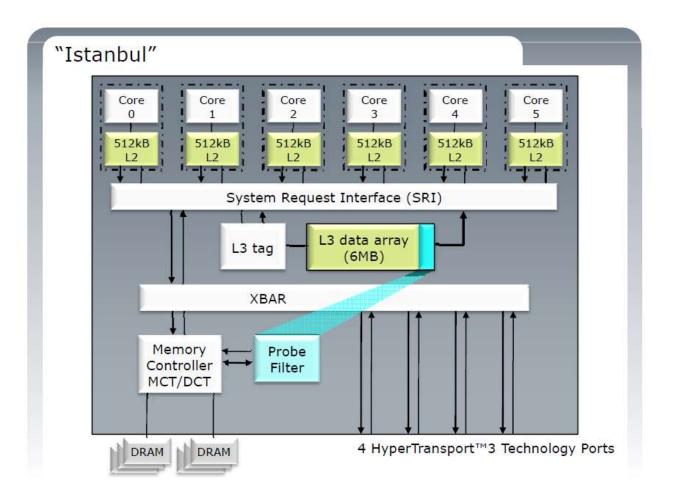

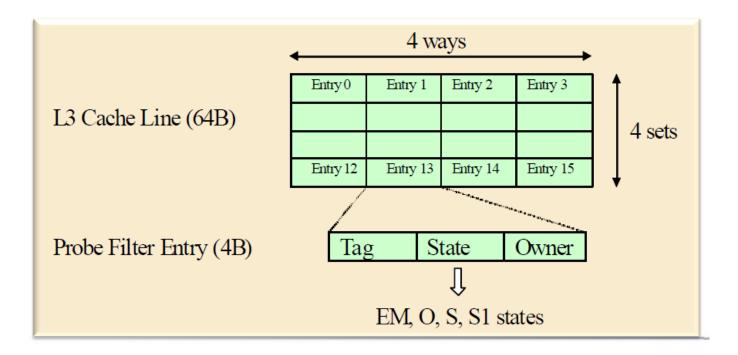

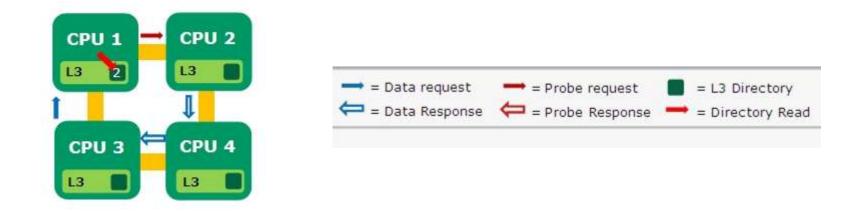

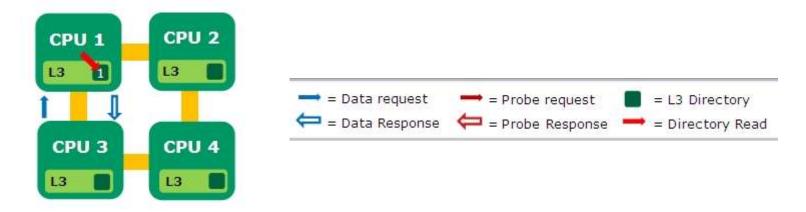

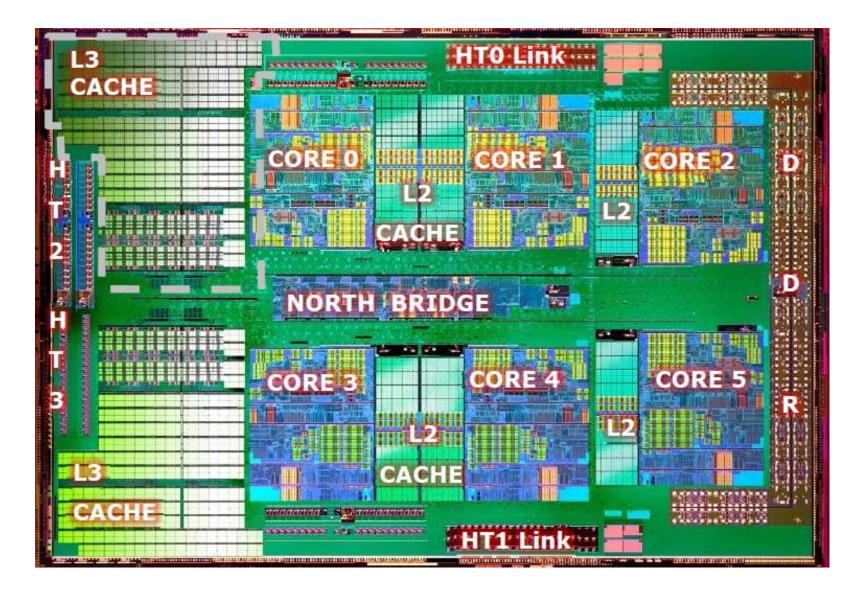

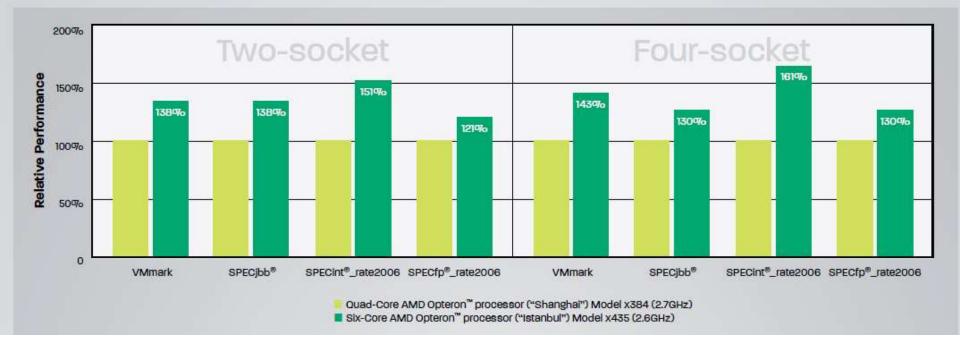

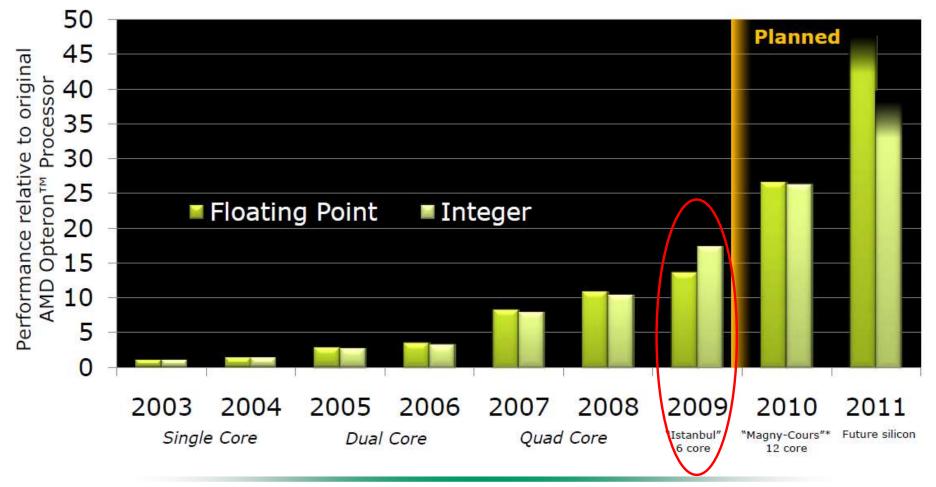

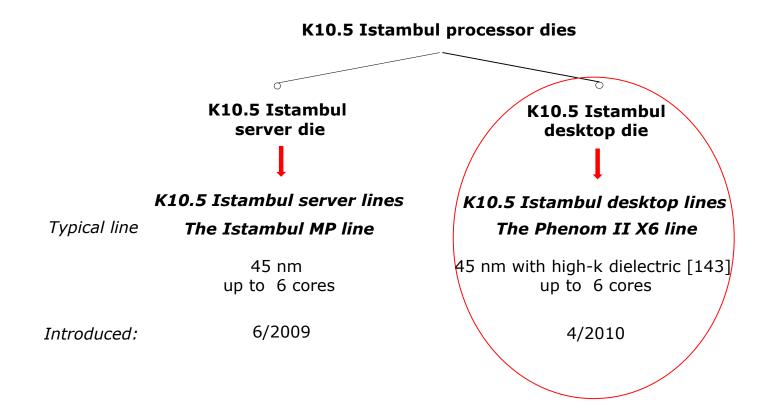

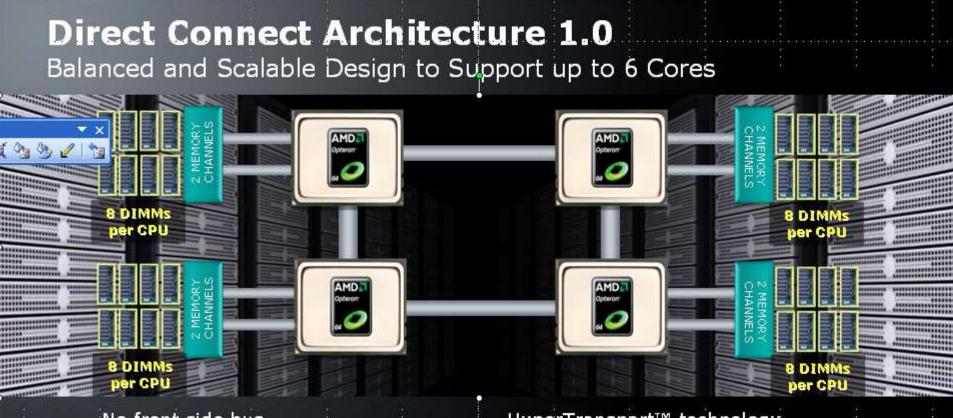

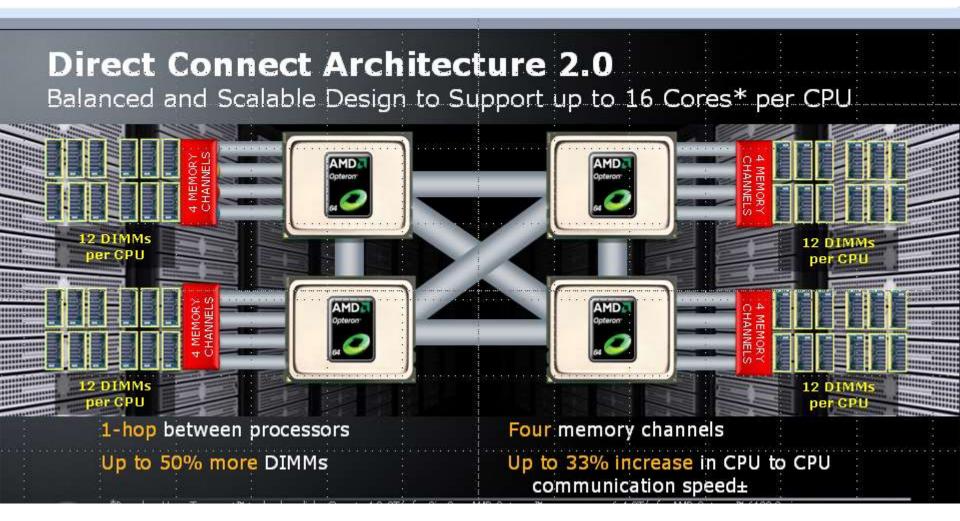

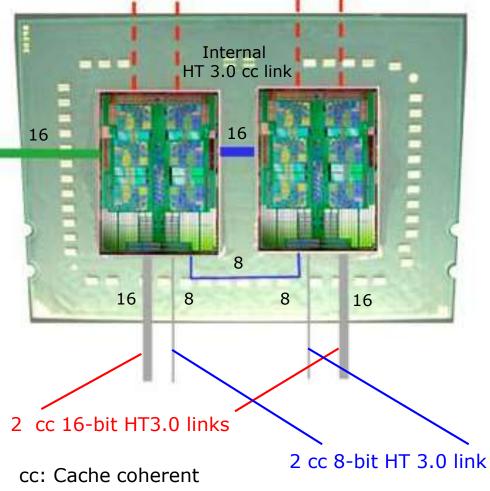

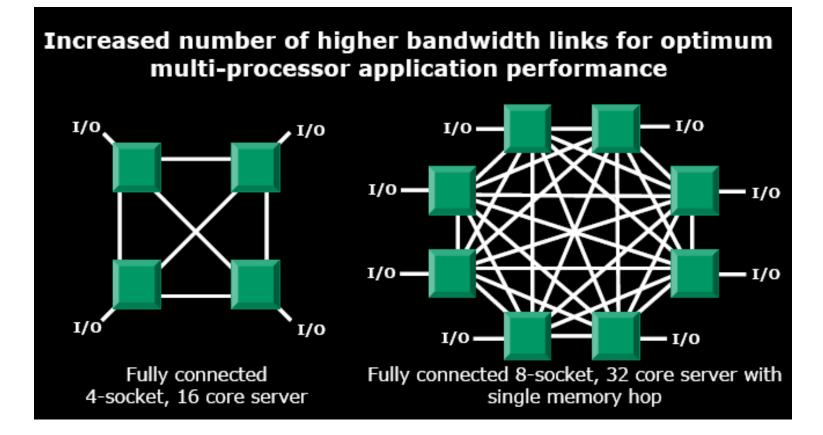

# **Overview and major innovations in AMD's K7 (Athlon) families**