# Intel's Core 2 family - TOCK lines Sunny Cove

# Dezső Sima

Vers. 1.0

Januar 2019

# Contents (1)

- 1. Introduction

- 2. The Core 2 line

- 3. The Nehalem line

- 4. The Sandy Bridge line

- 5. The Haswell line

- 6. The Skylake line

- 7. The Kaby Lake line

- 8. The Kaby Lake Refresh line

- 9. The Coffee Lake line

- 10. The Coffee Lake line Refresh

# Contents (2)

- 11. The Cannon Lake line (outlook)

- 12. Sunny Cove

- 13. References

# 12. Sunny Cove

- 12.1 Introduction to the Sunny Cove

- 12.2 Major enhancements of the Sunny Cove

12.1 Introduction to the Sunny Cove

## 12.1 Introduction to the Sunny Cove [296]

- Announced in 12/2018 at Intel's Architecture Day, to be launched in 2019.

- Manufactured on Intel's 10 nm technology.

- Presumably, the Sunny Cove cores paired with Gen11 graphics will yield the Ice Lake processor.

- Sunny Cove cores offer increased single-threaded performance, new instructions, and 'improved scalability

12.1 Introduction to the Sunny Cove (2)

Intel's CPU roadmap 2019 – 2022 [297]

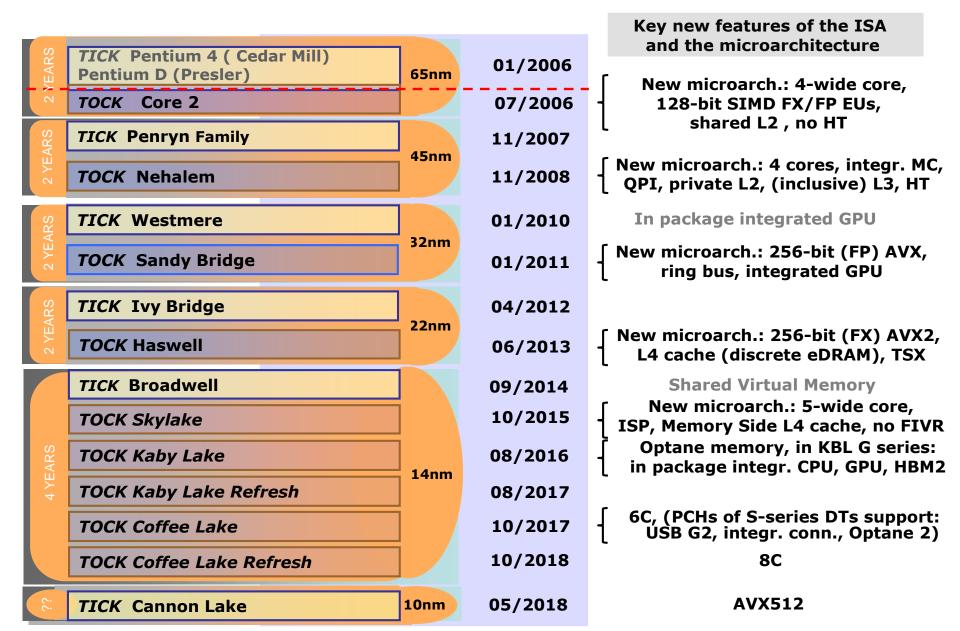

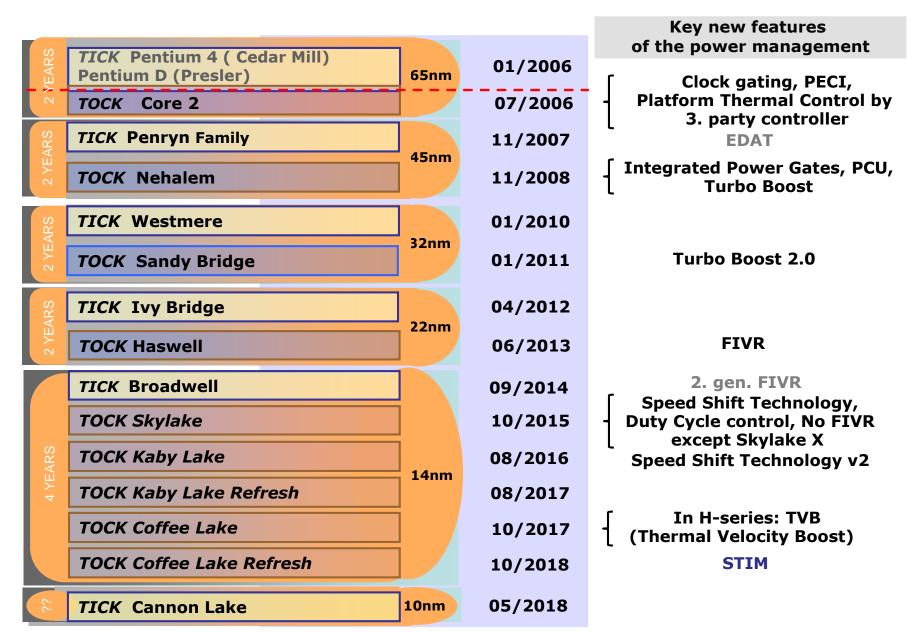

## Evolution of Intel's manufacturing technology [296]

| Intel Core Microarchitecture Roadmap |                   |             |                                                                                                   |  |  |

|--------------------------------------|-------------------|-------------|---------------------------------------------------------------------------------------------------|--|--|

| Core Name                            | Year Process Node |             | Improvements                                                                                      |  |  |

| Skylake                              | 2015              | 14 nm       | Single Threaded Performance<br>Lower Power<br>Other Optimizations                                 |  |  |

| Kaby Lake                            | 2016              | 14 nm+      | Frequency                                                                                         |  |  |

| Coffee Lake                          | 2017              | 14 nm++     | Frequency                                                                                         |  |  |

| Coffee Refresh                       | 2018              | 14 nm++     | Frequency                                                                                         |  |  |

| Sunny Cove                           | 2019              | 10 nm       | Single Threaded Performance<br>New Instructions<br>Improved Scalability                           |  |  |

| Willow Cove                          | 2020 ?            | 10 nm ?     | Cache Redesign<br>New Transistor Optimization<br>Security Features                                |  |  |

| Golden Cove                          | 2021 ?            | 7 / 10 nm ? | Single Threaded Performance<br>AI Performance<br>Networking / 5G Performance<br>Security Features |  |  |

## The core generations -1

| 1. gen.                              |                                   |                                           |                                          | 2. gen.                                       | 3. gen.                                                                                                                                                                                    | 4. gen.                                | 5. gen.                                   |  |  |

|--------------------------------------|-----------------------------------|-------------------------------------------|------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------|--|--|

| Core 2<br>New<br>Microarch.<br>65 nm | Penryn<br>New<br>Process<br>45 nm | Nehalem<br>New<br>Microarch.<br>45 nm     | West-<br>mere<br>New<br>Process<br>32 nm | Sandy<br>Bridge<br>New<br>Microarch.<br>32 nm | Ivy<br>Bridge<br>New<br>Process<br>22 nm                                                                                                                                                   | Haswell<br>New<br>Microarchi.<br>22 nm | Broad-<br>well<br>New<br>Process<br>14 nm |  |  |

| тоск                                 | ТІСК                              | тоск                                      | ТІСК                                     | тоск                                          | тіск                                                                                                                                                                                       | тоск                                   | ТІСК                                      |  |  |

| (2006)                               | (2007)                            | (2008)                                    | (2010)                                   | (2011)                                        | (2012)                                                                                                                                                                                     | (2013)                                 | (2014)                                    |  |  |

| 6. gen.                              | 7. gen.                           | 8. gen. <sup>1</sup> 9. gen.              |                                          | fc                                            | <ul> <li><sup>1</sup>Astonishingly, the 8th generation encompasses<br/>four processor lines, as follows:</li> <li>Kaby Lake Refresh</li> <li>Kaby Lake G with AMD Vega graphics</li> </ul> |                                        |                                           |  |  |

| Skylake                              | Kaby Lake                         | Kaby Lake R Coffee<br>KL G-series Lake R  |                                          | •                                             |                                                                                                                                                                                            |                                        |                                           |  |  |

| New<br>Microarch.                    | New<br>Microarch.                 | KL G-series<br>Coffee Lake<br>Cannon Lake | New                                      |                                               | <ul> <li>Coffee Lake (all 14 nm) and the</li> <li>10 nm Cannon Lake designs [218].</li> </ul>                                                                                              |                                        |                                           |  |  |

| 14 nm                                | 14 nm                             | 14/10 nm                                  | 14 nm                                    |                                               |                                                                                                                                                                                            |                                        |                                           |  |  |

| тоск                                 | тоск                              | тоск                                      | тоск                                     |                                               |                                                                                                                                                                                            |                                        |                                           |  |  |

| (2015)                               | (2016)                            | (2017/18)                                 | (2018)                                   | R:                                            | Refresh                                                                                                                                                                                    |                                        |                                           |  |  |

#### The Core generations -2 (based on [3])

#### The Core generations (based on [3])

# 12.2 Major enhancements of the Sunny Cove

## 12.2 Major enhancements of the Sunny Cove Two main directions of increasing processor performance [296]

# **CORE STRATEGY**

# THE FOUNDATION FOR COMPUTE SOLUTIONS FROM PCS TO DATA CENTER AND MORE

# **GENERAL PURPOSE PERFORMANCE**

#### What:

Microarchitecture Enhancements to Improve Performance and Efficiency Across a Broad Set of Applications

#### How:

Deeper Wider Smarter

# **SPECIAL PURPOSE PERFORMANCE**

What:

Architecture Extensions Targeted at Specific Use Cases and Algorithms Building Upon the Microarchitecture

#### How:

1011291

ISA (New Instructions) Software Enabling (Compilers, Libraries)

Intel<sup>®</sup> Confidential, Under embargo

https://ww.anandtech.com/print/13699/intel-architecture-day-2018-core-future-hybrid-x86

12.2.1 Microarchitecture enhancements to improve performance and efficiency across a broad range of applications in the Sunny Cove -1

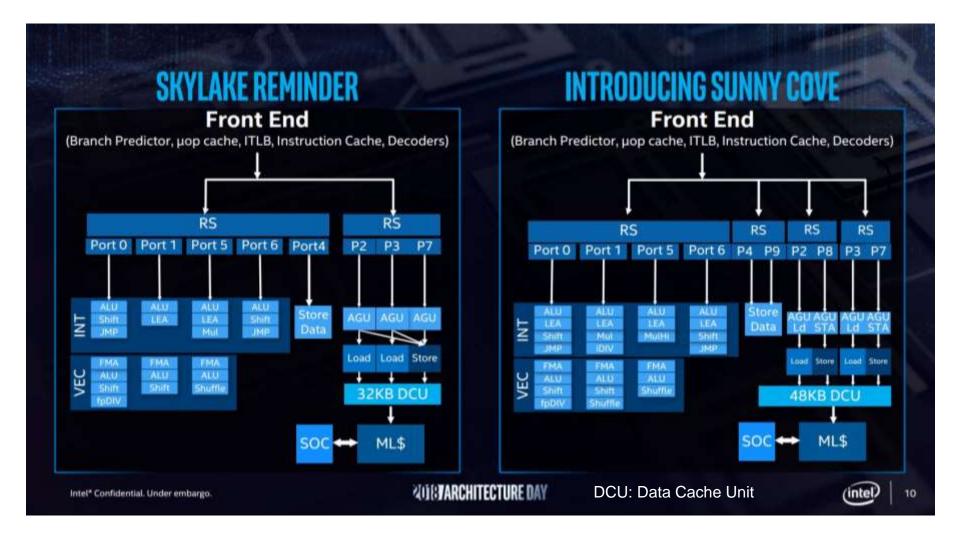

Overview – Contrasting the back-ends of Skylake and Sunny Cove [297 ]-1

### Overview – Contrasting the back-ends of Skylake and Sunny Cove -2

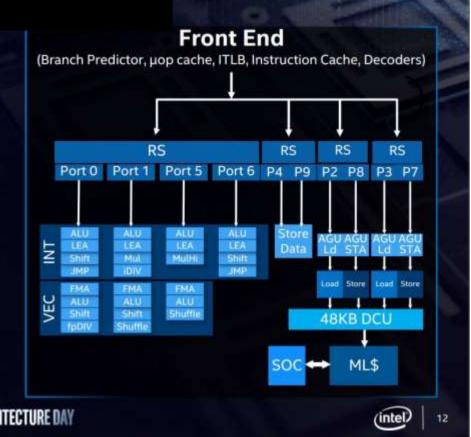

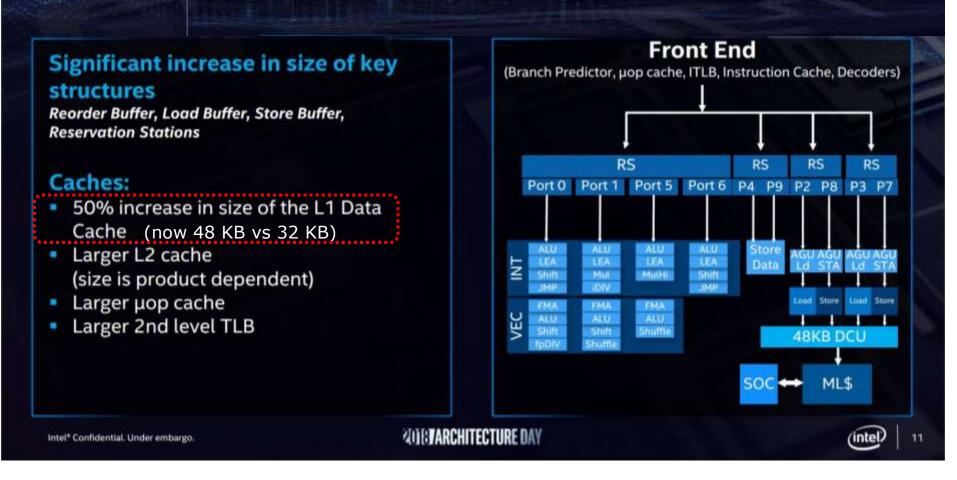

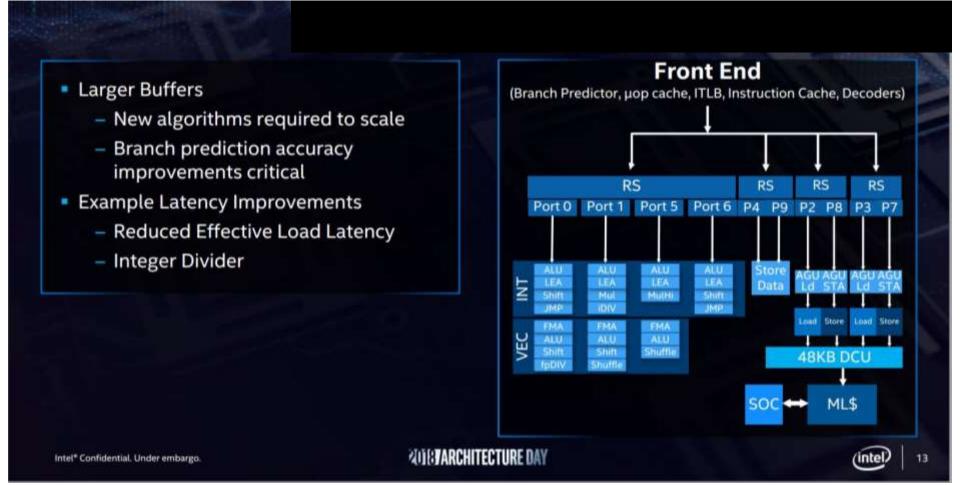

Note that Sunny Cove has 10 ports for issuing instructions (up from 8) implemented in the Skylake.

#### 12.2 Major enhancements of the Sunny Cove (4)

Microarchitecture enhancements to improve performance and efficiency across a broad range of applications in the Sunny Cove -2

Main areas of enhancing the microarchitecture

- a) wider FX/FP/SIMD and load/store execution (executing more instructions per clock),

- b) deeper key structures, including caches (providing more parallelism per clock cycle) and

- c) smarter units (leading to processing more instructions or data)

12.2 Major enhancements of the Sunny Cove (5)

a) Wider FX/FP/SIMD and load/store execution (executing more instructions per clock)

#### 12.2 Major enhancements of the Sunny Cove (6)

### a1) Wider FX and FP/SIMD execution (over the ports 0, 1, 5, 6) [296]

| Back-End Execution Resources |         |       |      |        |            |     |         |         |

|------------------------------|---------|-------|------|--------|------------|-----|---------|---------|

|                              | Skylake |       | Port |        | Sunny Cove |     |         |         |

|                              |         |       |      | Intege | r          |     |         |         |

|                              | JMP     | Shift | ALU  | 0      | ALU        | LEA | Shift   | JMP     |

|                              |         | LEA   | ALU  | 1      | ALU        | LEA | Mul     | iDIV    |

|                              | Mul     | LEA   | ALU  | 5      | ALU        | LEA | MulHi   |         |

|                              | JMP     | Shift | ALU  | 6      | ALU        | LEA | Shift   | JMP     |

| Vector / FP                  |         |       |      |        |            |     |         |         |

| fpDIV                        | Shift   | ALU   | FMA  | 0      | FMA        | ALU | Shift   | fpDIV   |

|                              | Shift   | ALU   | FMA  | 1      | FMA        | ALU | Shift   | Shuffle |

|                              | Shuffle | ALU   | FMA  | 5      | FMA        | ALU | Shuffle |         |

https://www.anandtech.com/print/13699/intel-architecture-day-2018-core-future-hybrid-x86

# a2) Wider load/store execution (over the ports 2, 3, 4, 7, 8, 9) [297] -1

- 4→5 wide allocation

- 8→10 Execution Ports

- 2x L1 Store Bandwidth

- $3 \rightarrow 4$  AGUs

- $1 \rightarrow 2$  Store Data

- Greater capabilities per execution port (ex. SIMD shuffle, LEA)

**2018 ARCHITECTURE DAY**

#### Wider load/store execution (over the ports 2, 3, 4, 7, 8, 9) [296] -2

Compared with Skylake, Sunny Cove will be capable of issuing dual loads and dual stores per cycle, rather than dual loads and a single store per cycle, as in the Skylake.

#### Wider load/store execution (over the ports 2, 3, 4, 7, 8, 9) [296] -2

Compared with Skylake, Sunny Cove will be capable of issuing dual loads and dual stores per cycle, rather than dual loads and a single store per cycle, as in the Skylake.

#### 12.2 Major enhancements of the Sunny Cove (10)

b) Deeper key structures, including caches (providing more parallelism per clock cycle) [297]

#### 12.2 Major enhancements of the Sunny Cove (11)

# c) Smarter units (leading to processing more instructions or data) [297] -1

### c) Smarter units (leading to processing more instructions or data) -2

In this respect Intel improved branch prediction accuracy, with additional latency improvements, like load latency and a implemented a new faster integer divider unit.

#### 12.2 Major enhancements of the Sunny Cove (13)

13.2.2 Architecture extensions targeting specific use cases and algorithms, building upon the microarchitecture [296], [297]

In addition to the microarchitecture enhancements Sunny Cove introduces the following architecture extensions:

- new instructions to speed up special fields of interest (see subsequently),

- 57 bits linear address space,

- 52-bits physical address space, allowing to address 4 PetaB per socket,

- five levels of paging tables, up from four, and

- new security modes, including User Mode Instruction Prevention, that forbids (if enabled) the execution of certain instructions if the Current Privilege Level (CPL) is greater than 0.

Then user space applications can no longer access system-wide settings, such as the global and local descriptor tables, the task register and the interrupt descriptor table. 12.2 Major enhancements of the Sunny Cove ()

Special areas of interest for improving performance [296]

| SUNNY COVE: SPECIA                                                                                                           | ALIZED PERFORMANCE                                                                                                                         |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| EXAMPLE AREAS OF INTEREST<br>Al/Machine Learning<br>Cryptography C<br>Compression/Decompression<br>Communications/Networking | <ul> <li>Big-Number Arithmetic (IFMA)</li> <li>Vector AES</li> <li>Vector Carryless Multiply</li> <li>Galois Field</li> <li>SHA</li> </ul> |  |

| General SIMD/Vector Processing<br>Special SIMD/Vector Processing<br>Multi-Threaded & Multiple Agent Processing               | IFMA: Integer FMA                                                                                                                          |  |

2018VARCHITERTURE D